# A FRAMEWORK FOR USING THE PENTIUM'S PERFORMANCE MONITORING HARDWARE

#### BY

# KEVIN DAVID SAFFORD

B.S., University of Illinois, 1995

# **THESIS**

Submitted in partial fulfillment of the requirements for the degree of Master of Science in Electrical Engineering in the Graduate College of the University of Illinois at Urbana-Champaign, 1997

Urbana, Illinois

# **ACKNOWLEDGMENTS**

My advisor, Professor Wen-Mei Hwu, has been wonderful throughout my career. His enthusiasm for teaching and his passion for research were my main inspiration for going into computer architecture. I thank him for giving me the opportunity to work with a wonderful group.

I wish to thank the entire IMPACT research group for providing an excellent infrastructure with which to do this research. In particular, Brian Dietrich served as my mentor throughout graduate school, helping me every step of the way. John Gyllenhaal and Teresa Johnson have provided many ideas on how this software will be used. Matt Merten taught me many aspects about x86 code and served as a sounding board for many of my ideas. He also helped greatly in debugging this software.

Finally, I wish to thank my parents for their love and support through six years of university study. Without them, none of this would have been possible.

# TABLE OF CONTENTS

|    |      | Page                                             |

|----|------|--------------------------------------------------|

| 1. | INT  | RODUCTION1                                       |

|    | 1.1  | Overview                                         |

|    | 1.2  | Motivation2                                      |

|    | 1.3  | Related Work3                                    |

| 2. | DEN  | TIUM PERFORMANCE MONITORING COUNTERS5            |

| ۷. | 2.1  | Overview5                                        |

|    | 2.2  | Model Specific Registers (MSRs)                  |

|    | 2.3  | Performance Monitoring Features of the MSRs      |

|    | 2.3  | 2.3.1 Time Stamp Counter (TSC)                   |

|    |      | 2.3.2 Event counters                             |

|    |      | 2.3.3 Control and Event Select Register (CESR) 7 |

|    | 2.4] | Events9                                          |

| 2  | DEI  | MOE DRIVER AND ADDADA                            |

| 3. |      | /ICE DRIVER AND LIBRARY                          |

|    | 3.1  | Overview                                         |

|    | 3.2  | Linux Device Driver Module                       |

|    |      | 3.2.1 Access methods                             |

|    |      | 3.2.2 Device driver approach                     |

|    | 2.2  | 3.2.3 P5mon device driver                        |

|    | 3.3  | Library Routines                                 |

|    |      | 3.3.1 Enumerated types                           |

|    |      | 3.3.2 Structures                                 |

|    |      | 3.3.3 Functions                                  |

|    |      | 3.3.4 Example p5mon library routines usage       |

|    | 3.4  | Summary                                          |

| 4. | RUN  | N_P5MON25                                        |

|    | 4.1  | Motivation                                       |

|    | 4.2  | Overview of Run_p5mon25                          |

|    |      | 4.2.1 Unmodified executable                      |

|    |      | 4.2.2 Modified executable                        |

|    | 4.3  | Configuring Run_p5mon28                          |

|    |      | 4.3.1 IMPACT parameters facility                 |

|    |      | 4.3.2 Basic configuration options                |

|    |      | 4.3.3 Advanced configuration options             |

|    | 4.4  | Results                                          |

|    |      | 4.4.1 Run_p5mon statistics                       |

|    |      | 4.4.2 Output report format                       |

|    |      | 4.4.3 Output file format                         |

|    | 4.5  | Interpreting the Results                         |

| 5. | USI | NG RUN_P5MON                                         | 41 |

|----|-----|------------------------------------------------------|----|

|    | 5.1 | Overview                                             | 41 |

|    | 5.2 | Basic Usage of an Unmodified Executable              | 41 |

|    | 5.3 | Basic Usage of a Modified Executable                 |    |

|    | 5.4 | Techniques for Using Run_p5mon                       | 45 |

|    |     | 5.4.1 One assembly region covering the whole program | 45 |

|    |     | 5.4.2 Defining a region around a loop                | 45 |

|    |     | 5.4.3 Nonoverlapping regions                         | 46 |

|    | 5.5 | Synthetic Benchmarks                                 | 47 |

|    |     | 5.5.1 Program 1                                      | 48 |

|    |     | 5.5.2 Program 2                                      | 50 |

|    | 5.6 | Case Study: Word Count                               | 51 |

|    | 5.7 | Case Study: Compress                                 |    |

| 6. | SUN | /IMARY                                               | 55 |

|    | APF | PENDIX A. DESCRIPTION OF PERFORMANCE MONITORING      |    |

|    |     | COUNTER EVENTS                                       | 56 |

|    | APF | PENDIX B. INSTALLING P5MON SOFTWARE                  | 64 |

|    |     | B.1 Installing P5mon Device Driver                   | 64 |

|    |     | B.2 Installing P5mon Library and Run_p5mon           | 67 |

|    | APF | PENDIX C. SUMMARY OF RUN_P5MON PARAMETERS            | 69 |

|    | APF | PENDIX D. PMC ACCESS OVERHEAD                        | 72 |

|    | REF | FERENCES                                             | 76 |

# LIST OF TABLES

| Table | Table                                         |    |  |

|-------|-----------------------------------------------|----|--|

| 2.1   | Pentium performance monitoring MSRs           | 6  |  |

| 2.2.  | Counter modes                                 |    |  |

| 2.3.  | Performance monitoring events                 | 10 |  |

| 3.1.  | Counter initialization control                | 16 |  |

| 3.2.  | Enumerated event names                        | 19 |  |

| 3.3.  | Counter control                               | 20 |  |

| 3.4.  | Counter initialization control                | 21 |  |

| 3.5.  |                                               |    |  |

| 5.1.  | Results for sample unmodified program         | 42 |  |

| 5.2.  | Results for sample modified program           | 44 |  |

| 5.3.  | Program 1 results                             | 49 |  |

| 5.4.  | Program 2 results                             | 51 |  |

| 5.5.  | Parameters for cache and memory configuration | 52 |  |

| 5.6.  | Simulated versus PMC results for wc           |    |  |

| 5.7.  | Results for wc inner loop                     | 53 |  |

| 5.8.  | Results for <i>compress</i>                   | 54 |  |

| C.1   | Run_p5mon parameters                          | 69 |  |

| D.1.  | PMC overhead for an unmodified executable     | 73 |  |

| D.2.  | PMC access overhead using assembly regions    | 75 |  |

# LIST OF FIGURES

| Figur | re                                                                               | Page |

|-------|----------------------------------------------------------------------------------|------|

| 2.1.  | Control and Event Select Register layout                                         | 8    |

| 3.1.  | Software abstraction levels.                                                     | .11  |

| 3.2.  | P5mon device write buffer                                                        | .15  |

| 3.3.  | P5mon device read buffer                                                         | .16  |

| 3.4.  | Example C program using p5mon device directly                                    | .18  |

| 3.5.  | Libp5mon function prototypes                                                     | .22  |

| 3.6.  | Example C program using p5mon library routines                                   | .24  |

| 4.1.  | Run_p5mon algorithm                                                              | .26  |

| 4.2.  | Sample header from run_p5mon                                                     | .33  |

| 4.3.  | Sample results section from run_p5mon                                            | .34  |

| 4.4.  | Sample results section containing results from each repetition                   | .34  |

| 4.5.  | Sample results with multiple regions                                             | .35  |

| 4.6.  | Sample results with multiple regions, displaying the results for each repetition | .36  |

| 4.7.  | Sample output file containing all results with no regions                        | .37  |

| 4.8.  | Sample output file with no regions, and summary information only                 | .37  |

| 4.9.  | Sample output file with multiple regions.                                        | .38  |

| 5.1.  | Sample hello.c program                                                           | .41  |

| 5.2.  | Commands executed to gather data on unmodified program                           | .42  |

| 5.3.  | Optimized hello.c assembly code                                                  | .43  |

| 5.4.  | Modified hello.c assembly code                                                   | .44  |

| 5.5.  | Commands executed to gather data on modified program                             | .44  |

| 5.6.  | Using one region around entire program                                           | .46  |

| 5.7.  | Defining region around a loop                                                    |      |

| 5.8.  | Using nonoverlapping regions in a program.                                       | .48  |

| 5.9.  | Program 1 C code                                                                 | .49  |

| 5.10. | Program 1 modified assembly code                                                 | .49  |

| 5.11. | Program 2 assembly code                                                          | .50  |

|       | Output of p5mon device test program                                              |      |

| C.1.  | Sample p5mon PARMS file                                                          | .71  |

# 1. INTRODUCTION

#### 1.1 Overview

Analyzing a program's run-time behavior on a real system is a difficult challenge. Basic UNIX tools only provide data such as execution time. Conventional profilers, such as *gprof*, only give information on how many times a function might be called, or how long a function might take to execute. Neither of these tools, however, provides insight as to why a particular section of code takes as long to execute as it does. Modern processors contain multiple execution units, high-speed caches, and other performance-enhancing features. Obtaining the greatest possible performance requires following a complicated set of rules during compilation. In an effort to characterize how real code runs on a real processor, special hardware can be added to monitor performance. In the case of Intel's Pentium processor, the architects added two performance monitoring counters that can count 38 different events related to processor performance. The designers provided an interface to allow users to access these counters and measure various aspects of system performance.

This thesis serves several purposes. First, it is designed to give some background information about the monitoring hardware found in the Pentium. Second, it is a source of documentation for both low-level and high-level software developed as part of this thesis work to provide access to these counters. Finally, it offers insight on how to use this hardware and software to obtain meaningful results. The rest of this thesis is organized as follows: Chapter 1 provides motivation for this work, as well as describing some related work. Chapter 2 then describes the performance monitoring hardware found in the Pentium processor. Chapter 3 describes the low-level software and library routines developed to provide user-level access to the

hardware. Chapter 4 documents a high-level program, run\_p5mon, which gathers data on program execution. Chapter 5 provides some examples of using this software to monitor various programs. Finally, Chapter 6 discusses conclusions as well as possible future work.

#### 1.2 Motivation

There are several reasons for using performance monitoring hardware to analyze code behavior. Traditional benchmarking has only looked at real execution time of entire programs on a particular system. Little additional detail has been available. To gather finer-grain information, some sort of simulator or emulator must be used.

Simulators, while useful to evaluate new architectural features to obtain a rough idea of potential benefits, have several drawbacks when used to analyze code on an existing system. The first is the execution speed of a simulator. At best, it is several times slower than the real hardware. On average, the cycle-accurate simulator used by the IMPACT group is about 1000 times slower if all dynamic program instructions are simulated. This can be reduced to about a 20 times slowdown if sampling is used. Second, the accuracy of a simulator is directly dependent on the accuracy of the processor and memory models. Finally, while some simulators and emulators, such as Stanford's SimOS [2], can easily measure operating system and library code, it is difficult for trace-driven simulators to measure this code because of the difficulty in obtaining traces. The effects of library and operating system code can be far-reaching. First, the simulator will generally generate optimistic results, since the actual program with library and system calls will execute more instructions. These extra instructions can displace other program instructions and data in both the instruction and data caches, displace branches in the branch target buffer (BTB), cause more pipeline flushes, and have other negative effects on the program's execution time.

To overcome the problems of a simulator, it is desirable to analyze code behavior on a real system in order to include both library and operating system code when running a particular program. In addition to gathering data on all executing code, hardware monitors give the added benefit of helping verify a simulator's accuracy by allowing comparisons of simulated results with the actual measured results. In a benchmark that has few library calls, the simulator results should be very close to the measured results. If they are not, then there is a possibility that something is not being modeled correctly within the simulator.

The other benefit of using the Pentium hardware counters is to analyze compiler-generated x86 code. Through analysis, we can determine what portions of the code lose performance by measuring different events on small regions of code. Then, the reasons for the performance loss — be they stalls due to cache misses, cache bank conflicts, address generation interlocks, or other factors — can be identified and addressed. In general, this type of analysis can be useful to any software or compiler writer trying to tune code to run on that particular processor.

#### 1.3 Related Work

Little is published concerning hardware performance monitors. When Intel released the Pentium processor, they merely mentioned that there were several performance monitoring counters in the Pentium, but did not disclose how to access them or what they measured. However, Terje Mathisen reverse-engineered this information and published the results in *BYTE Magazine* [1]. Following this, Intel released the Pentium's performance monitoring hardware information. They also disclosed this information for both the Pentium Pro and the Pentium with MMX processors when they were released.

Two papers have been published concerning the use of the Pentium's performance monitoring counters. Chen et al, used the Pentium's hardware counters to compare the performance of the Microsoft Windows 3.1, Microsoft Windows 95, and NetBSD operating systems [3], [4]. Intel itself recently published a paper comparing the performance of the Pentium and Pentium Pro running various benchmarks [5]. These comparisons contained information that was gathered from the hardware monitoring counters on both processors. However, no information was given on how they actually gathered the data.

Presumably, other processors contain this type of hardware, as monitoring counters are an excellent source of information for the designers of the processor in determining how their processor will behave on real code. This hardware is also helpful for the company to provide code generation guidelines for external compiler writers.

# 2. PENTIUM PERFORMANCE MONITORING COUNTERS

#### 2.1 Overview

In order to monitor the performance of the Pentium, the architects added several registers and counters to the Pentium architecture. The performance monitoring registers in the Pentium processor are a subset of the Model Specific Registers (MSRs). To provide access, two instructions, RDMSR (Read Model Specific Register) and WRMSR (Write Model Specific Register), were added to the Pentium's instruction set. This chapter describes the Pentium's MSRs. Section 2.2 first describes the function of the MSRs, and Section 2.3 details their performance monitoring features. Finally, Section 2.4 describes the various events that may be counted using the MSRs. All of this information concerning the MSRs comes from the *Pentium Processor Family Developer's Manual, Volume 3: Architecture and Programming Manual* [6].

# 2.2 Model Specific Registers (MSRs)

The Pentium Processor includes model specific registers to provide access to features that are tied to implementation-dependent aspects of the Pentium. In addition to registers that help test internal chip structures, such as the cache or BTB, the MSRs include performance monitoring counters that allowed the architects and developers to investigate how the Pentium behaves while executing real code. In addition to being useful to the architects and designers, the model specific registers are useful to compiler writers, software developers, and system designers.

In order to access the MSRs, two instructions were added to the Pentium's instruction set, both of which are described in Chapter 25 of the *Pentium Programming Manual* [6]. The RDMSR (Read Model Specific Register) instruction reads one of the model specific registers and returns the value. The value in the ECX register specifies one of the processor's MSRs. The

value of the MSR is copied into the EDX and EAX registers, with EDX containing the high-order 32 bits and EAX the low-order 32 bits. This instruction takes anywhere from 20 to 24 clock cycles to complete. This instruction must be executed from privilege level 0, otherwise a protection fault will occur. No processor flags are affected by this instruction.

Similarly, the WRMSR (Write Model Specific Register) instruction writes one of the model specific registers. The value in the ECX register specifies which one of the 64-bit MSRs to write. The value to be written is specified in the EDX and EAX registers, with EDX containing the high-order 32 bits and EAX the low-order 32 bits of the value. This instruction takes anywhere from 30 to 45 clock cycles to complete. It too must be executed from privilege level 0. No processor flags are affected by the WRMSR instruction.

# 2.3 Performance Monitoring Features of the MSRs

Four MSRs are related to performance monitoring in the Pentium. They are summarized in Table 2.1. It is important to note that none of the performance monitoring counters (PMCs) are saved and restored when using the low-level task switch instruction normally executed by the operating system. If the user wishes to have these registers saved and restored, the operating system itself must actually save and restore the MSRs. This is discussed in some detail later.

Table 2.1. Pentium performance monitoring MSRs

| MSR (in hex) | Register Name                |

|--------------|------------------------------|

| 0x10         | Time Stamp Counter           |

| 0x11         | Control and Event Select     |

| 0x12         | Programmable Event Counter 0 |

| 0x13         | Programmable Event Counter 1 |

# 2.3.1 Time Stamp Counter (TSC)

The Time Stamp Counter (TSC) is a dedicated, 64-bit register that is incremented once every clock cycle. A separate instruction, RDTSC (Read Time Stamp Counter) is used to access this counter. The TSC was not used during the course of this work.

#### 2.3.2 Event counters

There are two 40-bit programmable event counters (CNT0 and CNT1) that may be programmed to count any event from a predetermined set, as described in Section 2.4. When switching to a new event, the user must clear or preset the counters using the WRMSR instruction. Each of these counters can also signal the occurrence of an event on an external pin to allow system designers to perform hardware monitoring of the processor.

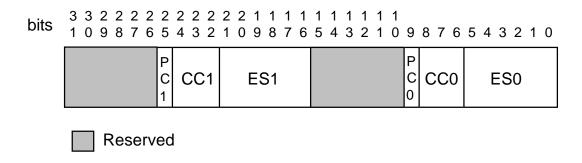

# 2.3.3 Control and Event Select Register (CESR)

The Control and Event Select Register (CESR) is a 32-bit register used to control the two event counters described above. The layout of the CESR is shown in Figure 2.1. Each counter has a 6-bit Event Select (ES) field, 3-bit Counter Control (CC) field, and Pin Control (PC) bit. The shaded areas are reserved and may not be changed by the user. Since it is not possible to selectively write a part of the CESR, the CESR must first be read, the appropriate fields changed, and all 32 bits written back in order to make a configuration change.

# 2.3.3.1 Event select

The six-bit Event Select field controls the events to be counted by each counter. The two events are independent of one another. The individual events that can be counted are described in Section 2.4.

Figure 2.1. Control and Event Select Register layout

#### 2.3.3.2 Counter control

A 3-bit Counter Control field is used to control the operation of the two counters. The counter control determines whether to count the specified event or just clock cycles, as well as what "ring" in which to count the events. The Pentium processor has four rings of operation in order to support varying degrees of protection. Ring 0 (also known as CPL 0) is the most privileged level of operation, typically where the operation system runs. Rings 1 and 2 (CPLs 1 and 2) are additional rings used by the operating system. Finally, Ring 3 (CPL 3) is the level where all user processes run. In addition to counting events, both counters can count just clock cycles, transforming the counter into a time stamp counter.

The three bits of the control field determine what mode each counter is operating in, with each bit in the field controlling one aspect. The highest order bit selects between counting events and counting clock cycles. The middle bit enables counting in Ring 3 (the user level). Finally, the low order bit enables counting when executing in rings 0, 1, or 2 (the operating system, or kernel, level). Using these three bits, eight modes of operation are possible, as summarized in Table 2.2.

Table 2.2. Counter modes

| CC                                | Description                      |  |  |

|-----------------------------------|----------------------------------|--|--|

| 000 disable counter               |                                  |  |  |

| 001                               | count event while CPL=0,1, or 2  |  |  |

| 010                               | count event while CPL=3          |  |  |

| 011 count event regardless of CPL |                                  |  |  |

| 100 disable counter               |                                  |  |  |

| 101                               | count clocks while CPL=0,1, or 2 |  |  |

| 110                               | count clocks while CPL=3         |  |  |

| 111                               | count clocks regardless of CPL   |  |  |

# 2.3.3.3 Pin control

As mentioned before, each counter can control an external pin to signal an event occurrence or counter overflow. For the purposes of this research, these are ignored and set to 0.

#### 2.4 Events

The Pentium can count 38 different events in each of its performance monitoring counters. These events range from data reads and writes, to branches and BTB hits. Each of the events may be classified as either among those that count an *occurrence*, or among those that count a *duration*. An *occurrence* event is counted each time the event takes place. Some events in the Pentium can occur twice in one clock cycle, which causes the counter to be incremented by two. For a *duration* event, the counter counts the total number of clock cycles during which a particular condition is true. The events, including their event code, a brief description, and whether it is an *occurrence* or *duration* event, are summarized in Table 2.3. Each event, or group of events, is described in detail in Appendix A.

Table 2.3. Performance monitoring events

| Encoding (in hex) | Event                                                | Occurrence/<br>Duration |

|-------------------|------------------------------------------------------|-------------------------|

| 0x00              | data read                                            | occurrence              |

| 0x01              | data write                                           | occurrence              |

| 0x28              | data read or write                                   | occurrence              |

| 0x02              | data TLB miss                                        | occurrence              |

| 0x03              | data read miss                                       | occurrence              |

| 0x04              | data write miss                                      | occurrence              |

| 0x29              | data read or write miss                              | occurrence              |

| 0x05              | write (hit) to M or E state lines                    | occurrence              |

| 0x06              | data cache lines written back                        | occurrence              |

| 0x07              | external snoops                                      | occurrence              |

| 0x08              | data cache snoop hits                                | occurrence              |

| 0x09              | memory access in both pipes                          | occurrence              |

| 0x0A              | bank conflicts                                       | occurrence              |

| 0x0B              | misaligned data memory or I/O references             | occurrence              |

| 0x0C              | code read                                            | occurrence              |

| 0x0D              | code TLB miss                                        | occurrence              |

| 0x0E              | code cache miss                                      | occurrence              |

| 0x0F              | any segment register loaded                          | occurrence              |

| 0x12              | branches                                             | occurrence              |

| 0x13              | BTB hits                                             | occurrence              |

| 0x14              | taken branch or BTB hit                              | occurrence              |

| 0x15              | pipeline flushes                                     | occurrence              |

| 0x16              | instructions executed                                | occurrence              |

| 0x17              | instructions executed in the v-pipe                  | occurrence              |

| 0x18              | clocks while a bus cycle is in progress              | duration                |

| 0x19              | number of clocks stalled due to full write buffers   | duration                |

| 0x1A              | pipeline stalled waiting for data memory read        | duration                |

| 0x1B              | stall on write to an E or M state line               | duration                |

| 0x1C              | locked bus cycle                                     | occurrence              |

| 0x1D              | I/O read or write cycle                              | occurrence              |

| 0x1E              | non-cacheable memory reads                           | occurrence              |

| 0x1F              | pipeline stalled due to address generation interlock | duration                |

| 0x22              | floating point operations (FLOPs)                    | occurrence              |

| 0x23              | breakpoint match on DR0 register                     | occurrence              |

| 0x24              | breakpoint match on DR1 register                     | occurrence              |

| 0x25              | breakpoint match on DR2 register                     | occurrence              |

| 0x26              | breakpoint match on DR3 register                     | occurrence              |

| 0x27              | hardware interrupts                                  | occurrence              |

# 3. DEVICE DRIVER AND LIBRARY

# 3.1 Overview

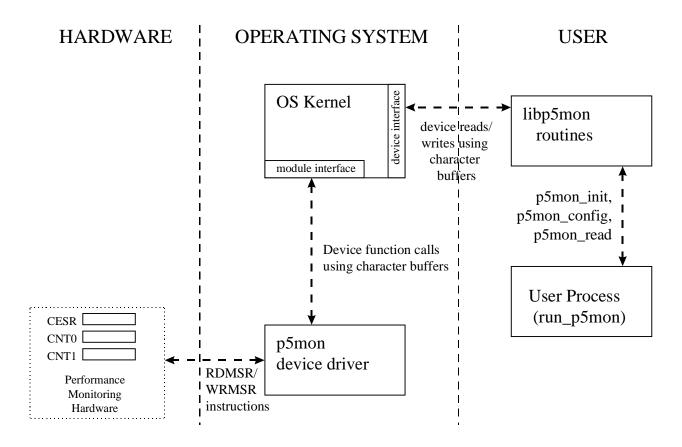

The performance monitoring hardware in the Pentium is useless without some sort of software to configure the counters, then read the values and provide them to the user. Since the PMCs can only be accessed by use of privileged instructions, such software support must be integrated into the operating system itself. However, the operating system interface can be awkward to use, so various levels of abstraction form the software control desired by a user. These levels of abstraction are shown below in Figure 3.1. There are three distinct layers: the hardware itself, the operating system, and the user process.

Figure 3.1. Software abstraction levels

The purpose of this chapter is to provide the reader with insight into how the various counters are controlled by the operating system. Two levels of abstraction, a device driver and a library, form the interface between the user and the hardware. Section 2 describes the device driver itself, which forms the lowest level of software support required in the operating system. Section 3 then describes the high-level library routines that provide an interface to the device driver. The highest level of abstraction depicted in Figure 3.1 is described in Chapter 4.

### 3.2 Linux Device Driver Module

As mentioned in Chapter 2, both the Read Model Specific Register (RDMSR) and Write Model Specific Register (WRMSR) instructions must be executed from a privileged mode. The Intel x86 architecture provides four "rings" of operation, ranging from 0 to 3, with ring 0 being the most privileged level. Generally, the operating system kernel is the only program executing in ring 0. Thus, both the RDMSR and WRMSR instructions must be executed from within the operating system kernel in some fashion. However, in order for the instructions to be useful to the user, there must be some type of interface to allow the user to both read and write the performance monitoring counters.

#### 3.2.1 Access methods

There are two methods of having the operating system kernel provide this type of access to the user. The first method involves using system calls that are built into the kernel itself. In order to add system calls, the code must be compiled directly into the operating system kernel, which involves changing the kernel source code. The second method involves treating the counters as a device in the system. Creating a device driver to act as an intermediary between the

operating system and the hardware allows the user to pass "commands" through the operating system's device interface; this is the approach taken in this thesis work.

# 3.2.2 Device driver approach

There are several advantages to the device driver approach. The first, and perhaps most important, advantage is that no changes to the operating system kernel source code are necessary. In the case of Linux, a widely-distributed "free" UNIX operating system, modifying the kernel source is relatively easy. However, it would be nearly impossible for a commercial UNIX system. Most UNIX operating systems provide some sort of third-party device driver support to allow hardware developers to control their hardware. Under Linux, the device driver is implemented as a "module" that can attach to the kernel. Furthermore, this module is somewhat independent of the operating system kernel. Thus, if support is to be added to another Linux system, the module would be merely copied over and compiled.

Second, it is simple to create new modules that operate in much the same way for the performance counters that are available in the Pentium Pro or the Pentium with MMX technology. Both processors can monitor different events and have slightly different instructions to access the information. Using a device interface, the paradigm for using the counters remains consistent regardless of the platform.

There are two minor disadvantages to using a device driver over system calls. First, since the hardware is considered a device, it is controlled through a rigidly defined interface that ordinary users might find difficult to use when compared to a custom-designed system call interface. A set of higher-level library routines that actually communicate with the device driver overcomes this problem. The second disadvantage is that a device driver might have more overhead than a system call. The operating system has to go through various layers of functions to

get from the device interface to the hardware itself. This second point, as well as overhead in general, is addressed in later chapters.

#### 3.2.3 P5mon device driver

The device driver to control the Pentium's performance monitoring counters is called *p5mon*. The user uses character buffers to send configuration information to write into the MSRs and to read values from the MSRs. Linux provides a common interface to all devices through a set of system calls. During a system call, the operating system relays these buffers to the appropriate function in the p5mon device driver. The device driver itself consists of an initialization function, an open function, a read device function, and a write device function. The device driver itself was written with flexibility and efficiency in mind.

# 3.2.3.1 Opening p5mon

The p5mon device, usually installed as /dev/p5mon, is opened using the open system call [7]. The only important item of note here is that the device does not lock itself to prevent another process from reading or writing the PMCs. This support is needed to allow two processes to use the device at the same time, which is essential for doing some types of measurement. The user on the system must ensure that no other process uses the counters while trying to measure events in a program.

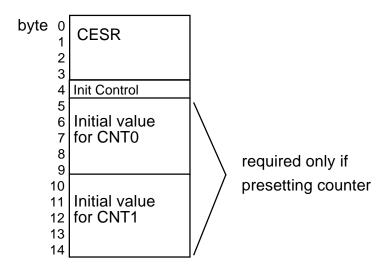

#### 3.2.3.2 Configuring the PMCs

The PMCs are configured through the *write* system call [8]. As mentioned earlier, the configuration information is passed through a character buffer. Note that in the Intel architecture, a character is one byte in length. Three values must be sent via this buffer: a value used to configure the CESR, a flag used to control initialization of the counters, and, optionally, two

40-bit initialization values to write into the PMCs. The format of this character buffer is shown in Figure 3.2. In all cases where a field spans multiple bytes, the field is stored in little endian format, meaning the lowest byte of the field is stored in the first byte of the buffer, the next byte in the second byte of the buffer, and so on.

Figure 3.2. P5mon device write buffer

The user is responsible for setting up the CESR correctly by providing two events and a counter control for each event in the correct positions within the 32-bit CESR word as shown in Figure 2.1 (page 8). However, the user does not have to worry about assigning the reserved positions of the CESR since the device driver will actually first perform a read of the CESR, combine only the unreserved bits with the user-specified value, and finally write the new value back to the CESR. The fifth byte in the buffer is an integer, represented as an enumerated type, specifying the type of counter initialization to perform. Since writing the CESR does not automatically clear the two counters, the user must specify whether the counters are to be initialized to zero, preset with some specified value, or left alone. Furthermore, the user can specify different types of initialization for each of the two counters. The various initialization

modes are summarized in Table 3.1. Finally, if the counters are to be preset, the values are provided in the next ten bytes of the buffer.

Table 3.1. Counter initialization control

| Value | Name         | Description                                       |  |

|-------|--------------|---------------------------------------------------|--|

| 0     | clr_none     | leave both counters alone                         |  |

| 1     | clr_0        | clear CNT0, leave CNT1 alone                      |  |

| 2     | clr_1        | clear CNT1, leave CNT0 alone                      |  |

| 3     | clr_0_1      | clear both CNT0 and CNT1                          |  |

| 4     | init_0_clr_1 | initialize CNT0, clear CNT1                       |  |

| 5     | init_1_clr_0 | initialize CNT1, clear CNT0                       |  |

| 6     | init_0       | initialize CNT0, leave CNT1 alone                 |  |

| 7     | init_1       | initialize CNT1, leave CNT0 alone                 |  |

| 8     | init_0_1     | initialize both CNT0 and CNT1                     |  |

| 9     | clear_only   | clear both CNT0 and CNT1, do not reconfigure CESR |  |

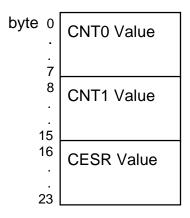

# 3.2.3.3 Reading the PMCs

Reading the PMCs, using the **read** system call, is much simpler than writing the counters [9]. The user passes a pointer to an empty 24-byte character buffer to the read device routine. This routine then places the values of counter 0, counter 1, and CESR into that buffer. The buffer format is shown in Figure 3.3.

Figure 3.3. P5mon device read buffer

While it is possible to create a smaller buffer, forming the buffer in this way allows much easier creation and access to the three elements in the buffer, either by using an array of six 32-bit unsigned integer types or an array of three 64-bit "long long" unsigned integer types. There is one caveat about using the 64-bit integer type. While GCC does support the 64-bit integer type internally, it is not supported by any library functions, such as *printf*. In order to display the values, they must first be converted to "double" (floating point) types.

### 3.2.3.4 Example p5mon device driver usage

Figure 3.4 contains a C program that illustrates how to use system calls to directly to access the PMCs through the p5mon device driver. This simple example creates a configuration buffer, opens the p5mon device, writes to the device, reads values out of the device, converts the values to "doubles", and finally displays the values to the screen. Comments within the code explain what is occurring at each step.

# 3.3 Library Routines

Using the device driver interface can be very difficult. It is prone to errors with incorrect character buffer sizes and formats, as well as incorrect command usage. In the interest of efficiency, very little error checking is done in the device driver itself. In order to provide some sort of error checking, as well as a more powerful interface, a set of library routines has been created to allow a user-level process to easily manage the p5mon device. In addition to providing higher-level "configuration" and "read" functions that operate on structures, the library routines provide a set of symbolic names to relate the event codes to the events they actually measure. By having the library routines carefully build up the character buffers, fatal errors involving the device driver will not occur. Ideally, any user interaction with the p5mon device will occur only through

```

int main() {

int P5MON; /* holds the p5mon device ID */

unsigned long long int buf[3]; /* 24-byte reading buffer */

char outbuf[5]; /* writing buffer */

double temp1, temp2; /* holds the results from the buffer */

/* Form the buffer to send to the device */

/* Since clearing the counters, only need a 5-byte buffer */

outbuf[0]=0x83; /* Event 0 is Data Read Miss, */

outbuf[1]=0; /* and count user-level events */

outbuf[2]=0x80; /* Event 1 is Data Read, */

outbuf[3]=0; /* and count user-level events */

/* want to clear both counters */

outbuf[4]=3;

/* Open the device using the "open" system call */

P5MON = open("/dev/p5mon", O_RDWR);

if(P5MON == 0) {

printf("opening unsuccessful ");

exit(1);

}

write(P5MON, outbuf, 5); /* Configure the counters */

read(P5MON, buf, 24); /* Read values back out */

/* Convert the unsigned long longs into 40-bit doubles */

temp1 = buf[0];

temp2 = buf[1];

printf("Counter 0 value: %f\n", temp1);

printf("Counter 1 value: %f\n", temp2);

printf("Ratio: %f\n", temp1/temp2);

close(P5MON); /* close the device */

return 0;

}

```

Figure 3.4. Example C program using p5mon device directly

this library. In the sections that follow, the library is first described, then is followed by an example using the library routines to obtain information from the PMCs.

# 3.3.1 Enumerated types

The library defines three sets of enumerated types that allow the user to specify symbolic names instead of numbers to reference certain key aspects of controlling the PMC configuration. These enumerated types are useful for any application using the p5mon device.

# 3.3.1.1 Events (EVENT)

The first enumerated type, defined to be the type EVENT, includes all possible events (described in Table 2.3, page 10) that the PMCs can measure, providing a mapping between event names and their corresponding event codes. This mapping is shown in Table 3.2. The number associated with each enumerated event is identical to the hex code for the event. Two additional special events, one that counts nothing and one that counts clock cycles, are also available. In addition to the enumerated type names themselves, a static character array containing the event names is available. This allows the user to easily output the name of the event based on the event number.

Table 3.2. Enumerated event names

| Event | Enumerated Event Name                   | Event  | Enumerated Event Name                         |

|-------|-----------------------------------------|--------|-----------------------------------------------|

| Code  |                                         | Code   |                                               |

| 0x00  | data_read                               | 0x14   | taken_branch_or_btb_hit                       |

| 0x01  | data_write                              | 0x15   | pipeline_flushes                              |

| 0x28  | data_read_or_write                      | 0x16   | instructions_executed                         |

| 0x02  | data_tlb_miss                           | 0x17   | instructions_executed_in_v_pipe               |

| 0x03  | data_read_miss                          | 0x18   | clocks_while_bus_cycle_in_progress            |

| 0x04  | data_write_miss                         | 0x19   | clocks_stalled_full_write_buffers             |

| 0x29  | data_read_or_write_miss                 | 0x1A   | clocks_stalled_waiting_data_read              |

| 0x05  | write_to_M_or_E_lines                   | 0x1B   | clocks_stalled_write_to_M_or_E_line           |

| 0x06  | data_cache_lines_written_back           | 0x1C   | locked_bus_cycle                              |

| 0x07  | external_snoops                         | 0x1D   | IO_read_or_write_cycle                        |

| 0x08  | data_cache_snooping_hits                | 0x1E   | non_cacheable_memory_reads                    |

| 0x09  | memory_accesses_in_both_pipes           | 0x1F   | pipeline_stalled_address_generation_interlock |

| 0x0A  | bank_conflicts                          | 0x22   | flops                                         |

| 0x0B  | misaligned_data_memory_or_IO_references | 0x23   | breakpoint_match_DR0                          |

| 0x0C  | code_read                               | 0x24   | breakpoint_match_DR1                          |

| 0x0D  | code_tlb_miss                           | 0x25   | breakpoint_match_DR2                          |

| 0x0E  | code_cache_miss                         | 0x26   | breakpoint_match_DR3                          |

| 0x0F  | segment_register_loaded                 | 0x27   | hardware_interrupts                           |

| 0x12  | branches                                | -none- | count_clocks                                  |

| 0x13  | btb_hits                                | -none- | event_disable (count nothing)                 |

# 3.3.1.2 Counter control (CNT\_CTRL)

The second enumerated type, CNT\_CTRL, specifies how each counter should be controlled. As discussed in Chapter 2, each counter may be configured to count events or clocks within the four different processor rings. Both counters can be configured individually. For example, the user may wish to count a certain event within the kernel level in one of the counters and count the same event within the user level in the other counter, thus allowing a comparison to be made between the user and kernel (i.e., operating system) levels. The different control modes and their associated enumerated type names are shown in Table 3.3.

Table 3.3. Counter control

| Name        | Description                                    |  |

|-------------|------------------------------------------------|--|

| evt_disable | disable counter                                |  |

| evt_kernel  | count kernel-level events                      |  |

| evt_user    | count user-level events                        |  |

| evt_all     | count both kernel- and user-level events       |  |

| clk_kernel  | count kernel-level clock cycles                |  |

| clk_user    | count user-level clock cycles                  |  |

| clk_all     | count both kernel- and user-level clock cycles |  |

# 3.3.1.3 Counter initialization (CNT\_CLR)

The final enumerated type, CNT\_CLR, describes how the counters are to be initialized. As mentioned in Section 3.2, each counter can be independently cleared or preset to a specified value. An additional name called *clear\_only* signals the library routines to only clear the counters and not write to the CESR. Table 3.4 lists the various initialization combinations and their associated enumerated type names.

Table 3.4. Counter initialization control

| Name         | Description                                       |

|--------------|---------------------------------------------------|

| clr_none     | leave both counters alone                         |

| clr_0        | clear CNT0, leave CNT1 alone                      |

| clr_1        | clear CNT1, leave CNT0 alone                      |

| clr_0_1      | clear both CNT0 and CNT1                          |

| init_0_clr_1 | initialize CNT0, clear CNT1                       |

| init_1_clr_0 | initialize CNT1, clear CNT0                       |

| init_0       | initialize CNT0, leave CNT1 alone                 |

| init_1       | initialize CNT1, leave CNT0 alone                 |

| init_0_1     | initialize both CNT0 and CNT1                     |

| clear_only   | clear both CNT0 and CNT1, do not reconfigure CESR |

#### 3.3.2 Structures

A configuration structure, CNT\_CONFIG, is used to allow the user to configure the PMCs. The user merely fills in the fields of the structure, then the library functions convert the structure into the character buffer format that the p5mon device understands. Similarly, another routine can generate a configuration structure given the value of the CESR. The structure itself contains seven different fields. Table 3.4 lists the various fields in the structure, their types, and a brief description.

Table 3.5. CNT\_CONFIG structure fields

| Structure Field | Type           | Description                   |

|-----------------|----------------|-------------------------------|

| event0          | EVENT          | event to be counted in CNT0   |

| event1          | EVENT          | event to be counted in CNT1   |

| ctrl1           | CNT_CTRL       | CNT1 operation control        |

| ctrl0           | CNT_CTRL       | CNT0 operation control        |

| clr             | CNT_CLR        | configuration mode to use     |

| init0           | 64-bit integer | 40-bit initial value for CNT0 |

| init1           | 64-bit integer | 40-bit initial value for CNT1 |

# 3.3.3 Functions

The other features in the library are the functions that act as an interface between the user and the device driver. The prototypes for six different functions are shown in Figure 3.5 and are described in the following sections.

```

int p5mon_init();

int p5mon_close();

int p5mon_clear();

int p5mon_config(CNT_CONFIG *config);

int p5mon_read(ULONG *result);

void p5mon_gen_config(ULONG cesr, CNT_CONFIG *config);

```

Figure 3.5. Libp5mon function prototypes

# 3.3.3.1 p5mon\_init and p5mon\_close

These two functions open and close the p5mon device. The device must be initialized before it is used, and should be closed before the program exits.

# 3.3.3.2 p5mon\_clear

This function clears the two counters but does not reconfigure the CESR. This allows the user to reset the counters whenever desired without knowing what events are actually being counted.

# 3.3.3.3 p5mon\_config

This function is the most complicated function in the library. As its name suggests, it is responsible for configuring the CESR to count various events. It takes the configuration structure described in Section 3.3.2 as input, builds the character write buffer described in Section 3.2.3.2, and writes the character buffer to the p5mon device. This function also provides some error checking on the configuration structure as well.

# 3.3.3.4 p5mon\_read

This is the companion function to *p5mon\_config*. It simply reads both counters and the CESR, and puts the results into an array of three 64-bit integers in that order.

# 3.3.3.5 p5mon\_gen\_config

This function fills in the configuration structure fields based on the CESR value passed to the function, so that the user doesn't have to know the format of the CESR to interpret what is being counted.

# 3.3.4 Example p5mon library routines usage

Figure 3.6 contains a C program that illustrates how to use the p5mon library routines to access the PMCs. This example has the same function as the example shown in Figure 3.4 (page 18) and is useful for seeing the differences in using the library routines versus directly accessing the p5mon device. This simple example initializes the p5mon device, creates a simple configuration structure, calls the configuration routine, uses the read function to get the value of the counters, and finally prints the values to *stdout* (standard out). The primary difference is in the method of configuring the CESR. Comments within the code explain what is occurring at each step.

# 3.4 Summary

The device driver and the library provide the interface needed to access the Pentium's performance monitoring counters. Appendix B describes how to install the p5mon device and library onto a Linux system. For more detailed information, the reader is encouraged to look at the source code. These software routines provide access to the counters, but they don't provide power. The real power of the counters comes from the ability to measure different events in real programs, look at multiple results to compute averages and other statistics, and examine smaller regions of a program without having to worry about all the details of creating configuration

```

#include "libp5mon.h"

int main() {

CNT_CONFIG p5mon_cfg; /* configuration structure */

unsigned long long results[3]; /* array for results */

double temp1, temp2; /* temp values */

/* initialize the p5mon device */

if(p5mon_init()) {

printf("Unable to initialize p5mon device\n");

exit(-1);

/* Build up the configuration structure */

p5mon_cfg.event0 = data_read_miss;

p5mon_cfg.ctrl0 = evt_user;

p5mon_cfg.init0 = (unsigned long long) 0x0;

p5mon_cfg.event1 = data_read;

p5mon cfg.ctrl1 = evt user;

p5mon cfg.init1 = (unsigned long long) 0x0;

p5mon_cfg.clr = init_0_1;

p5mon_config(&p5mon_cfg); /* Configure PMCs */

p5mon_read(results); /* Read PMCs */

/* Convert the unsigned long longs into 40-bit doubles */

temp1 = (double) results[0]

temp2 = (double) results[1]

printf("Counter 0 value: %f\n", temp1);

printf("Counter 1 value: %f\n", temp2);

printf("Ratio: %f\n", temp1/temp2);

p5mon_close(); /* close the device */

exit(0);

}

```

Figure 3.6. Example C program using p5mon library routines

structures and reading the counters. A program called run\_p5mon uses the library routines described in this chapter to create the power of this software.

# 4. RUN P5MON

#### 4.1 Motivation

Run\_p5mon is a C program that allows a user to easily measure different events in an executable with little or no modifications to the source code of the program. Run\_p5mon acts as an interface to the p5mon library routines to allow the user to easily turn on and off various events, run each event multiple times, and compute statistics for each event. By using run\_p5mon, the user doesn't have to worry about configuring the performance monitoring counters (PMCs), managing buffers, or keeping track of what events have been measured.

Run\_p5mon has been designed with two goals in mind. It allows a user to measure events on a per-executable basis without any modification to the program's source code. Since there is no source code modification, no recompilation of the program is required to measure events. By using this method, the user can obtain statistics for the entire program. However, sometimes the user would like to obtain finer-grain data on the program. In order to support this, run\_p5mon's second goal is to allow the user to make some minor additions to the assembly-level source code, recompile this modified program, and then use run\_p5mon as a driver for this modified program.

# 4.2 Overview of run\_p5mon

Run\_p5mon acts as a controlling process for measuring events in a program. Fully configurable by the user, it is responsible for running the program to be monitored, gathering and computing statistics, and displaying the results. It uses the p5mon library functions to access the p5mon device driver as described in Chapter 3. In fact, it can be thought of as the "user process"

portion within the abstraction layers shown in Figure 3.1 (page 11). Figure 4.1 is a high-level algorithm showing how run\_p5mon works.

Figure 4.1. Run\_p5mon algorithm

Run\_p5mon takes an arbitrary length event list, as specified by the configuration options, and pairs up the events to measure two at a time, since the PMCs allow at most two events to be measure simultaneously. In order to measure many events, run\_p5mon will actually execute the program multiple times. In addition, since the results may not be precise, the user may wish to measure each individual event multiple times. This is termed the number of repetitions. This should not be confused with having to run the program multiple times to gather data for all the events. Run\_p5mon can support both unmodified and modified executables.

# 4.2.1 Unmodified executable

As the name suggests, running an unmodified executable requires no modification to the machine-level code. Events are measured from the program's entry to its exit, including the operating system overhead in order to create and destroy the process.

#### 4.2.2 Modified executable

If the user desires finer-grain information, probes can be inserted into the assembly code of the program to define regions. These regions can overlap or be executed multiple times (e.g., loops). To define the regions, the user inserts one-line function calls in the assembly code, called "assembly stubs," that act as probes. These one-line function calls are actually wrappers to simple C functions. Up to 100 regions may be defined in a program in the current version of run\_p5mon. More regions may be added by changing a constant within run\_p5mon and recompiling.

As the modified program is being executed, the assembly stubs and, in turn, the C functions are called. The begin and end region function calls merely sample the PMCs as the program executes and store the difference in an accumulator corresponding to the region. When the modified program exits, all data are written to a temporary file that run\_p5mon then uses to compute statistics to output to the user. Just as with the unmodified executable, run\_p5mon acts as a driver by configuring the PMCs and controlling the number of times the program must be executed to measure all of the events. In order to use these stubs, the user must have access to the assembly code and be willing to recompile the code after inserting the stubs. These function calls add a relatively constant overhead to the data being gathered each time they are called.

All of the assembly stub routines are defined in two files. The file *p5mon\_asm.c* contains all of the C functions and the file *p5mon\_asm\_elf.s* contains the assembly stubs themselves. Both files are automatically compiled into the p5mon library (libp5mon). When the modified assembly code is recompiled, it must be linked to the p5mon library by adding the *-lp5mon* flag to the compiler command line.

Before defining any regions, it is necessary to call the initialization function, p5mon\_asm\_init, in order to create some data structures to hold information. Regions themselves are defined between a "begin region" and "end region" function call. These two functions take the form of *p5mon\_asm\_begreg\_X* and *p5mon\_asm\_endreg\_X*, where *X* is a number between 0 and 99. The begin-region function samples the PMCs and stores the value in a temporary array. The end-region function again samples the PMCs, subtracts the starting value, and adds the result into an accumulator. In order to have the correct value in the accumulator, the user should make sure that the number of times that a region is entered is the same as the number of times that it is exited. A detailed example using the assembly regions is provided in Chapter 5.

# 4.3 Configuring run\_p5mon

The power of run\_p5mon lies in its ability to be easily configured to perform a variety of tasks, freeing the user from having to manipulate the PMCs, keeping track of buffers, and computing statistics.

# 4.3.1 IMPACT parameters facility

All modules within the IMPACT (Illinois Microarchitecture Project Utilizing Advanced Compiler Technology) research compiler use the same parameter facility for configuration. Each IMPACT module can have its own set of parameters, located in what is known as a PARMS (or parameters) file. Run\_p5mon has its own section, called "p5mon," that specifies its configuration. These parameters control all aspects of run\_p5mon, from the events to measure to the executable to use. In addition to the PARMS file itself, the user may use "-P" and "-F" command line switches to control run\_p5mon configuration. For more information on the IMPACT parameter facility, the reader is encouraged to look at the PARMS tutorial [10]. Using this parameter

passing facility allows a user to customize run\_p5mon for a given benchmark, just as the user would for any other aspects of compilation within IMPACT.

# 4.3.2 Basic configuration options

Below are the six basic configuration options for run\_p5mon. The heading for each subsection is also the parameter name. Most configuration values have some sort of default value that is indicated. All configuration parameters, as well as a sample PARMS file, are summarized in Appendix C.

#### 4.3.2.1 command

Quite simply, this is the program measured by run\_p5mon. The command parameter should contain the full command line used to invoke this program, including any command line arguments or redirection. If the executable is not in the current directory, the full path should also be specified. The executable format of the binary, a.out or ELF, does not matter. This parameter has no default value and must be specified.

# 4.3.2.2 repetitions

This parameter specifies how many times each event should be measured. This parameter has a default value of one.

# 4.3.2.3 user\_events, kernel\_events

These two parameters control the level, user, kernel, or both, in which the events should be counted. The default is to count only user-level events. If both user- and kernel-level events are enabled, both are counted. If neither is enabled, a warning message will be printed because nothing is being counted.

## 4.3.2.4 output\_all\_results

This parameter allows the user to see the results obtained for each repetition of each event, as well as a final average and confidence interval based on all the repetitions. This parameter might be used to analyze results both when there is a relatively wide confidence interval and when the confidence interval is equal to zero. If the number of repetitions is large, a great deal of information will be printed. The default for this parameter is "no," meaning the extra information is not printed.

## 4.3.2.5 confidence\_level\_99

This parameter is used to trigger which statistical confidence interval, 95% or 99%, is provided in the results. The default confidence interval is 95%. If the user wishes to have a higher confidence interval, this parameter can be enabled to calculate the 99% confidence interval. The statistical confidence intervals are discussed in Section 4.5.1.

#### 4.3.3 Advanced configuration options

In addition to the six basic configuration parameters, five advanced configuration options allow even more control of run\_p5mon.

# 4.3.3.1 use\_assembly\_regions

This parameter instructs run\_p5mon to run an executable that contains assembly stubs. By default, it is disabled. If assembly stubs are being used, this parameter must be enabled in order to instruct run\_p5mon to look for the file containing the data gathered on the regions generated by the modified executable.

# 4.3.3.2 max\_regions

This parameter is used in conjunction with the previous parameter. It informs run\_p5mon of the maximum number of regions present in the modified executable, which cannot be greater than 100. By default, this parameter is set to ten. It helps run\_p5mon to limit memory usage while computing statistics.

## 4.3.3.3 output\_file

This parameter specifies the name of a file in which to write the results. The results are written out in a format that can be easily parsed to allow the data to be used by other programs. Even when an output file is specified, results are written to *stdout*. The format of the output file is given in Section 4.5.3.

# 4.3.3.4 skip\_initialization\_run

By default, before gathering data on an executable, run\_p5mon will first execute the program to try to minimize some of the start-up effects, such as cold-start cache misses. If the user does not wish to perform this initialization, this parameter should be set to "no." Be aware, however, that the values of the first two events measured will be affected.

#### 4.3.3.5 verbose\_level

This integer parameter is used to see the status of run\_p5mon as it executes. This parameter is useful if run\_p5mon takes a long time to execute. By default, this parameter is set to zero, which means all messages are turned off. Level 1 prints a message at the beginning of each repetition. Level 2 prints a message at the start of each execution and specifies the events being measured. All messages are printed to *stderr* (standard error) so that normal program output may be redirected.

#### 4.3.3.6 Events

Thirty-nine different events can be counted, including the 38 that the hardware directly supports, plus one event to count total clock cycles. Each event can be turned on or off as needed by setting its parameter to a "yes" or a "no" value. By default, all events are disabled. The name of each parameter is very similar to the actual event names. These parameters are summarized in Appendix C.

#### 4.4 Results

After gathering results for all the specified events, run\_p5mon generates a report containing the raw data as well as averages and confidence intervals on the data gathered.

## 4.4.1 Run\_p5mon statistics

Run\_p5mon computes two different statistics for each event that it measures. First, run\_p5mon computes an average value of the event based on the data for each repetition.

Second, run\_p5mon computes a two-sided confidence level on the data. Run\_p5mon can compute both a 95% and a 99% confidence interval, based on the value of the *conf\_level\_99* parameter. This confidence interval is computed using standard statistical techniques [4]. The meaning of the 95% confidence interval is that the probability that the "real" value lies within the range of the average, plus or minus the confidence interval, is equal to 95%. Thus, there is a 95% probability that if the same event were measured under the same set of conditions, including system load and input parameters, the result obtained would lie within this range.

# **4.4.2** Output report format

After computing statistics, run\_p5mon generates a report. The two sections of the report, the header and the detailed information, are described below. The information contained in the

detailed information section depends on the values of the *output\_all\_results* and *use\_assembly\_regions* parameters.

#### 4.4.2.1 Header information

The first part of the report, the header, consists of the date and time run\_p5mon started, the directory in which it was invoked, the parameter file read, the command-line arguments passed to run\_p5mon (such as the -F arguments), and the program actually executed. A sample header is shown in Figure 4.2.

run\_p5mon started at Thu Jan 30 16:02:20 1997

current directory: /home/fixed/safford/p5mon

parameter file: ./STD\_PARMS

arguments:

command: hello

Figure 4.2. Sample header from run\_p5mon

## 4.4.2.2 Summary information

The second part of the report contains the data gathered on the program execution behavior. The exact format of this section depends on the parameters described in Section 4.3. The first line of this section will contain the number of repetitions and the confidence interval, then the results of each event are given on a single line, with the event name first, followed by the average value. After the average, the confidence interval is displayed as "+/- <conf int> (<percentage>%)" where "<conf\_int>" is the raw confidence interval, and "<percentage>" is the confidence interval expressed as a percentage of the average. The final lines of the report show the total run time for the entire execution of the run\_p5mon program, as well as the number of times the program actually executed to gather the data. A sample results section is shown in Figure 4.3.

```

Results (for 5 repetitions with a 95% confidence level):

Data Read: 201900.0 +/- 2.8 (0.001%)

Data TLB Miss: 269.0 +/- 0.0 (0.000%)

Code Read: 202666.4 +/- 38.8 (0.019%)

Code TLB Miss: 525.4 +/- 10.2 (1.941%)

Instructions Executed in the v-pipe: 141021.6 +/- 21.5 (0.015%)

Clock cycles: 201900.0 +/- 2.8 (0.001%)

Total elapsed time: 1.0 seconds

(program executed 15 times, with an average execution time of 0.1s)

```

Figure 4.3. Sample results section from run p5mon

#### 4.4.2.3 Detailed information

Setting the parameter *output\_all\_results* to "yes" displays the data collected for each repetition of each event, in addition to the summary information. The value for each repetition of the event is shown on its own line. Averages and confidence intervals follow in the same format as described in Section 4.4.2.2. A sample results section containing this information is shown in Figure 4.4.

```

Results (for 5 repetitions with a 95% confidence level):

Event: Data Read

201902

rep 0:

rep 1:

201902

201902

rep 2:

201902

rep 3:

rep 4:

201907

Average:

201903.0 +/- 2.3 (0.001%)

Event: Data TLB Miss

rep 0:

269

rep 1:

269

rep 2:

269

rep 3:

269

rep 4:

271

Average:

269.4 +/- 0.9 (0.341\%)

Total elapsed time: 1.3 seconds

(program executed 5 times, with an average execution time of 0.3s)

```

Figure 4.4. Sample results section containing results from each repetition

#### 4.4.2.4 Regions

If the executable contains assembly regions, the output will have information broken down by regions. The first line of the results section contains the number of regions, the number of repetitions, and the confidence level computed. Each region itself has a header, containing both the region number and the number of times the particular region was entered and exited. Within each region, each event measured results in a corresponding summary line, in a format similar to the summary line information described in Section 4.4.2.2. The only addition is the number within brackets at the end of the line, which is the average value divided by the number of times the region was entered. If the *output\_all\_results* parameter is set to "yes," each event within each region will also have a corresponding output line, as described in Section 4.4.2.3. The next two figures, Figures 4.5 and 4.6, show the results using multiple regions, both with and without this parameter set to "yes."

```

Results (for 3 regions, 3 repetitions, 95% confidence level):

Region 0, entered 1 times and exited 1 times:

Branches: 797.0 +/- 0.0 (0.000%) [797.0]

BTB Hits: 502.3 +/- 11.3 (2.241%) [502.3]

Region 1, entered 100 times and exited 100 times:

Branches: 3900.0 +/- 0.0 (0.000%) [39.0]

BTB Hits: 2993.0 +/- 6.5 (0.218%) [29.9]

Region 2, entered 1 times and exited 1 times:

Branches: 174.0 +/- 0.0 (0.000%) [174.0]

BTB Hits: 57.3 +/- 3.1 (5.446%) [57.3]

```

Figure 4.5. Sample results with multiple regions

#### 4.4.3 Output file format

In addition to outputting the results to *stdout*, run\_p5mon also creates a file containing data that is suitable for parsing when a file is specified in the *output\_file* parameter. The data contained in this file will differ depending on the value of the *output\_all\_results* parameter and whether regions have been defined. Any line beginning with a "#" in the output file is considered

```

Results (for 3 regions, 3 repetitions, 95% confidence level):

Region 0, entered 1 times and exited 1 times: Event: Branches

rep 1:

797 rep 3:

Average: 797.0 +/- 0.0 (0.000%) 797.0 per time region entered

Event: BTB Hits

498

498

rep 1:

rep 2:

rep 3:

511

Average: 502.3 +/- 11.3 (2.241%) 502.3 per time region entered

Region 1, entered 100 times and exited 100 times:

Event: Branches

3900

rep 1:

rep 2: 3900

rep 3: 3900

Average: 3900.0 +/- 0.0 (0.000%)

39.0 per time region entered

Event: BTB Hits

rep 1: 2995

rep 2: 2996

rep 3: 2988

Average: 2993.0 +/- 6.5 (0.218%)

29.9 per time region entered

Region 2, entered 1 times and exited 1 times:

Event: Branches

rep 1: 174

rep 2: 174

rep 3: 174

Average: 174.0 +/- 0.0 (0.000%)

174.0 per time region entered

Event: BTB Hits

59

rep 1:

rep 2:

58

rep 3:

55

Average:

57.3 +/- 3.1 (5.446%)

57.3 per time region entered

```

Figure 4.6. Sample results with multiple regions, displaying the results for each repetition a comment. The first part of the file is a header specifying the number of regions (if regions are being used), the number of repetitions, and the confidence level. The next line contains a listing of the fields present in this file, to help guide parsing the file. Following the header lines are the results. In order to conserve space and simplify parsing, the events are specified by their actual event codes.

#### 4.4.3.1 All results with no regions defined

When the user uses an unmodified executable and requests the results from each repetition, each result will lie on a separate line. The event code is the first number on each line, followed by the repetition that the data corresponds to, and finally, the value of the counter for that repetition. However, a repetition number of "-1" indicates that the line contains summary information. These lines have a slightly different format. The third number is the average result from all the repetitions of this event. The fourth and fifth numbers are the confidence interval expressed as a number and then a percentage of the average value. Figure 4.7 contains a sample output file with this information.

```

# run_p5mon results file

# Results (5 repetitions, 95% confidence level):

# Event Repetition Value [conf.int] [percentage]

0x30

11113

0x31

11003

0x32

10962

0x33

10975

10979

0x34

0x3 - 1

11006.4 63.2 0.574

0x40

8856

0x4 1

8876

0x42

8816

0x43

8850

0x44

8845

0x4 - 1

8848.6 22.3 0.252

```

Figure 4.7. Sample output file containing all results with no regions

#### 4.4.3.2 Summary information only, with no regions defined

When the user requests only summary information for each event, only the summary lines are printed. Sample output is shown in Figure 4.8.

Figure 4.8. Sample output file with no regions, and summary information only

## 4.4.3.3 Regions defined

When a modified executable containing regions is used, the region number is simply added to the beginning of each line. The rest of the fields do not change. To make reading easier, comment lines are inserted at the beginning of each region. Figure 4.9 shows all of the results of an executable with multiple regions.

```

# run_p5mon results file

# Results (for 2 regions, 5 repetitions, 95% confidence level):

# Region Event Repetition Value [conf.int] [percentage]

# Region 0: entered 1 exited 1

0.0x3.0

5

0.0x31

5

0.0x3.2

5

5

0.0x3.3

0.0x3.4

0 0x3 -1

5.0 0.0 0.000 5.0

0.0x4.0

6

0.0x41

6

0.0x4.2

6

0.0x4.3

6

0.0x4.4

6.0 0.0 0.000 6.0

0.0x4 - 1

# Region 1: entered 1 exited 1

1 0x3 0

0

1 0x3 1

0

1 0x3 2

0

1 0x3 3

1 0x3 4

0.0 0.0 NaN 0.0

1 0x3 -1

1 0x4 0

2

1 0x4 1

2

2

1 0x4 2

1 0x4 3

1 0x4 4

1 0x4 -1

2.0 0.0 0.000 2.0

```

Figure 4.9. Sample output file with multiple regions

# 4.5 Interpreting the Results

When examining the results obtained from run\_p5mon, the user must realize that there are several sources of error in the values measured. First, and most important, since the PMCs are not context switched, they measure the activity in the entire system. Thus, background noise caused by other running processes in the system will cause the results to vary. Results with wide

confidence intervals are one sign of an excessive amount of background noise in the system. There are several ways of removing the effect of background processes. The first, and simplest, is to simply not run any other jobs in the system while gathering data using run\_p5mon. This includes any system processes that are not crucial to system operation. Another method is to lower the priority of the other processes with the *nice* or *renice* system commands, and to raise the priority of the run\_p5mon process. This will, in effect, stop the other jobs in the system without having to kill them.

The second source of error is the operating system overhead incurred when creating and destroying a process. This overhead can be eliminated by defining one assembly-level region covering the entire program. This is the most accurate method to measure events on an entire executable, and should be used whenever possible. Also, since this effect can be easily measured to an extent, a user can subtract the overhead from the results obtained in order to find the true values. Appendix D lists the approximate overhead values observed when using these counters.