# AN OPTIMIZING COMPILER CODE GENERATOR: A PLATFORM FOR RISC PERFORMANCE ANALYSIS

## BY

# WILLIAM YU-WEI CHEN, JR.

B.S., The Ohio State University, 1988

# THESIS

Submitted in partial fulfillment of the requirements for the degree of Master of Science in Electrical Engineering in the Graduate College of the University of Illinois at Urbana-Champaign, 1991

Urbana, Illinois

#### ACKNOWLEDGEMENTS

I would like to thank my advisor, Professor Wen-mei Hwu, for providing constant guidance and support. His patience was invaluable. I would also like to thank Sabrina Hwu for taking care of me for the past few years.

I wish to thank Pohua Chang for his constant suggestion and help. This thesis would not be possible without his work. Scott Mahlke and I have complemented each other's work during this time, and his cooperation in this project is very helpful. Thomas Conte, Nancy Warter, Sadun Anik and other members of the research group were always there to provide me with their insight and knowledge to further my study.

I wish to thank my friends here at the University of Illinois, especially Jaushin Lee, for their friendship and support.

Finally, I would like to thank my parents, William and Pauline, for their love and support. They have taught me to think before acting, which made my conviction toward attending graduate school much stronger.

# TABLE OF CONTENTS

|   |              |                                                | Page          |

|---|--------------|------------------------------------------------|---------------|

| 1 | INTO         | EDODICTION                                     | 1             |

| 1 | 11N 1<br>1.1 | ΓRODUCTION                                     | 1             |

|   | 1.1          | Outline of the Thesis                          | $\frac{1}{2}$ |

|   | 1.2          | Outline of the Thesis                          | Δ             |

| 2 | ТН           | E IMPCC/MIPS CODE GENERATOR                    | 3             |

|   | 2.1          | LCODE Environment                              | 3             |

|   | 2.2          | MIPS Convention Overview                       | 4             |

|   | 2.3          | Data Generation                                | 8             |

|   | 2.4          | Instruction Selection                          | 9             |

|   | 2.5          | Machine Dependent Optimizations                | 19            |

|   | 2.6          | Register Allocation                            | 22            |

|   | 2.7          | Register Assignment                            | 24            |

|   | 2.8          | MIPS Assembly Code Output                      | 26            |

| 3 | LO           | W-LEVEL SUPPORTING TOOLS                       | 28            |

|   | 3.1          | Probing LCODE                                  | 28            |

|   |              | 3.1.1 Statically available information         | 29            |

|   |              | 3.1.2 Dynamically available information        | 29            |

|   | 3.2          | Supporting Tool to Analyzer Interface          | 30            |

|   |              | 3.2.1 LCODE profiler interface                 | 30            |

|   |              | 3.2.2 LCODE trace generator interface          | 31            |

|   | 3.3          | LCODE Profiler                                 | 31            |

|   | 3.4          | LCODE Trace Generator                          | 33            |

|   | 3.5          | Implementation Hazards and Difficulties        | 33            |

| 4 | СО           | DE SCHEDULING STUDIES USING THE CODE GENERATOR | 35            |

|   | 4.1          | Static Code Scheduling                         | 35            |

|   | 4.2          | Hardware Scheduling Approach                   | 36            |

|   | 4.3          | Experiments                                    | 38            |

|   |     | 4.3.1   | Benchmark programs                       | 38       |

|---|-----|---------|------------------------------------------|----------|

|   |     | 4.3.2   | Base architecture                        | 39       |

|   |     | 4.3.3   | Multiple-instruction-issue architectures | 39       |

|   |     | 4.3.4   | Measurement tools                        | 40       |

|   | 4.4 | Result  | s and Analysis                           | 41       |

|   |     | 4.4.1   | Ideal cache results                      | 42       |

|   |     | 4.4.2   | Small cache results                      | 44       |

| 5 |     |         | ICES                                     | 47<br>49 |

|   | APF | PENDIX  | X A AN EXAMPLE OF CODE GENERATION        | 50       |

|   | A.1 | Sampl   | e Program                                | 50       |

|   |     |         | E Program                                | 51       |

|   | A.3 | MIPS    | Code Generation Result                   | 52       |

|   | A.4 | Inserti | ng Probes by the LCODE Profiler          | 53       |

|   | A.5 | Inserti | ng Probes by the LCODE Trace Generator   | 56       |

# LIST OF TABLES

| Table                                                                | Page   |

|----------------------------------------------------------------------|--------|

| 2.1: General register set                                            | <br>7  |

| 2.2: Floating-point register set                                     | 7      |

| 2.3: Register usage for parameter passing                            | 7      |

| 2.4: LCODE assembly macros                                           | 10     |

| 2.5: LCODE integer branch instructions                               | 11     |

| 2.6: LCODE single-precision floating-point branch instructions.      | <br>12 |

| 2.7: LCODE double-precision floating-point branch instructions       | <br>13 |

| 2.8: LCODE integer arithmetic instructions                           | <br>14 |

| 2.9: LCODE single-precision floating-point arithmetic instructions.  | <br>15 |

| 2.10: LCODE double-precision floating-point arithmetic instructions. | <br>16 |

| 2.11: LCODE move instructions                                        | <br>17 |

| 2.12: LCODE type conversion instructions                             | 17     |

| 2.13: LCODE load/store instructions                                  | 18     |

| 2.14: Load/store addressing modes                                    | 18     |

| 4.1: Benchmarks                                                      | 38     |

| 4.2: Operation latencies                                             | 39     |

| 4.3: Individual benchmark program results for ideal cache            | 43     |

| 4.4: Individual benchmark program results for 8KB cache              | 45     |

| 4.5: Individual benchmark program results for 16KB cache             | 46     |

| A.1: Definition of the probing variables                             | 53     |

# LIST OF FIGURES

| Figure |                                  | Page |

|--------|----------------------------------|------|

| 2.1:   | LCODE within IMPACT-I C compiler | 4    |

| 2.2:   | Program memory divisions         | 5    |

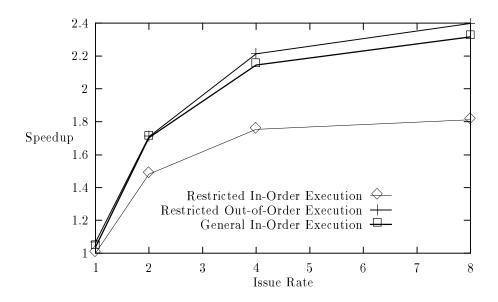

|        | Speedup for ideal cache.         | 42   |

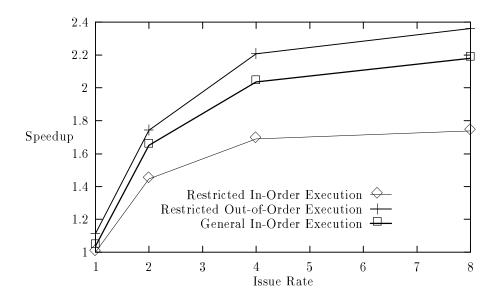

| 4.2:   | Speedup for 8KB data cache       | 44   |

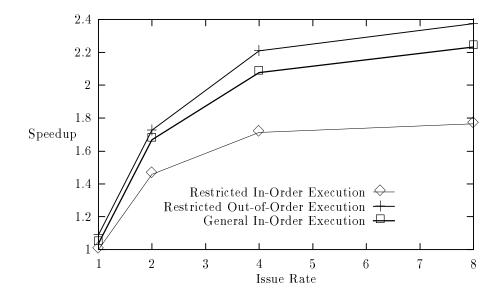

| 4.3:   | Speedup for 16KB data cache.     | 45   |

#### 1. INTRODUCTION

#### 1.1 Motivation

In the process of designing an architecture, the support of a good compiler cannot be ignored. The IMPACT-I C compiler generates a highly optimized code for processors designed within the IMPACT Architectural Framework. The IMPACT-I C compiler is retargetable, and can easily integrate with other optimizers and lower-level tools. This integration is possible through LCODE, the IMPACT-I low-level intermediate code.

The performance implication of the IMPACT-I C compiler is not known until it can be compared with a leading commercial compiler. Also, the worth of a compiler is judged by its ability to generate executable code. The construction of a code generator for the DEC 3100 Workstation satisfies both conditions. The IMPCC/MIPS code generator allows the performance comparison of the IMPACT-I C compiler with that of a leading commercial C compiler, MIPS C compiler. This comparison provides other researchers a basic understanding in the base technology for our architectural studies.

In the environment of an university, it is usually too costly and impractical to perform architectural studies by building the actual hardware; the studies are typically carried out by simulations. For our architectural studies, we constructed two low-level supporting tools: an LCODE profiler and an LCODE trace generator. These two tools provide accurate and efficient ways of interpreting LCODE instruction level information. With an LCODE profiler, accurate instruction count and accurate branch flow directions are measured. With an LCODE trace generator, accurate instruction execution sequence is generated. Both the LCODE profiler and LCODE trace generator conform to a standard interface and are built in addition to the IMPCC/MIPS code generator. Thus, by providing a trace analyzer which conforms to the standard interface, the users aquire immediate support from these two low-level LCODE supporting tools to perform various types of RISC architecture studies.

#### 1.2 Outline of the Thesis

In Chapter 2, the general overview of the IMPCC/MIPS code generator is discussed. The main focus is on how to generate correct and fast execution code. Chapter 3 gives the modification of the IMPCC/MIPS code generator to create useful low-level supporting tools for architectural studies. The use of these low-level supporting tools is shown in Chapter 4. The comparison of static and dynamic code scheduling on a multiple-instruction-issue processor is used as an example. Chapter 5 gives the concluding remarks.

# 2. THE IMPCC/MIPS CODE GENERATOR

#### 2.1 LCODE Environment

LCODE <sup>1</sup> (low-level intermediate code) is a register transfer language designed to provide an easy interface between high- and low-level languages. All low-level supporting tools are implemented in addition to LCODE, and these tools include the LCODE code optimizer, machine-dependent code generators, LCODE profilers, and LCODE trace generators. By following the LCODE interfacing rules, all high level languages are automatically supported by these low-level tools that are either available or under development. Figure 2.1 provides an overview as to where LCODE fits in the whole IMPACT-I C compiler structure.

LCODE is divided into two distinct sections: data declaration and function definition. Each instruction of LCODE is presented in a Lisp-like format, and two sets of data structures are created to store the LCODE instructions. The first data structure contains the data section, and the second data structure contains the function section. One data declaration instruction or one function are read in at a time.

<sup>&</sup>lt;sup>1</sup>LCODE documentation is available as an internal report.

Figure 2.1: LCODE within IMPACT-I C compiler.

#### 2.2 MIPS Convention Overview

In order to maximize the performance of a code generator, the MIPS architecture must be carefully studied. The information presented in this section is published by Kane [1] and MIPS Computer Systems [2]. These books should be read for a more detailed explanation. The MIPS memory system is divided into the text and the data sections. The data section is further divided into several smaller sections, each with a special purpose. For simplicity, Figure 2.2 provides a breakdown of the MIPS program memory that is utilized by the IMPCC/MIPS code generator. The text memory is for storing the user program instructions. All instructions are aligned on the boundary of four bytes. The data memory stores global variable values. The 32-bit addressing mode is used for accessing the variable values in the data memory. The small data memory has only 64k of space and is also used for storing global variable values. The small data

Figure 2.2: Program memory divisions.

memory uses the 16-bit addressing mode. Thus, each value within the small data memory can be accessed using only one instruction, where the 16-bit address offset is embedded in the immediate value part of the load/store instruction. The base address for the small data section is contained in gp, the global pointer register. On the other hand, the values within the data memory require two instructions to access. The third data section is the stack memory. All information local to the currently executed function is stored on the stack. For the IMPCC/MIPS code generator, the stack is used for storing parameters to be passed, local variables, caller saved registers, callee saved registers, returned structure values, and all spilled register contents. The current stack address is contained in sp, the stack pointer register. All contents above the stack pointer are assumed to be safe, and cannot be changed by other processes.

In order to be compatible with the system libraries or other user written assembly code, the calling convention must be coherent. There are several major constraints.

- 1. Stack layout must be the same.

- 2. Parameter passing methods must be coherent.

- 3. Register usage must be consistent.

The MIPS architecture keeps two pointers with respect to the stack; one is the stack pointer and the other one is the frame pointer. All stack accesses are in reference to these two pointers. The positive difference between the current stack pointer and the current frame pointer is the frame size of the current function. The space immediately above the current stack pointer location contains the parameters to be passed, if any, for the function to be called. At least 16 bytes must be allocated on the stack for these parameters that are passed in registers. The space immediately below the current frame pointer is the local variable location. The space immediately above the current frame pointer is for the passing parameters of the current function. All other space on the stack can be used freely.

The MIPS register set and its usage are presented in Tables 2.1 and 2.2. Four integer registers and two double floating-point registers are used for passing registers, but at most, four words (each integer register is a word, and each double floating-point register is two words) can be passed in register for each function call. These register numbers are 4, 5, 6, 4 and 7 for the integer registers, and 12, 4 for the double floating-point registers. Table 2.3 lists some possible parameter passing situations. The notations 12, 4 and 12, 4 for the double floating-point registers. Table 2.3 lists some possible parameter passing situations. The notations 12, 4 indicate integer or floating-point parameter type. The number following 12, 4 indicates the occurrence of that parameter type. The algorithm for passing parameters in registers is presented in the following rules.

Table 2.1: General register set.

| Register | Usage                               |

|----------|-------------------------------------|

| \$0      | Constant value of zero              |

| \$1      | Reserved and not usable             |

| \$2      | Return register for integer values  |

| \$3      | Caller saved register               |

| \$4\$7   | Integer parameter passing registers |

| \$8\$15  | Caller saved registers              |

| \$16\$23 | Callee saved registers              |

| \$24\$25 | Caller saved registers              |

| \$26\$27 | Reserved and not usable             |

| \$28     | Global memory address pointer       |

| \$29     | Stack pointer                       |

| \$30     | Frame pointer                       |

| \$31     | Return address                      |

Table 2.2: Floating-point register set.

| Register                                            | Usage                                      |

|-----------------------------------------------------|--------------------------------------------|

| \$f0\$f1 Return registers for floating point values |                                            |

| \$f2\$f11                                           | Caller saved registers                     |

| \$f12\$f15                                          | Floating point parameter passing registers |

| \$f16\$f19                                          | Caller saved register                      |

| \$f20\$f31                                          | Callee saved registers                     |

Table 2.3: Register usage for parameter passing.

| Values          | Register Usage                                                                     |

|-----------------|------------------------------------------------------------------------------------|

| f1, f2,         | $f1 \rightarrow \$f12, f2 \rightarrow \$f14$                                       |

| f1, i1, f2,     | $f1 \rightarrow \$f12, i1 \rightarrow \$6, f2 \rightarrow stack$                   |

| f1, i1, i2,     | $f1 \rightarrow \$f12, i1 \rightarrow \$6, i2 \rightarrow \$7$                     |

| i1, i2, i3, i4, | $i1 \to \$4, i2 \to \$5, i3 \to \$6, i4 \to \$7$                                   |

| i1, i2, i3, f1, | $i1 \rightarrow \$4, i2 \rightarrow \$5, i3 \rightarrow \$6, f1 \rightarrow stack$ |

| i1, i2, f1,     | $i1 \to \$4, i2 \to \$5, f1 \to (\$6,\$7)$                                         |

| i1, f1,         | $i1 \to \$4, f1 \to (\$6,\$7)$                                                     |

- 1. All integer parameters are passed in the integer registers in order.

- Double-precision floating-point values have to be passed in integer registers if any integer parameter comes before it; otherwise, it is passed in double floating-point registers.

- 3. Double-precision floating-point values must be aligned to even numbered registers.

This applies to either integer or double floating-point registers.

- 4. If an integer register is skipped over because of the alignment problem, then it cannot be used for parameter passing.

- 5. Any parameters that cannot fit in the registers are passed on the stack.

#### 2.3 Data Generation

It is important to place the global variables in the right section of the data memory since MIPS has the 16-bit and 32-bit data addressing features. Thus far, LCODE is unable to provide enough information in its data structures as to intelligently guide the code generator to efficiently allocate the small data memory space. All the variables are generated in the data memory, and it is up to the MIPS assembler to move the variables to the small data memory. This is done by assembling the entire program in one command line.

The MIPS assembler cannot handle long algebraic expressions. The IMPCC/MIPS code generator is required to reduce the algebraic expressions that contain labels into a minimal format. For example, we are given the following C declaration statement.

int

$$p5 = &(p3[2]) - p3;$$

In LCODE, this statement is in this form.

The IMPCC/MIPS code generator reduces the LCODE data declaration statement into one simple form.

\$p5:

.word 2

where \$p5 is the address label of the variable.

#### 2.4 Instruction Selection

The first major step in the IMPCC/MIPS code generation is the mapping of each LCODE instruction into the appropriate MIPS assembly instruction. LCODE is broken down into six groups of instruction types: macro, branch, arithmetic, move, type conversion, and load/store. For some of the instruction groups, further distinctions between integer, floating-point, and double floating-point instruction types are made. For these instruction groups, tables are constructed to show the instruction mapping of each LCODE instruction to MIPS assembly instruction. The *LCODE* column gives the LCODE instruction. The *MIPS Code* column gives the equivalent MIPS assembly instruction or MIPS assembly instruction sequences. A branch instruction with an fs attached to it is the forward semantic version of that branch instruction. Forward semantic is used to indicate that the instruction is a likely taken branch.

Table 2.4 shows some LCODE assembly macros. For the jsr and the  $jsr\_fs$  instructions, function pertains to the callee function name. But sometimes in the language C, we can call a function through a pointer. If this happens, function would pertain to a register whose content holds the address of the callee function. The register \$31 is the linkage register, or better known as the return address register. The prologue and

Table 2.4: LCODE assembly macros.

| LCODE    | MIPS Code                  |

|----------|----------------------------|

| jsr      | jal function               |

| jsr_fs   | jal function               |

| rts      | j \$31                     |

| rts_fs   | j \$31                     |

| prologue | (variable)                 |

| epilogue | (variable)                 |

| define   | (ignored)                  |

| alloc    | addu \$2, \$29, structsize |

| nop      | nop                        |

epilogue instructions translate to none or many MIPS assembly instructions depending upon the function. The roles of prologue and epilogue instructions are to set the stack pointer (\$29) for the current function, and to store and load callee saved registers on and from the stack. Define is for the internal use of the code generator, and does not generate any equivalent MIPS assembly instruction. Alloc allocates a portion of stack space for a structure that is the size of structsize in number of bytes. The register \$2 contains the beginning address of that structure, and \$2 is passed to the callee function, which will return a structure on the stack space provided.

Tables 2.5 to 2.7 give the LCODE branch instruction mappings. MIPS has no equivalent instruction for the floating-point branch instructions. For these branch instructions, two MIPS assembly instructions are required for one LCODE instruction. The first MIPS assembly instruction compares the two operands, and the second MIPS assembly instruction determines the branch direction depending on the result of the comparison.

Tables 2.8 to 2.10 give the LCODE arithmetic instruction mappings. For the integer arithmetic instructions, only *nand* and *nxor* have no equivalent MIPS assembly instruction. Each floating-point compare and set instruction requires at least four MIPS

Table 2.5: LCODE integer branch instructions.

| LCODE      | MIPS Code |

|------------|-----------|

| jump       | b         |

| jump_fs    | b         |

| jump_rg    | j         |

| jump_rg_fs | j         |

| beq        | beq       |

| beq_fs     | beq       |

| bne        | bne       |

| bne_fs     | bne       |

| bgt        | bgt       |

| bgt_fs     | bgt       |

| bge        | bge       |

| bge_fs     | bge       |

| blt        | blt       |

| blt_fs     | blt       |

| ble        | ble       |

| ble_fs     | ble       |

| bgt_u      | bgtu      |

| bgt_u_fs   | bgtu      |

| bge_u      | bgeu      |

| bge_u_fs   | bgeu      |

| blt_u      | bltu      |

| blt_u_fs   | bltu      |

| ble_u      | bleu      |

| ble_u_fs   | bleu      |

|            |           |

Table 2.6: LCODE single-precision floating-point branch instructions.

| $MIPS\ Code$ |

|--------------|

| c.eq.s       |

| bc1t         |

| c.eq.s       |

| bc1t         |

| c.eq.s       |

| bclf         |

| c.eq.s       |

| bclf         |

| c.le.s       |

| bc1f         |

| c.le.s       |

| bc1f         |

| c.lt.s       |

| bc1f         |

| c.lt.s       |

| bc1f         |

| c.lt.s       |

| bc1t         |

| c.lt.s       |

| bc1t         |

| c.le.s       |

| bc1t         |

| c.le.s       |

| bc1t         |

|              |

Table 2.7: LCODE double-precision floating-point branch instructions.

| LCODE           | $MIPS\ Code$      |

|-----------------|-------------------|

| beq_f2          | c.eq.d            |

|                 | bc1t              |

| beq_f2_fs       | c.eq.d            |

|                 | bc1t              |

| bne_f2          | c.eq.d            |

|                 | bclf              |

| bne_f2_fs       | c.eq.d            |

|                 | bclf              |

| bgt_f2          | c.le.d            |

|                 | bc1f              |

| bgt_f2_fs       | c.le.d            |

|                 | bc1f              |

| bge <b>_</b> f2 | $\mathrm{c.lt.d}$ |

|                 | bc1f              |

| bge_f2_fs       | c.lt.d            |

|                 | bc1f              |

| blt_f2          | c.lt.d            |

|                 | bc1t              |

| $blt_f2_fs$     | $\mathrm{c.lt.d}$ |

|                 | bc1t              |

| ble_f2          | c.le.d            |

|                 | bc1t              |

| ble_f2_fs       | c.le.d            |

|                 | bc1t              |

Table 2.8: LCODE integer arithmetic instructions.

| rem rem rem_u remu add addu add_u addu sub subu sub_u subu mul mul mul_u mul div div div_u divu abs abs or or nor nor and and nand and not xor xor nxor xor nxor xor not eq seq ne sne gt sgt gt_u sgtu ge sge ge_u sgeu lt slt lt_u sltu le sle                                                                                                                                                                                                                                  | rem_u         readd           add_u         add           add_u         add           sub         su           sub_u         su           mul         m           mul_u         m           div_div_u         di           div_u         di           abs         al           or         or           nor         no           and         an           nor         no           and         an           nor         no           eq         se           ne         sr           gt_u         sg           gt_u         sg           ge_u         sg           ge_u         sg           ge_u         sg           ge_u         sg           lt_u         sl           le_u         sl           le_u         sl                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | IIPS Code |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------|

| add addu add_u addu sub subu sub_u subu mul mul mul_u mul div div div_u divu abs abs or or nor nor nor and and not xor xor nxor xor nxor xor not eq seq ne sne gt sgt gt_u sgtu ge sge ge_u sgeu lt slt_u sltu                                                                                                                                                                                                                                                                    | add         ad           add_u         ad           sub         su           sub_u         su           mul         m           mul_u         m           div_div         di           div_u         di           abs         al           or         or           nor         no           and         an           nor         no           and         an           nor         no           xor         xo           nxor         xo           nc         se           gt         sg           gt_u         sg           ge_u         sg           ge_u         sg           ge_u         sg           lt_u         sl           le_u         sl           le_u         sl           lsl         sl                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | em        |

| add_u addu sub subu sub_u subu mul mul mul_u mul div div div_u divu abs abs or or nor nor and and nand and not xor xor nxor xor not eq seq ne sne gt sgt gt_u sgtu ge sge ge_u sgeu lt slt_u sltu                                                                                                                                                                                                                                                                                 | add_u         ad           sub         su           sub_u         su           mul         m           mul_u         m           div_div_u         di           abs         al           or         or           nor         no           and         an           nand         an           nxor         xo           nxor         xo           ne         sr           gt_u         sg           gt_u         sg           ge_u         sg           ge_u         sg           ge_u         sg           lt_u         sl           le_u         sl           le_u         sl           lsl         sl                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | emu       |

| sub subu sub_u subu mul mul mul_u mul div div div_u divu abs abs or or nor nor nor and and not xor xor nxor xor not eq seq ne sne gt sgt gt_u sgtu ge sge ge_u sgeu lt slt_u sltu                                                                                                                                                                                                                                                                                                 | sub         su           sub_u         su           mul         m           mul_u         m           div_u         di           div_u         di           abs         al           or         or           nor         no           and         an           nor         no           and         an           nor         xo           nxor         xo           nxor         xo           nxor         xo           nc         sr           gt         sg           gt_u         sg           ge_u         sg           ge_u         sg           ge_u         sg           lt         sl           le_u         sl           le_u         sl           lsl         sl                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | ddu       |

| sub_u subu mul mul mul_u mul div div div_u divu abs abs or or or nor nor and and nand and not xor xor nxor xor not eq seq ne sne gt sgt gt_u sgtu ge sge ge_u sgeu lt slt_u sltu                                                                                                                                                                                                                                                                                                  | sub_u         sub_u           mul         m           mul_u         m           div_u         di           abs         al           or         or           nor         no           and         ar           nand         ar           nxor         xo           nxor         xo           nc         sr           gt         sg           gt_u         sg           ge_u         sg           ge_u         sg           lt         sl           le_u         sl           le_u         sl           lsl         sl                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | ddu       |

| mul mul mul_u mul div div div_u divu abs abs or or or nor nor and and nand and not xor xor nxor xor not eq seq ne sne gt sgt gt_u sgtu ge sge ge_u sgeu lt slt_u sltu                                                                                                                                                                                                                                                                                                             | mul         m           mul_u         m           div_u         di           div_u         di           abs         al           or         or           nor         no           and         an           nand         an           no         xor           xor         xo           nxor         xo           nc         sr           gt_u         sg           gt_u         sg           ge_u         sg           ge_u         sg           lt_u         sl           le_u         sl           le_u         sl           lsl         sl                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | ıbu       |

| mul_u         mul           div         div           div_u         divu           abs         abs           or         or           nor         nor           and         and           nand         and           not         xor           nxor         xor           not         seq           ne         sne           gt         sgt           gt_u         sgtu           ge         sge           ge_u         sgeu           lt         slt           lt_u         sltu  | mul_u         m           div_u         di           abs         al           or         or           nor         or           nor         no           and         ar           nand         ar           nxor         xo           nxor         xo           nc         sr           gt         sg           gt_u         sg           ge_u         sg           ge_u         sg           lt         sl           le_u         sl           le_u         sl           lsl         sl                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | ıbu       |

| div         div           div_u         divu           abs         abs           or         or           nor         nor           and         and           nand         and           not         xor           nxor         xor           nxor         xor           not         seq           ne         sne           gt         sgt           gt_u         sgtu           ge         sge           ge_u         sgeu           lt_u         slt           lt_u         sltu | div         di           div_u         di           abs         al           or         or           nor         no           nor         no           and         an           nand         an           nand         an           no         xo           nxor         xo           nc         sr           gt         sg           gt_u         sg           ge_u         sg           ge_u         sg           ge_u         sg           lt_u         sl           le_u         sl           le_u         sl           lsl         sl                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | nul       |

| div_u         divu           abs         abs           or         or           nor         nor           and         and           nand         not           xor         xor           nxor         xor           not         seq           ne         sne           gt         sgt           gt_u         sgtu           ge         sge           ge_u         sgeu           lt         slt           lt_u         sltu                                                        | div_u         di           abs         al           or         or           nor         or           nor         or           nor         no           and         an           nand         an           xor         xo           nxor         xo           nc         nc           gt         sg           gt_u         sg           ge_u         sg           ge_u         sg           ge_u         sg           lt         sl           le_u         sl           le_u         sl           lsl         sl                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |           |

| abs abs or or nor or nor and and nand and not xor xor nxor xor not eq seq ne sne gt sgt gt_u sgtu ge sge ge_u sgeu lt slt_u sltu                                                                                                                                                                                                                                                                                                                                                  | abs         al           or         or           nor         or           nor         or           nor         or           and         an           nand         an           nor         xo           nxor         xo           nxor         xo           nxor         xo           nxor         xo           nc         sr           gt         sg           gt_u         sg           ge_u         sg           ge_u         sg           lt         sl           le_u         sl           lsl         sl                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |           |

| or         or           nor         nor           and         and           nand         not           xor         xor           nxor         xor           not         eq           seq         se           ne         sne           gt         sgt           gt_u         sgtu           ge         sge           ge_u         sgeu           lt         slt           lt_u         sltu                                                                                       | or on nor nor nor nor nor nor nor nor no                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |           |

| nor         nor           and         and           nand         and           not         xor           nxor         xor           not         eq           eq         seq           ne         sne           gt         sgt           gt_u         sgtu           ge         sge           ge_u         sgeu           lt         slt           lt_u         sltu                                                                                                               | nor no no and an nand  | os        |

| and and not not xor xor xor not eq seq ne sne gt sgt u sgt u ge sge u lt slt lt_u sltu                                                                                                                                                                                                                                                                                                                                                                                            | and an nand an | r         |

| nand and not xor xor xor not eq seq set sgt gt_u sgtu ge sge ge_u sgeu lt slt_u sltu                                                                                                                                                                                                                                                                                                                                                                                              | nand         an           xor         xo           nxor         xo           nxor         xo           eq         se           ne         sr           gt         sg           gt_u         sg           ge_u         sg           ge_u         sg           lt         sl           le_u         sl           lsl         sl                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | or        |

| xor         xor           nxor         xor           nxor         xor           not         seq           ne         sne           gt         sgt           gt_u         sgtu           ge         sge           ge_u         sgeu           lt         slt           lt_u         sltu                                                                                                                                                                                           | Nor    | nd        |

| xor         xor           nxor         xor           not         eq           eq         seq           ne         sne           gt         sgt           gt_u         sgtu           ge         sge           ge_u         sgeu           lt         slt           lt_u         sltu                                                                                                                                                                                              | xor         xor           nxor         xor           nxor         xor           eq         se           ne         sr           gt         sg           gt_u         sg           ge         sg           ge_u         sg           lt         sl           lt_u         sl           le_u         sl           lsl         sl                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | nd        |

| nxor         xor           eq         seq           ne         sne           gt         sgt           gt_u         sgtu           ge         sge           ge_u         sgeu           lt         slt           lt_u         sltu                                                                                                                                                                                                                                                 | nxor         xo           eq         se           ne         sr           gt         sg           gt_u         sg           ge_u         sg           lt         sl           lt_u         sl           le_u         sl           lsl         sl                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | ot        |

| not           eq         seq           ne         sne           gt         sgt           gt_u         sgtu           ge         sge           ge_u         sgeu           lt         slt           lt_u         sltu                                                                                                                                                                                                                                                              | eq se                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | or        |

| eq         seq           ne         sne           gt         sgt           gt_u         sgtu           ge         sge           ge_u         sgeu           lt         slt           lt_u         sltu                                                                                                                                                                                                                                                                            | eq se<br>ne sr<br>gt sg<br>gt_u sg<br>ge sg<br>ge_u sg<br>lt sl<br>lt_u sl<br>le sl<br>lsl sl                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | or        |

| ne         sne           gt         sgt           gt_u         sgtu           ge         sge           ge_u         sgeu           lt         slt           lt_u         sltu                                                                                                                                                                                                                                                                                                     | ne         sr           gt         sg           gt_u         sg           ge         sg           ge_u         sg           lt         sl           lt_u         sl           le_u         sl           lsl         sl                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | ot        |

| gt         sgt           gt_u         sgtu           ge         sge           ge_u         sgeu           lt         slt           lt_u         sltu                                                                                                                                                                                                                                                                                                                              | gt         sg           gt_u         sg           ge         sg           ge_u         sg           lt         sl           lt_u         sl           le         sl           le_u         sl           lsl         sl                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | eq        |

| gt_u         sgtu           ge         sge           ge_u         sgeu           lt         slt           lt_u         sltu                                                                                                                                                                                                                                                                                                                                                       | gt_u       sg         ge       sg         ge_u       sg         lt       sl         lt_u       sl         le_u       sl         lsl       sl                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |           |