# MEMORY DISAMBIGUATION TO FACILITATE INSTRUCTION-LEVEL PARALLELISM COMPILATION

## BY

## DAVID MARK GALLAGHER

B.S., United States Air Force Academy, 1978M.S., Air Force Institute of Technology, 1987

#### THESIS

Submitted in partial fulfillment of the requirements for the degree of Doctor of Philosophy in Electrical Engineering in the Graduate College of the University of Illinois at Urbana-Champaign, 1995

Urbana, Illinois

# MEMORY DISAMBIGUATION TO FACILITATE INSTRUCTION-LEVEL PARALLELISM COMPILATION

David Mark Gallagher, Ph.D.

Department of Electrical and Computer Engineering

University of Illinois at Urbana-Champaign, 1995

Wen-mei W. Hwu, Advisor

To expose sufficient instruction-level parallelism (ILP) to make effective use of wide-issue superscalar and VLIW processor resources, the compiler must perform aggressive low-level code optimization and scheduling. However, ambiguous memory dependences can significantly limit the compiler's ability to expose ILP. To overcome the problem of ambiguous memory dependences, optimizing compilers perform memory disambiguation.

Both dynamic and static approaches to memory disambiguation have been proposed. Dynamic memory disambiguation approaches resolve the dependence ambiguity at run-time. Compiler transformations are performed which provide alternate paths of control to be followed based upon the results of this run-time ambiguity check. In contrast, static memory disambiguation attempts to resolve ambiguities during compilation. Compiler transformations can be performed based upon the results of this disambiguation, with no run-time checking required.

This dissertation investigates the application of both dynamic and static memory disambiguation approaches to support low-level optimization and scheduling. A dynamic approach, the memory conflict buffer, originally proposed by Chen [1], is analyzed across a large suite of integer and floating-point benchmarks. A new static approach, termed sync arcs, involving the passing of explicit dependence arcs from the source-level code down to the low-level code, is proposed and evaluated. This investigation of both dynamic and static memory disambiguation allows a quantitative analysis of the tradeoffs between the two approaches.

# **DEDICATION**

To my wife, Kathy, and my children, Jonathan and Daniel.

${\it Thank you for your love, support and long suffering!}$

#### ACKNOWLEDGMENTS

First and foremost, I would like to thank God for the opportunity, ability, and strength to complete a doctoral program. To Him be all the glory!

I would like to thank my advisor, Professor Wen-mei W. Hwu, for his insight and guidance throughout my studies. Not only was it an honor to work with someone of his caliber, but it was also a pleasure. He truly cares about the needs of his students.

This research would not have been possible without the support of the IMPACT research group. Their efforts provided a unique compilation environment in which to conduct my research. The group also provided a very enjoyable work atmosphere. Members of the group were always willing to provide any help required - from research discussions to practice talks to listening to my frustrations. I deeply appreciate the willingness of Scott Mahlke and Rick Hank to answer my innumerable questions about Lcode and to act as a sounding board for my ideas. Grant Haab spent a great deal of time introducing me to the Pcode environment; he was also responsible for the Pcode data dependence which laid the foundation for much of my work. John Gyllenhaal was responsible for much of the simulation environment used in this thesis. William Chen provided me with my first introduction to IMPACT and to dynamic memory disambiguation. Many thanks to Dan Lavery, Ben Sander, Wayne Dugal, Cheng-Hsueh Hsieh, Derek Cho, and others who worked hard on the IMPACT X86 project.

Thanks to Bob Rau, Mike Schlansker, Vinod Kathail, and Sadun Anik of HP Laboratory for their valuable discussions about static memory disambiguation. Their technical ability and insight across the entire spectrum of computer architecture are remarkable.

I would like to thank my parents, Gilbert and Billye, for their continued love and encouragement. They provided a firm foundation for me both spiritually and emotionally as a child; as an adult, they continue to act as a source of strength and stability in my life. I also thank my brother, Steven, for his love and patience with his little brother.

Finally, I must thank my wife, Kathy, and my children, Jonathan and Daniel, for their love and support during this difficult time in graduate school. They are the ones who truly sacrificed to make my graduate studies possible. Kathy single-handedly maintained our household, chasing the boys from one activity to another, so that I could spend time on my research. Jonathan and Daniel have been very understanding during the many times Dad couldn't be there for a school or sports activity. Thanks, and I plan to do better in the future!

# TABLE OF CONTENTS

| CI | НАРТ       | TER                                                   | PAGE |

|----|------------|-------------------------------------------------------|------|

| 1  | INT<br>1.1 | RODUCTION                                             |      |

|    | 1.2        | Overview                                              | . 4  |

| 2  | CON        | MPILATION AND SIMULATION ENVIRONMENT                  | . 6  |

| _  | 2.1        | Pcode                                                 |      |

|    | 2.2        | Lcode                                                 |      |

|    | 2.3        | Superblocks                                           |      |

|    | 2.4        | IMPACT Simulation Environment                         |      |

| 3  | OVE        | ERVIEW OF MEMORY DISAMBIGUATION                       | . 18 |

| Ĭ  | 3.1        | Tradeoffs Between Dynamic and Static Approaches       |      |

|    | 3.2        | Dynamic Memory Disambiguation Approaches              |      |

|    |            | 3.2.1 Run-time disambiguation                         |      |

|    |            | 3.2.2 Preload register update                         | . 29 |

|    |            | 3.2.3 HP smart load                                   |      |

|    |            | 3.2.4 Speculative disambiguation                      | . 31 |

|    |            | 3.2.5 Unsafe loads                                    |      |

|    |            | 3.2.6 Hardware-only disambiguation                    | . 34 |

|    | 3.3        | Static Memory Disambiguation Approaches               | . 35 |

| 4  | DYN        | NAMIC MEMORY DISAMBIGUATION USING THE MEMORY CONFLICT |      |

|    | BUF        | FER                                                   | . 38 |

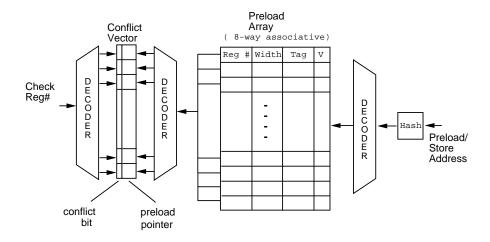

|    | 4.1        | Architectural Support                                 | . 40 |

|    |            | 4.1.1 MCB design                                      | . 40 |

|    |            | 4.1.2 MCB address hashing                             | . 45 |

|    |            | 4.1.3 Handling variable access sizes                  |      |

|    |            | 4.1.4 Handling context switches                       |      |

|    |            | 4.1.5 Speculative execution                           |      |

|    |            | 4.1.6 Discussion of hardware requirements             |      |

|    | 4.2        | Compiler Support                                      |      |

|    |            | 4.2.1 Basic MCB scheduling algorithm                  |      |

|    |            | 4.2.2 Inserting correction code                       |      |

|    | 4.3        | Experimental Evaluation                               |      |

|    |            | 4.3.1 MCB emulation                                   |      |

|    |            | 4.3.2 MCB size and associativity                      |      |

|    |            | 4.3.3 Signature field size                            |      |

|    |            | 4.3.4 MCB performance                                 |      |

|    |            | 4.3.5 Reducing MCB conflicts                          |      |

|    | 4 4        | MCB Summary                                           | 74   |

| 5 | STATIC MEMORY DISAMBIGUATION USING SYNC ARCS                 |  |

|---|--------------------------------------------------------------|--|

|   | 5.1 Providing Source Information to the Intermediate Code    |  |

|   | 5.1.1 Performing static analysis on low-level code           |  |

|   | 5.1.2 Performing static analysis on source-level code        |  |

|   | 5.2 Sync Arcs                                                |  |

|   | 5.2.1 Desired dependence information                         |  |

|   | 5.2.2 Extracting sync arcs                                   |  |

|   | 5.2.3 Maintaining sync arcs                                  |  |

|   | 5.2.4 Limiting the number of sync arcs                       |  |

|   | 5.2.5 Using sync arcs                                        |  |

|   | 5.3 Sync Arc Summary                                         |  |

| 6 | C DEPENDENCE ANALYSIS TO GENERATE SYNC ARCS                  |  |

| U | 6.1 Dependence Analysis for C Programs                       |  |

|   | 6.1.1 Semantic differences                                   |  |

|   | 6.1.2 Required modifications to existing dependence analysis |  |

|   | 6.2 Interprocedural Analysis for C Programs                  |  |

|   | 6.2.1 Granularity of analysis                                |  |

|   | 6.2.2 Building the program call graph                        |  |

|   | 6.2.3 Implementation                                         |  |

|   | 6.3 Dependence Analysis Summary                              |  |

|   |                                                              |  |

| 7 | EXPERIMENTAL RESULTS                                         |  |

|   | 7.1 Sync Arcs                                                |  |

|   | 7.1.1 Integer benchmarks                                     |  |

|   | 7.1.2 Floating-point benchmarks                              |  |

|   | 7.2 Comparison of Static and Dynamic Approaches              |  |

|   | 7.2.1 Performance comparison                                 |  |

|   | 7.2.2 Synergy of the approaches                              |  |

|   | 7.3 Summary of Results                                       |  |

| 8 | CONCLUSIONS                                                  |  |

|   | 8.1 Summary                                                  |  |

|   | 8.2 Future Work                                              |  |

|   | REFERENCES                                                   |  |

|   | VITA                                                         |  |

|   | 1.71                                                         |  |

# LIST OF TABLES

| Tab | Γable I                                                                                                      |  | Page |  |

|-----|--------------------------------------------------------------------------------------------------------------|--|------|--|

| 3.1 | Tradeoffs of Dynamic and Static Memory Disambiguation                                                        |  | 22   |  |

| 4.1 | Simulated Architecture                                                                                       |  |      |  |

| 4.2 | Instruction Latencies                                                                                        |  | 57   |  |

| 4.3 | MCB Conflict Statistics (8-issue architecture, 64 entries, 8-way set associative, 5 signature bits)          |  | 68   |  |

| 4.4 | MCB Static and Dynamic Code Size (8-issue architecture, 64 entries, 8-way set associative, 5 signature bits) |  | 70   |  |

| 5.1 | Desired Dependence Information                                                                               |  | 86   |  |

| 6.1 | Access Table Names.                                                                                          |  | 106  |  |

| 6.2 | Rules for Determining if an Operator Corresponds to an Access                                                |  | 111  |  |

| 7.1 | Number of Functional Units                                                                                   |  | 135  |  |

# LIST OF FIGURES

| Figu | ire                                                                                | Page |

|------|------------------------------------------------------------------------------------|------|

| 1.1  | Importance of Memory Disambiguation.                                               | . 2  |

| 2.1  | The IMPACT Compiler                                                                | . 7  |

| 2.2  | An Example of Superblock Formation                                                 |      |

| 2.3  | MCB Compilation Path for Simulation                                                |      |

| 3.1  | Effect of Memory Disambiguation on Performance.                                    | . 21 |

| 3.2  | Limitations of Static Memory Disambiguation                                        | . 23 |

| 3.3  | Run-time Memory Disambiguation Example                                             | . 27 |

| 3.4  | Preload Register Update Example.                                                   | . 30 |

| 3.5  | Speculative Disambiguation Example                                                 | . 32 |

| 4.1  | Memory Conflict Buffer Example                                                     | . 39 |

| 4.2  | Set Associative MCB Design.                                                        | . 42 |

| 4.3  | Hashing MCB Array Entry                                                            | . 48 |

| 4.4  | Speculative Execution of Excepting Instructions                                    | . 50 |

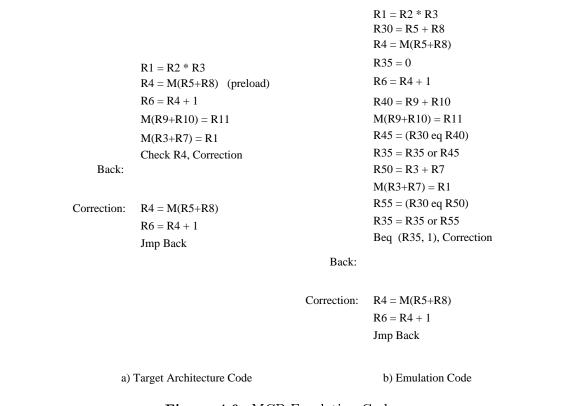

| 4.5  | MCB Code Compilation                                                               | . 53 |

| 4.6  | MCB Emulation Code                                                                 | . 58 |

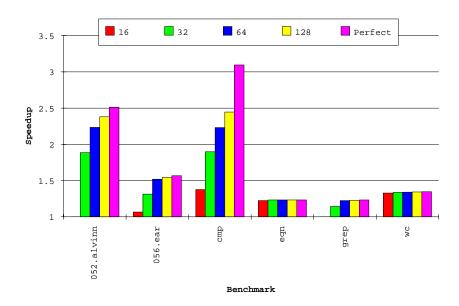

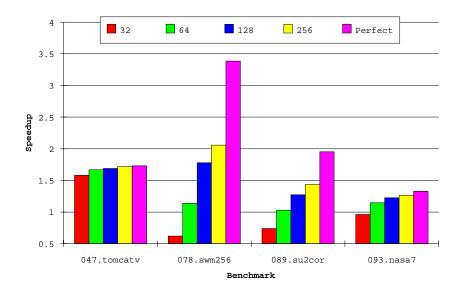

| 4.7  | MCB Size Evaluation. Speedup of an 8-issue architecture for various size MCBs vs.  |      |

|      | an 8-issue architecture without MCB (8-way set associative, 5 signature bits)      | . 60 |

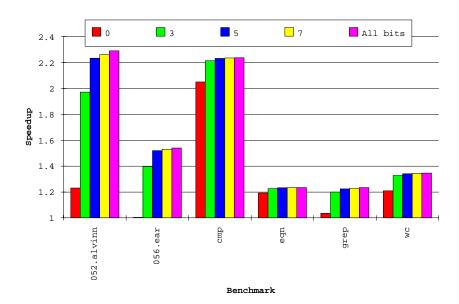

| 4.8  | MCB Signature Size. Speedup of an 8-issue architecture with various size address   |      |

|      | signature fields vs. an 8-issue architecture without MCB (8-way set associative, 5 |      |

|      | signature bits).                                                                   | . 61 |

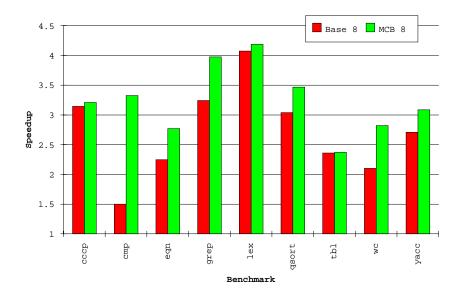

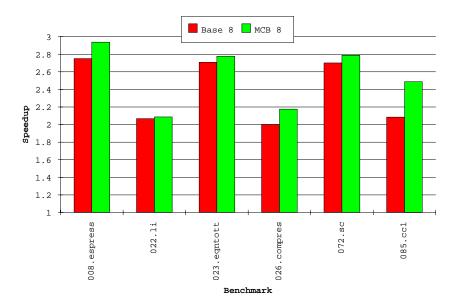

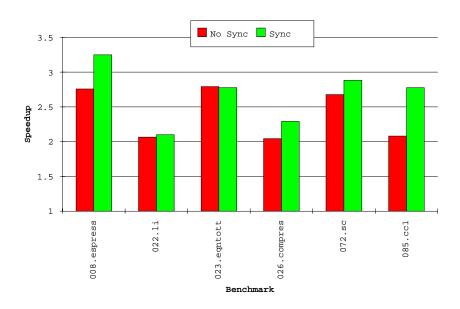

| 4.9  | Unix MCB 8-Issue Results. Speedup of code compiled with and without MCB over       |      |

|      | a baseline single-issue architecture.                                              | . 62 |

| 4.10 | SPEC-CINT92 MCB 8-Issue Results. Speedup of code compiled with and without         |      |

|      | MCB over a baseline single-issue architecture.                                     | . 63 |

| 4.11 | Unix MCB 8-Issue Results. Speedup of code compiled with MCB over an 8-issue        |      |

|      | architecture without MCB.                                                          | . 64 |

| 4.12 | SPEC-CINT92 MCB 8-Issue Results. Speedup of code compiled with MCB over an         |      |

|      | 8-issue architecture without MCB                                                   | . 64 |

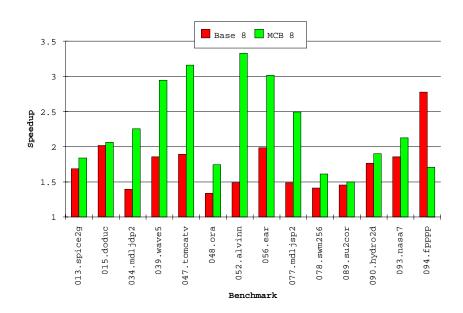

| 4.13 | SPEC-CFP92 MCB 8-Issue Results. Speedup of code compiled with and without          |      |

|      | MCB over a baseline single-issue architecture.                                     | . 66 |

| 4.14 | SPEC-CFP92 MCB 8-Issue Results. Speedup of code compiled with MCB over an          |      |

|      | 8-issue architecture without MCB                                                   | . 66 |

| 4.15 | Floating-Point MCB Size Evaluation. Speedup of an 8-issue architecture for vari-   |      |

|      | ous size MCBs vs. an 8-issue architecture without MCB (8-way set associative, 5    |      |

|      | signature bits).                                                                   | . 72 |

| 4.16 | 8-Issue Results for Different MCB Models                                           |      |

| 5.1  | Difficulty of Memory Disambiguation for Low-Level Code        |

|------|---------------------------------------------------------------|

| 5.2  | Dependence Information to Support Loop Unrolling              |

| 5.3  | Dependence Information to Support Loop Invariant Code Removal |

| 5.4  | Dependence Information to Support Redundant Load Elimination  |

| 5.5  | Single Iteration Dependence Example                           |

| 5.6  | Threshold Dependence Distance Example                         |

| 5.7  | Sync Arc Format                                               |

| 5.8  | Inlining Code with Sync Arcs                                  |

| 5.9  | Updating Sync Arcs for Code Motion                            |

| 5.10 | Updating Sync Arcs for Loop Unrolling                         |

| 5.11 | Address-Based Versus Flow-Based Analysis                      |

| 6.1  | Finding Memory References                                     |

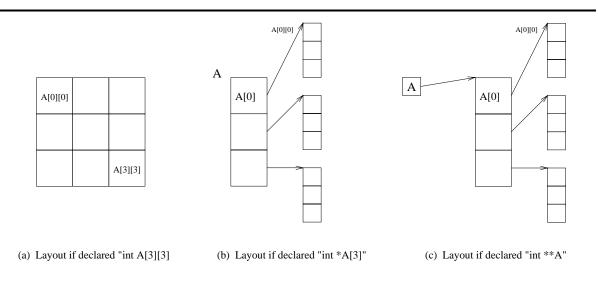

| 6.2  | Different Structures Based Upon Data Declaration              |

| 6.3  | Accuracy Loss of Low-Granularity Interprocedural Analysis     |

| 6.4  | Interprocedural Function Pointers                             |

| 6.5  | Indirect Function Calls Through Library Functions             |

| 6.6  | Phases of Interprocedural Analysis                            |

| 6.7  | Aliases Created by Binding                                    |

| 6.8  | Side effects on Function Pointer Arguments                    |

| 6.9  | Propagation of Side effects on Formal Parameters              |

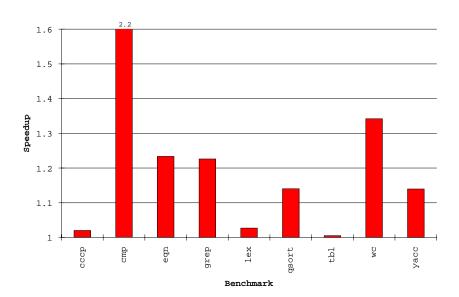

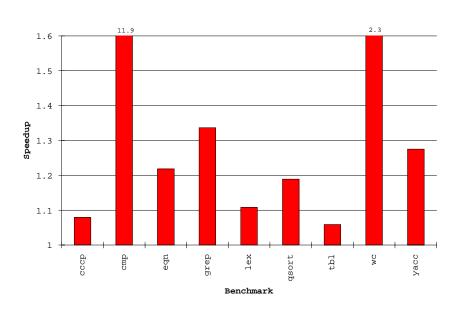

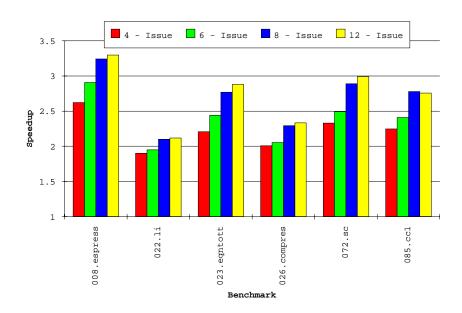

| 7.1  | Sync Arc 8-Issue Unix Results                                 |

| 7.2  | Sync Arc 8-Issue SPEC-CINT92 Results                          |

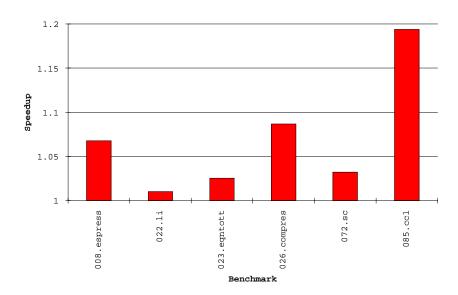

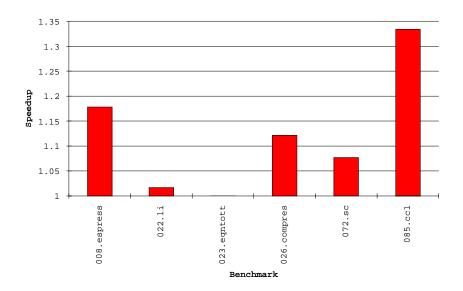

| 7.3  | Sync Arc 8-Issue Unix Ratios                                  |

| 7.4  | Sync Arc 8-Issue SPEC-CINT92 Ratios                           |

| 7.5  | Source Code for Inner Loop of cmp                             |

| 7.6  | Lcode for Inner Loop of $cmp$                                 |

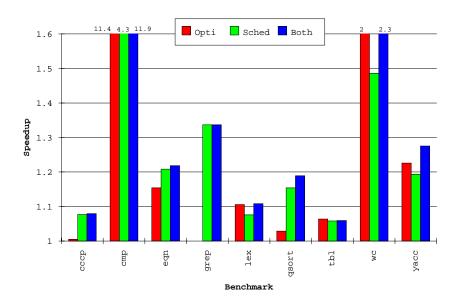

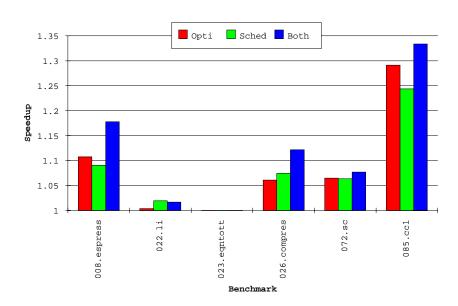

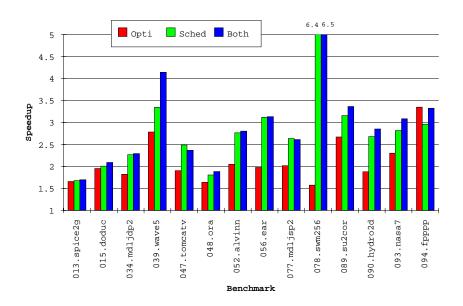

| 7.7  | Sync Arc 8-Issue Unix Optimization Versus Scheduling          |

| 7.8  | Sync Arc 8-Issue SPEC-CINT92 Optimization Versus Scheduling   |

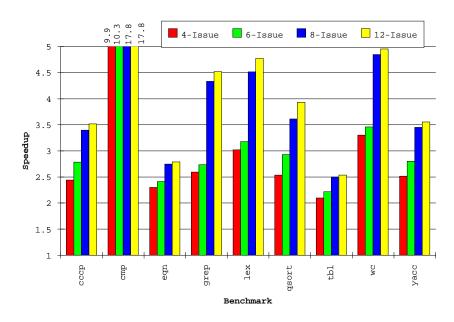

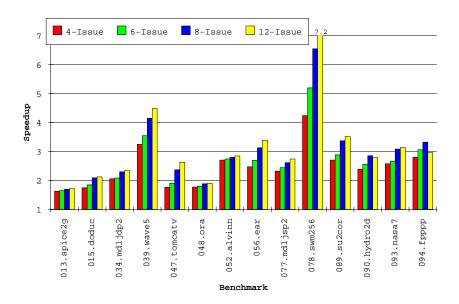

| 7.9  | Sync Arc Unix Results for Different Issue Rates               |

| 7.10 | Sync Arc SPEC-CINT92 Results for Different Issue Rates        |

| 7.11 | Effect of Interprocedural Analysis - Unix                     |

| 7.12 | Effect of Interprocedural Analysis - SPEC-CINT92              |

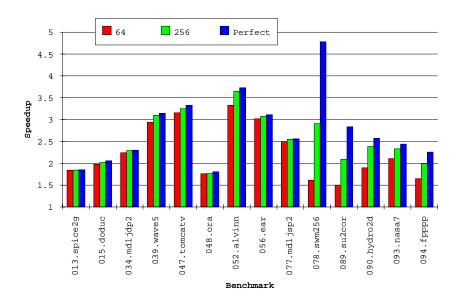

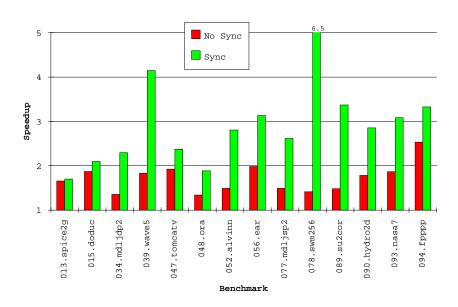

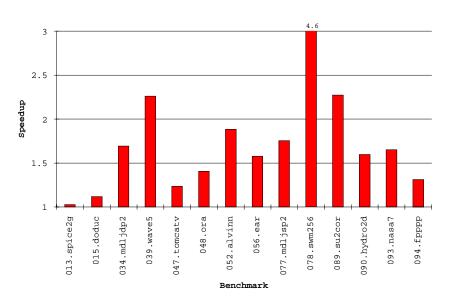

|      | Sync Arc 8-Issue SPEC-CFP92 Results                           |

| 7.14 | Sync Arc 8-Issue SPEC-CFP92 Ratios                            |

| 7.15 | Source Code for Inner Loop Nest of 078.swm256                 |

| 7.16 | Source Code from <i>056.ear</i>                               |

|      | Source Code from $013.spice2g6$                               |

| 7.18 | Sync Arc 8-Issue SPEC-CFP92 Optimization Versus Scheduling    |

| 7.19 | Sync Arc SPEC-CFP92 Results for Different Issue Rates         |

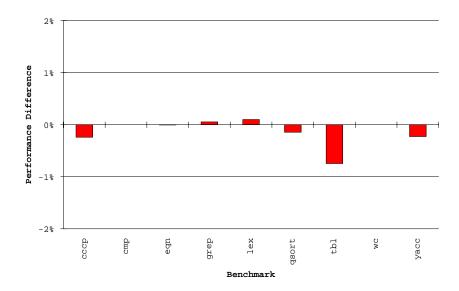

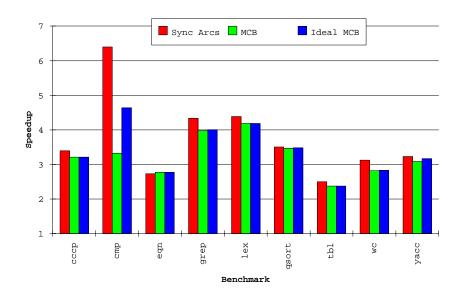

| 7.20 | Unix Comparison of Sync Arcs to MCB - 8-Issue                 |

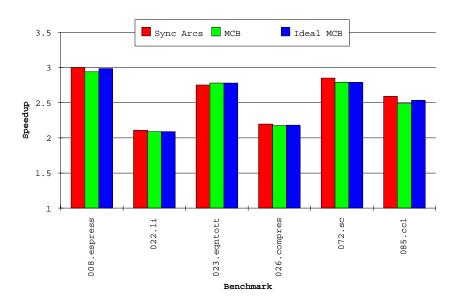

| 7.21 | SPEC-CINT92 Comparison of Sync Arcs to MCB - 8-Issue          |

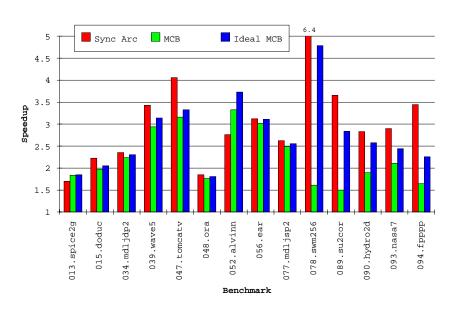

| 7.22 | SPEC-CFP92 Comparison of Sync Arcs to MCB - 8-Issue           |

| 7.23 | Source Code from 052.alvinn                                   |

#### CHAPTER 1

#### INTRODUCTION

Superscalar and VLIW processors attempt to achieve high performance by exploiting available instruction-level parallelism (ILP). The compiler is responsible for transforming the original program to expose sufficient ILP to keep the processor's functional units busy. This task of exposing parallelism requires aggressive low-level code optimization and scheduling.

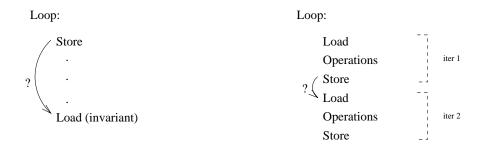

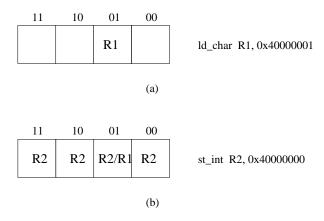

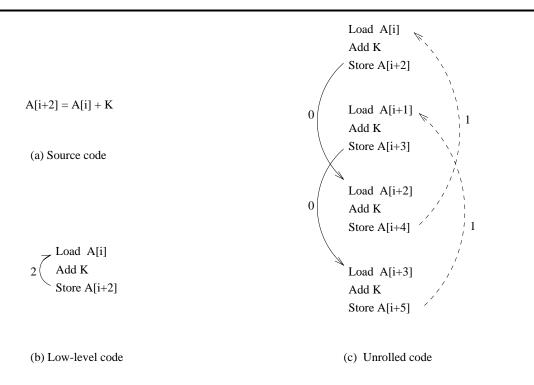

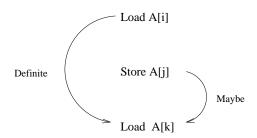

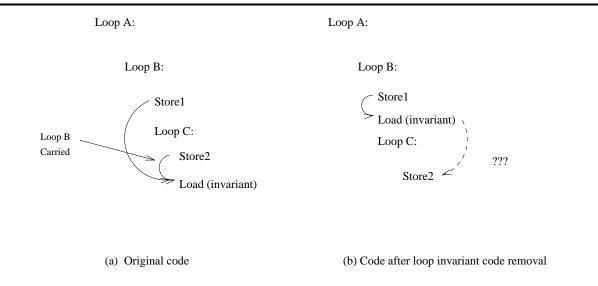

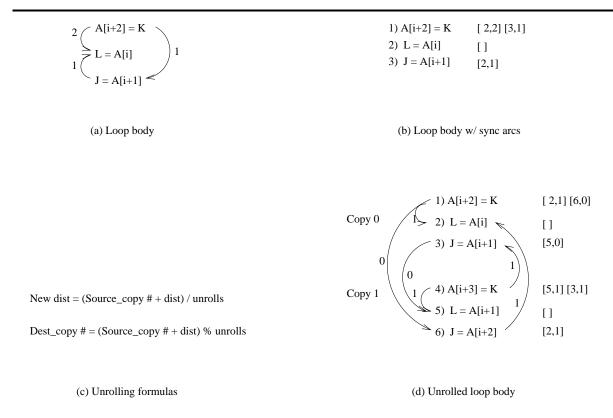

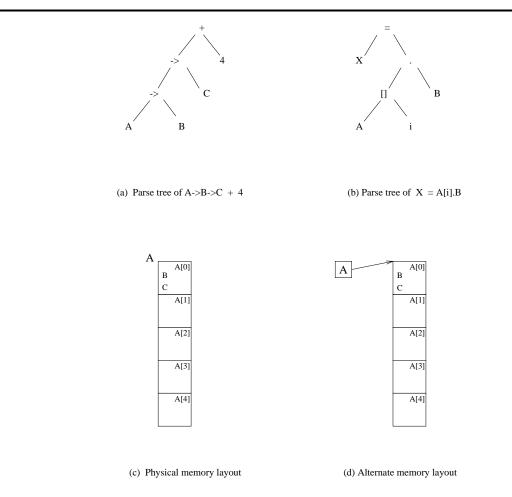

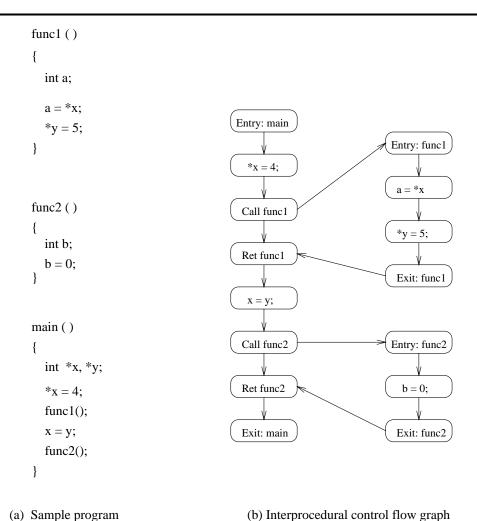

A major impediment to exploiting ILP is ambiguous memory dependences. When two memory instructions (e.g., a load and a store) may possibly reference the same memory location, the two instructions have an ambiguous memory dependence between them. As a result of this dependence, the compiler must ensure that the memory operations are executed in the original program order. Any code transformation that would alter the order of execution is prevented. Figure 1.1 shows two examples of how ILP compilation is hindered by ambiguous memory references. In Figure 1.1(a), the load address is assumed to be loop invariant (it references the same address during all iterations of the loop). However, loop invariant code removal cannot be performed to move the load out of the loop unless it can be determined the store instruction never writes to the same memory location as the load. The ambiguous memory dependence thus inhibits an important code optimization. In Figure 1.1(b), a simple loop, assumed to consist of a load instruction, several arithmetic instructions, and a store instruction, has been unrolled in an attempt to expose greater ILP to the scheduler. Again, if it cannot be determined that the store in the first iteration always references a different memory location than the load in second iteration, the two iterations cannot be overlapped and no additional ILP is achieved.

(a) Loop invariant code removal example

(b) Unrolling and scheduling example

Figure 1.1 Importance of Memory Disambiguation.

To overcome the problem of ambiguous memory dependences, optimizing compilers perform memory disambiguation, the process of determining whether two memory instructions might ever access the same location. Techniques for performing memory disambiguation generally are classified as either dynamic or static. Dynamic memory disambiguation determines at run-time whether two memory instructions ever reference the same location. To facilitate optimization or scheduling, the compiler provides different execution paths for the code depending upon whether the instructions are independent; at run-time, the dynamic memory disambiguation will determine which execution path is followed. In contrast, static memory disambiguation attempts to determine at compile-time the correct dependence relationship between memory disambiguation is successful in proving two memory instructions are independent, the compiler is able to perform optimization/scheduling at compile-time, and no run-time checking is required to ensure correct execution.

The potential benefit of dynamic and static memory disambiguation applied to low-level code optimization and scheduling has not been well-understood. Most existing dynamic memory disambiguation approaches are best suited for narrow-issue processors, and the benefit of

dynamic approaches for wide-issue superscalar or VLIW processors has not previously been demonstrated. Static memory disambiguation is most frequently applied to source-level code transformations, and its potential benefit for low-level code transformations has also not been demonstrated. Ideas for improved static disambiguation have been postulated, but few have actually been implemented in a working superscalar/VLIW compiler.

This dissertation examines both dynamic and static memory disambiguation approaches within the context of the IMPACT compiler project. Dynamic and static approaches have been implemented within the IMPACT compiler, targeted toward facilitating low-level code optimization and scheduling. Through detailed simulation, a quantitative analysis of both techniques is performed to better understand the merits of and tradeoffs between dynamic and static disambiguation.

## 1.1 Contributions

The four major contributions of this dissertation are discussed below.

• A dynamic memory disambiguation approach, the memory conflict buffer, is examined and developed. The memory conflict buffer is shown to be an effective means of overcoming the problem of ambiguous memory dependences, particularly for applications for which static analysis is not available. Contributions specific to this thesis include a new hardware design, development of an effective simulation environment, full integration into the IMPACT compiler, and a detailed quantitative evaluation of the benefit of the memory conflict buffer for ILP processors.

- The sync arc technique proposed in this thesis provides an effective framework for providing source-level dependence information for use by low-level optimization and scheduling.

The technique is described in detail, defining the type of information to be carried by the sync arc, how the information is maintained through aggressive code transformations, and how the dependence information is used by low-level transformations. A quantitative analysis of the effectiveness of sync arcs demonstrates their potential benefit.

- The source-level dependence analysis required to support sync arcs is studied. The challenges for dependence analysis posed by the C language are discussed. In particular, the need for interprocedural analysis of C programs to support effective memory disambiguation for low-level code, and the required granularity of this analysis, is quantitatively investigated.

- The tradeoffs involved in selecting a static or dynamic memory disambiguation approach are explored. This analysis is unique in that an example of each approach has been implemented within a single compiler environment, enabling a fair comparison of the relative merits. Both approaches are shown to provide good memory disambiguation and to have applicability in different problem domains.

## 1.2 Overview

This dissertation is composed of eight chapters. Chapter 2 presents an overview of the organization of the IMPACT compiler. All compiler techniques discussed in this thesis are implemented within the framework of the IMPACT compiler. The simulation methodology employed in the thesis is also described. Chapter 3 discusses two approaches to deal with

ambiguous memory dependences: dynamic memory disambiguation and static memory disambiguation. The two approaches are reviewed and the tradeoffs between them are discussed.

A general technique for dynamic memory disambiguation, the memory conflict buffer, is presented in Chapter 4. This technique, which combines both hardware and compiler support, allows memory operations to be reordered during low-level code scheduling despite the presence of ambiguous memory dependences. The hardware support is responsible for detecting when truly dependent memory operations have been reordered. In the event this occurs, the compiler provides code to correct program execution.

Chapter 5 introduces sync arcs, a technique for maintaining explicit dependence information within the intermediate code. Static memory disambiguation is used to extract this dependence information from source-level code and to generate the sync arcs. A detailed discussion of how the sync arcs are preserved through and used by code transformations is presented.

Chapter 6 discusses the C dependence analysis used to provide the static memory disambiguation required for sync arcs. The interprocedural alias and side-effect analysis that supports this analysis is also presented. The experimental results using this dependence analysis and sync arcs are then presented in Chapter 7. A quantitative analysis of the benefit of improved memory disambiguation is given. This is followed by a comparative analysis of the relative benefit of the dynamic and static disambiguation approaches presented in this dissertation. Finally, Chapter 8 presents conclusions and suggests directions for future research.

## CHAPTER 2

## COMPILATION AND SIMULATION ENVIRONMENT

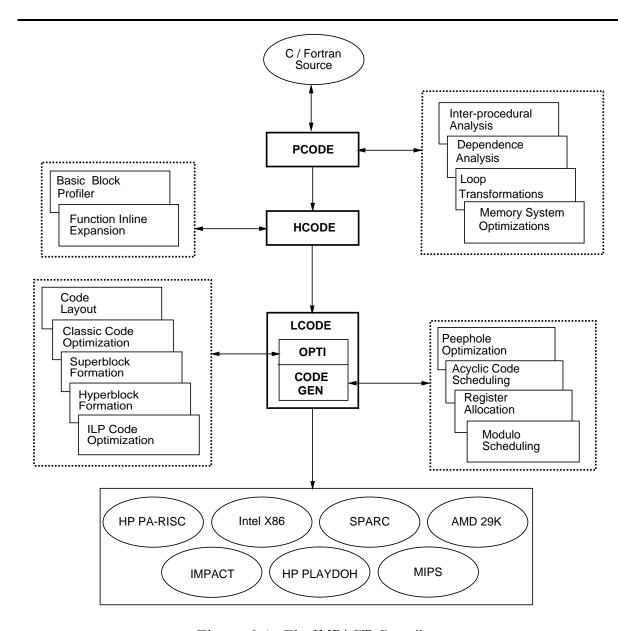

The compiler techniques necessary to investigate dynamic and static memory disambiguation approaches for this thesis are implemented within the framework of the IMPACT compiler project. The IMPACT compiler is a retargetable, optimizing C compiler being developed at the University of Illinois to investigate architectural and compilation techniques to support ILP processors. A block diagram of the IMPACT compiler is presented in Figure 2.1. The compiler accepts source code written in C, as well as Fortran code translated using the f2c translation tool [2]. The compiler can be divided into three distinct sections, each based upon a different intermediate representation (IR).

The highest level IR, Pcode, is a parallel C code representation with loop constructs intact. At the Pcode level, source-level techniques such as memory dependence analysis [3], loop-level transformations [4], and memory system optimizations [5], [6] are performed. Pcode is further described in Section 2.1. The middle-level IR is referred to as Hcode. In Hcode, the control structure of the code has been flattened into a basic block structure with simple if-then-else and go-to control flow constructs, but expressions are still maintained hierarchically. During this phase of compilation, basic-block-level profiling, as well as profile-guided code layout and function inline expansion [7], [8], [9], are performed.

The lowest level of IR in the IMPACT compiler is referred to as *Lcode*. Lcode is a generalized register transfer language similar in structure to most load/store processor assembly instruction sets. The majority of ILP code transformations within the IMPACT compiler are

Figure 2.1 The IMPACT Compiler.

performed at the Lcode level. Section 2.2 details these code transformations. A detailed machine description database, *Mdes*, for each target architecture is available for use by all Lcode compilation modules [10].

Seven architectures are currently supported by the IMPACT compiler. These include the AMD 29K [11], MIPS R3000 [12], SPARC [13], HP PA-RISC, <sup>1</sup> and Intel X86 [14], [15]. The other two supported architectures, IMPACT and HP Playdoh [16], are experimental ILP architectures, which provide a framework for compiler and architectural research. The IMPACT architecture models a generic superscalar processor which executes the Lcode instruction set. After machine specific annotation of the Lcode, the IMPACT code generator can produce code for extended versions of the HP PA-RISC (IMPACT-HPPA) and the SPARC (IMPACT-SPARC) architectures. For this thesis, all experiments are based upon the IMPACT-HPPA architecture.

The remainder of this chapter details portions of the IMPACT compiler project especially important to this thesis. Sections 2.1 and 2.2 discuss the Pcode and Lcode levels of compilation. The superblock technique, which is foundational to much of IMPACT's ILP compilation, is presented in Section 2.3. Finally, the simulation environment used in this thesis is presented in Section 2.4.

#### 2.1 Pcode

High-level analyses, transformations, and optimizations which benefit from the availability of explicit source-level information are performed at the Pcode level. Within the Pcode IR, program code is represented in an abstract syntax tree containing hierarchical statement and

<sup>&</sup>lt;sup>1</sup>The HP PA-RISC code generator was developed by Richard E. Hank.

expression nodes. This hierarchical intermediate representation facilitates the manipulation of program structures such as loops and blocks of statements.

The Pcode module contains several code restructuring transformations and optimizations. General purpose loop transformations currently implemented include loop distribution or loop fission, rectangular loop interchange, loop skewing, and loop reversal [4]. These loop transformations are usually exploited as tools to improve the applicability of other transformations and optimizations. In addition, conversion of while-type loops into for-type loops to facilitate data dependence analysis is also supported. Loop parallelization is currently limited to identification of loops which can be software pipelined. Loops that are identified as good candidates for software pipelining are marked at the Pcode level, but the software pipelining transformation is actually accomplished at the Lcode level during code generation [17], [18].

Memory system optimizations include loop blocking (also called iteration space tiling) to improve cache access locality [5], software prefetching, and data relocation and prefetching [6], a hardware-assisted form of software prefetching which simultaneously relocates array data to reduce cache mapping conflicts.

To support these transformations and optimizations, Pcode performs several types of analysis. Control-flow analysis provides the structural framework upon which many of the transformations and other analyses are built. It consists of control-flow graph construction, loop detection and nesting determination (used mostly for unstructured loops), support for data dependence analysis, and unreachable code removal. Data-flow analysis determines the flow of program values, variables, and expressions through the control-flow graph. Traditional types of data-flow information are computed including sets of reaching definitions and uses, available definitions and uses, and live variables [19]. In addition, an extended type of data-flow analysis

called *loop-carried data-flow analysis* is used to calculate loop-carried reaching definitions and uses, which are useful for determining accurate dependence direction vectors for scalar variables.

Data dependence analysis [3] calculates the dependence relationship between each access pair in the function. It consists of several steps. First, a variable access table containing information for each distinct variable reference in the function is built. Next, aliases are added between accesses in the access table as necessary. These aliases may stem from several sources, such as aliases between elements of a union, pointer aliasing caused by assignment expressions, or aliases determined during interprocedural analysis. Finally, the dependence relationship between pairs of accesses is determined. The Omega Test [20], developed by William Pugh at the University of Maryland, is employed to produce the data dependence equations and inequalities used to generate distance and direction vectors for pairs of variable references.

Pcode's existing data dependence analysis lays the foundation for the dependence analysis used to support the sync arc research presented in this thesis. Chapter 6 further discusses Pcode data dependence analysis and the enhancements made to it as part of this thesis.

#### 2.2 Lcode

The Lcode level performs low-level code optimization and scheduling to expose and exploit a program's inherent ILP. Lcode is logically subdivided into two subcomponents: machine-independent optimizations performed prior to code generation and machine-dependent optimizations performed during code generation. Although the internal data structures used during these two components of Lcode are identical, the machine-dependent portion of the Lcode is sometimes referred to as *Mcode*. The difference between Mcode and Lcode is that Mcode is broken down such that there is a one-to-one mapping between Mcode instructions and the

target machines' assembly languages. For example, when generating code for the X86 architecture, the Lcode will be in 3-operand format during machine-independent optimization, and then is converted to 2-operand format during the machine-dependent phases; once in 2-operand format, the code would be referred to as Mcode. Lcode instructions are broken up for a variety of reasons, such as limited addressing modes, limited opcode availability (e.g., no floating-point branch), ability to specify a literal operand, and field width of literal operands.

During the first step of Lcode compilation, all machine-independent classic optimizations are applied [21]. These include constant propagation, forward copy propagation, backward copy propagation, common subexpression elimination, redundant load elimination, redundant store elimination, strength reduction, constant folding, constant combining, operation folding, operation cancellation, code reordering, dead code removal, jump optimization, unreachable code elimination, loop invariant code removal, loop global variable migration, loop induction variable strength reduction, loop induction variable elimination, and loop induction variable reassociation. Additionally, analysis is performed to identify safe instructions for speculation [22].

The next step in Lcode compilation is to perform superblock code transformation and optimization. The superblock compilation structure is explained in detail in Section 2.3. When predicated execution support is available in the target architecture, hyperblocks [23] rather than superblocks are used as the underlying compilation structure. All superblock optimization techniques have also been extended to operate on hyperblocks. In addition, a set of hyperblock-specific optimizations to further exploit predicated execution support are available. For this thesis, the superblock was the primary compilation structure used for memory disambiguation experiments.

Following superblock transformations, machine-specific code generation is performed for one of the seven architectures shown in Figure 2.1. Code generation within the IMPACT compiler consists of three phases. During Phase I, Lcode to Mcode conversion is performed to transform the Lcode into a one-to-one correspondence to target machine assembly. During Phase II of code generation, machine-specific optimizations, code scheduling, and register allocation are performed. Finally, during Phase III of code generation, Mcode is translated into the target architecture's assembly language.

Two of the most significant components of code generation are the instruction scheduler and register allocator, both of which are common modules shared by all code generators. Scheduling is performed via either global acyclic scheduling [22], [24] or software pipelining [17], [18]. Global acyclic scheduling is applied both before register allocation (prepass scheduling) and after register allocation (postpass scheduling) to generate an efficient schedule. Loops targeted for software pipelining are identified and marked at the Pcode level. These loops are pipelined using modulo scheduling and the remaining code is scheduled using the global acyclic scheduler. Additionally, code transformations to support the memory conflict buffer technique described in Chapter 4 are applied during code scheduling.

Register allocation is performed using a graph-coloring-based scheme [25]. The register allocator employs profile information, if available, to better prioritize virtual registers for allocation to physical registers.

For each target architecture, a set of specially tailored peephole optimizations is performed.

These peephole optimizations are designed to remove inefficiencies introduced during Lcode to

Mcode conversion, to take advantage of specialized opcodes available in the architecture, and

to take advantage of new optimization opportunities after spill code has been added by the register allocator.

# 2.3 Superblocks

For most non-numeric programs, the ILP available within individual basic blocks is extremely limited [26], [27], [28]. An ILP compiler must be able to optimize and schedule instructions across basic block boundaries to find sufficient parallelism. An effective structure for ILP compilation is the *superblock* [23], [29]. The formation and optimization of superblocks increases the ILP available to the scheduler along important execution paths by systematically removing constraints due to the unimportant paths. Superblock scheduling is then applied to exploit ILP by mapping it to the available processor resources.

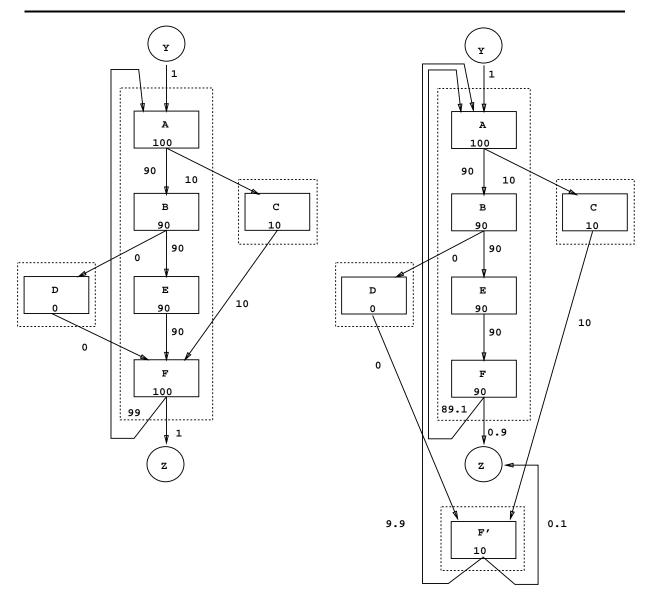

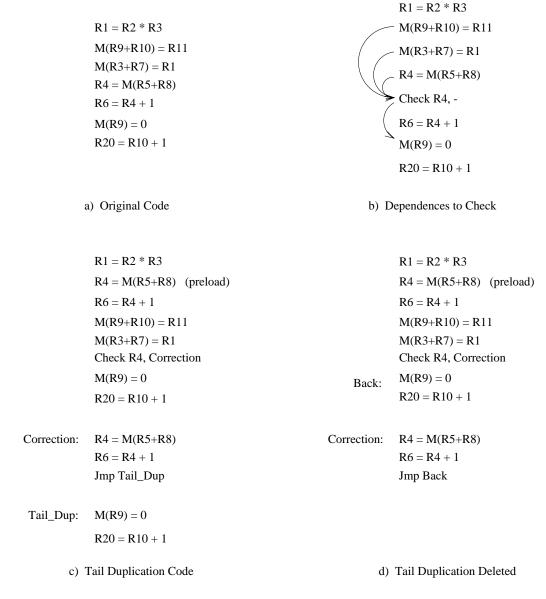

A superblock is a block of instructions for which the flow of control may only enter from the top, but may leave at one or more exit points. It is formed by identifying sets of basic blocks which tend to execute in sequence (called a *trace*) [30]. These blocks are coalesced to form the superblock. Tail duplication is then performed to eliminate any side entrances into the superblock [31].

The formation of superblocks is illustrated in Figure 2.2, taken from [23]. Figure 2.2(a) shows a weighted flow graph which represents a loop code segment. The nodes in the graph correspond to basic blocks and the arcs represent the possible control transfers. The number in each node represents the execution frequency of the basic block (as determined by profiling). Likewise, the number associated with each arc represents the number of times that particular control transfer path is followed. Because the most frequent control flow is along the path  $\{A, B, E, F\}$ , this trace is selected for superblock formation. To eliminate side entrances to this

(a) Original weighted control graph

(b) Control graph after tail duplication

Figure 2.2 An Example of Superblock Formation.

superblock, tail duplication replicates basic block F, and control flow from blocks C and D is redirected to this duplicated block. The result is the flow graph shown in Figure 2.2(b).

Following superblock formation, ILP is further exposed through superblock optimizations. Classic optimizations are reaccomplished within the scope of the superblock. Superblock enlarging optimizations such as loop unrolling and loop peeling are employed to increase the size of superblocks, providing more visible instructions to the scheduler. Dependence-removing optimizations such as register renaming, induction variable expansion, and accumulator expansion are performed to remove data dependences, increasing available ILP. For a detailed explanation of the superblock optimizations, see [23].

The superblock compilation framework can be viewed as an attempt to reduce the impact of control transfer instructions on ILP. For an architecture that supports control speculation, the greater optimization and scheduling freedom afforded by superblocks significantly reduces the negative impact of branches on ILP. The importance of this result to this thesis is that reducing the impact of branches on ILP has exposed ambiguous memory dependences as a secondary impediment to ILP. The potential ILP exposed by superblock formation cannot be fully exploited unless effective methods are developed to overcome the restrictions imposed by memory dependences.

## 2.4 IMPACT Simulation Environment

All experiments performed for this thesis were done using the IMPACT simulation environment. The IMPACT simulator models in detail the target architecture's prefetch and issue unit, instruction and data caches, branch prediction mechanism, and hardware interlocks. This allows the simulator to accurately model the number of cycles required to execute a program,

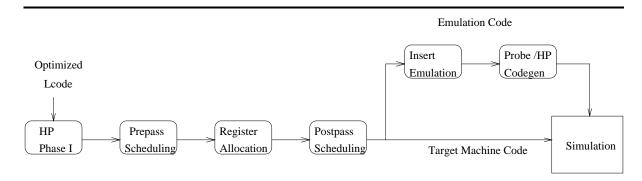

Figure 2.3 MCB Compilation Path for Simulation.

as well as provide detailed analysis such as cache hit rates or branch prediction performance.

The simulator also allows proposed new hardware, such as the memory conflict buffer, to be accurately modeled and analyzed. Supported architecture types include in-order superscalar and very long instruction word (VLIW) architectures.

The IMPACT simulation approach is referred to as emulation-driven simulation. Figure 2.3 shows the compilation path for the simulation used throughout this thesis. The figure assumes the Lcode has already been compiled through classic and ILP code optimizations, including superblock formation. Because the simulation performed for this thesis assumes an instruction set architecture which is an extension of the HP PA-RISC 1.1 instruction set, the optimized code is first run through the initial phase of the HP PA-RISC code generator, which transforms the code into HP Mcode. The code is then passed through pre-pass scheduling, register allocation, and post-pass scheduling for the target architecture, using the generic IMPACT code generator. During this stage, architectural features of the simulated architecture are assumed. For example, if the architecture being simulated can issue eight instructions per cycle, the scheduler reorders the code based upon this model. For the MCB experiments detailed in Chapter 4, the MCB code transformations are performed during pre-pass scheduling.

Following this stage of compilation, the intermediate code is in a form which could be executed by the simulated architecture. However, to create an executable file to drive the simulation, any unsupported architectural features of the simulated architecture must be emulated to allow the code to execute on the host architecture, an HP PA-RISC 7100-based workstation. For example, if the simulated architecture contains hardware support for MCB, emulation code must be added to allow the code to execute properly on the host architecture. Following insertion of required emulation code, a second phase of register allocation, assuming host architecture register file constraints, is performed. The code is then instrumented to gather address and branch direction data for the simulation, and then the final phases of the code generation are performed to create an executable file. This executable file serves two purposes. First, because the executable can be run to provide correct program results, it verifies that code transformations have been performed correctly. Second, it generates the trace information required to drive the simulation.

Simulation is performed on the modeled architecture's code, using address and branch direction data from the emulation path. The result is a highly accurate measure of the number of cycles required to execute the program on the simulated architecture. Due to the complexity of simulation, sampling [32] is used to reduce simulation time for large benchmarks. For sampled benchmarks, a minimum of 10 million instructions are simulated, with at least 50 uniformly distributed samples of 200,000 instructions each. Testing has shown sampling error to be less than 1% for all benchmarks.

Further details of the architecture being modeled for various experiments is provided within the experimental sections of this thesis.

#### CHAPTER 3

#### OVERVIEW OF MEMORY DISAMBIGUATION

Control flow instructions (e.g., branches and function calls) have been widely recognized as the major impediment to exposing ILP. Because such a high percentage of instructions (20-30%) in typical C programs are control flow instructions, the compiler must be able to search beyond the individual basic block for parallelism. Techniques such as trace scheduling [30], superblocks [29], and hyperblocks [23] have been developed to expand the size of blocks in which the compiler performs optimization and scheduling. Speculative execution techniques have been developed to allow code motion between basic blocks [33], [34], [35]. As a result of these techniques, the impact of control flow instructions on ILP can be significantly reduced.

However, this reduction of the impact of control flow instructions on ILP has exposed a secondary impediment to ILP: ambiguous memory dependences [1]. In much the same way that branches can restrict code optimization and scheduling, ambiguous memory dependences also prohibit these important transformations. In particular, dependences between loads and stores result in the greatest restriction to ILP.

Dependences between two loads (referred to as an *input dependence*) usually have little or no impact on ILP. Dependences between two store operations (referred to as an *output dependence*) rarely restrict optimization, and there tends to be limited benefit from reordering stores during code scheduling. However, dependences between load and store operations are a much more serious problem for the compiler. During code scheduling, *flow dependences* (the situation when a load operation sequentially follows a dependent store operation) often severely restrict

code reordering. Anti dependences (when a load sequentially precedes a dependent store) tend to be a minor problem during scheduling because load operations tend to move upward and stores tend to move downward during code scheduling. During optimization, both flow and anti dependences severely restrict transformations.

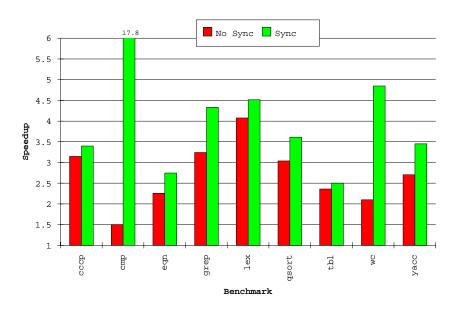

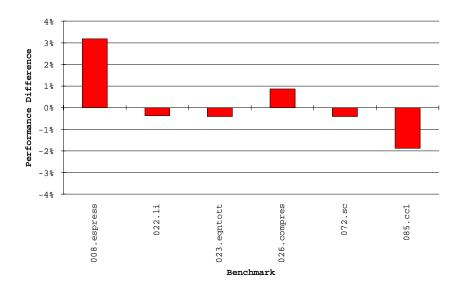

To overcome the problem of ambiguous memory dependences, optimizing compilers perform memory disambiguation. To illustrate the potential benefit of memory disambiguation, an experiment was conducted using a suite of twelve benchmarks, including five unix benchmarks, five SPEC-CINT92 benchmarks, and two SPEC-CFP92 benchmarks. The benchmarks were scheduled using the three different models of disambiguation. In the first model, no memory disambiguation was performed, i.e., all memory operations were assumed to be dependent on all other memory operations. The second model used the existing (prior to this thesis) IMPACT low-level memory disambiguation. This disambiguation model is typical of the static analysis performed on low-level code by current commercial compilers. The analysis is strictly intraprocedural and uses only information available within the low-level code for its analysis, i.e., no source-level information is used to aid the analysis. It is designed to be fast and fully safe, but is limited in its effectiveness. The final model used in this experiment is ideal disambiguation, where all memory operations are considered to be independent unless the static analysis proves them to be dependent. Note that this disambiguation model makes unsafe assumptions and may result in incorrect code if truly dependent operations are reordered. However, this model provides an upper bound on the performance which could potentially be achieved from scheduling with improved memory disambiguation.

For this experiment, an 8-issue architecture with 64 integer and 64 floating-point registers is assumed. No restrictions are placed on the combination of instructions that may be issued

in a cycle. Instructions latencies of the HP PA-7100 are also assumed. Because the executable generated from the ideal disambiguation model could execute incorrectly, the experiment was performed using cycle count estimates provided by the scheduler rather than the full simulation approach described in Section 2.4. To estimate the number of cycles required for execution, the code was profiled prior to scheduling to determine the execution frequency of each control block. The code was then scheduled, using the various levels of disambiguation, to determine the number of cycles each block would take to execute. From this, an accurate estimate of required execution cycles can be determined, excluding cache effects and branch-misprediction penalties.

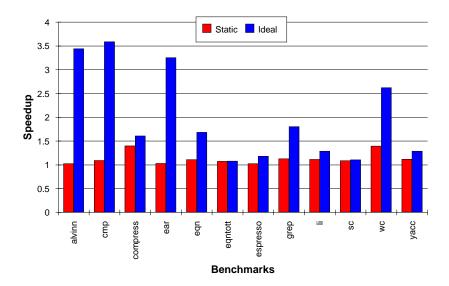

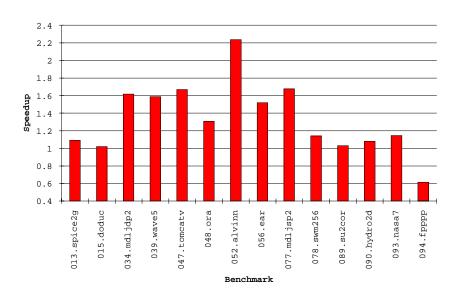

Figure 3.1 presents the results of this experiment. The vertical bars on the graph reflect the relative speedup of the current static and ideal disambiguation models over the baseline nodisambiguation case. Thus, a speedup of 1.0 indicates equivalent performance to the baseline case. Several items should be noted from this figure. First, the ideal disambiguation results indicate that by eliminating memory dependences a significant amount of potential ILP can be exposed. For six of the twelve benchmarks tested, more than 50% speedup could be achieved if all ambiguous memory dependences could be eliminated. A second point to note is that IMPACT's current low-level memory disambiguation is in large part ineffective at removing ambiguous memory dependences and exposing parallelism. It appears that a significantly more powerful disambiguation technique is required to eliminate ambiguous dependences and provide performance closer to the ideal disambiguation case. Finally, the experiment demonstrates that although improved memory disambiguation can significantly increase performance, it is not a panacea which can increase performance on all benchmarks. For example, in the benchmark 023.equivott, over 80% of the execution time is spent in an inner loop which contains no store

Figure 3.1 Effect of Memory Disambiguation on Performance.

operations; thus, improved memory disambiguation has little effect on performance. Note that this experiment only measures the potential benefit of improved memory disambiguation during scheduling; one would also expect a significant benefit for optimization. This benefit is quantified in Chapter 6.

The remainder of this chapter examines two general memory disambiguation approaches: dynamic and static. Tradeoffs between these two approaches are examined, followed by a review of related work for each of the two approaches.

# 3.1 Tradeoffs Between Dynamic and Static Approaches

Various solutions have been proposed to provide improved memory disambiguation. In general, these solutions can be categorized as either dynamic or static. Static memory disambiguation, also referred to as dependence analysis, attempts to determine the relationship between pairs of memory references at compile time. Once the compiler has determined the

Table 3.1 Tradeoffs of Dynamic and Static Memory Disambiguation.

| Dynamic | Less compile-time investment          |

|---------|---------------------------------------|

|         | More accurate                         |

|         | Compiler support confined to backend  |

|         | Useful when source not available      |

| Static  | Requires no hardware support          |

|         | Requires no instruction overhead      |

|         | May be nearly as accurate in practice |

dependence relationship for memory references, this information can be used to safely direct subsequent code transformations. In contrast, dynamic memory disambiguation attempts to determine at run-time whether two references could possibly reference the same memory location. The compiler may speculatively perform a code transformation based upon an assumed dependence relationship between memory references, and then provide some means of dynamically determining at run-time if the assumed relationship was correct. In the event of an incorrect assumption, the dynamic approach must provide a mechanism to ensure correct execution.

Both dynamic and static memory disambiguation approaches are targeted toward increasing processor performance. Tradeoffs exist between the approaches; a particular implementation may employ static techniques, dynamic techniques, or some combination of both. Table 3.1 highlights some of the relative advantages of the two approaches.

Dynamic approaches usually require significantly less compile-time investment than static approaches. In general, the compiler algorithms to support most currently proposed dynamic approaches do not significantly impact the overall compilation time. In contrast, static memory disambiguation requires an in-depth analysis which can dominate the time required for compilation. Languages such as C, which require interprocedural analysis to provide high accuracy, require an even greater investment in compilation time. For applications requiring extremely

$$for (i = 0; i < M; i++) \qquad \qquad for (i = 0; i < M; i++) \\ for (j = 0; j < N; j++) \qquad \qquad A[i] = A[M-i]; \\ A[j] = A[B[i]]; \qquad \qquad (b) occasional dependence$$

$$for (i = 0; i < M; i++) \qquad \qquad while (ptr != 0) \\ A[i] = A[i*i + 3]; \qquad \qquad ptr = ptr->next; \\ (c) non-linear references \qquad (d) pointer references \\ \textbf{Figure 3.2} \quad Limitations of Static Memory Disambiguation.}$$

fast compilation, a dynamic memory disambiguation technique may prove to be a better approach.

Because dynamic approaches do not attempt to determine the dependence relationship between two operations until run-time, they are inherently more accurate than static approaches. During program execution, the dynamic approach knows the exact memory address being accessed by each reference and, thus, can determine dependence relationships with complete accuracy. Although static memory disambiguation approaches can be highly accurate for many applications, current techniques are unable to accurately determine dependence relationships in certain circumstances. Figure 3.2 highlights code segments for which static memory disambiguation is less effective. In Figure 3.2(a), the reference to A[B[i]] is an indirect reference through a second array. Because the static analysis cannot determine the value stored in the location B[i], it is unable to accurately determine the dependence relationship of this reference of the array A to other references to the same array.

Figure 3.2(b) illustrates the problem that occasional dependences cause for static memory disambiguation. In this example, a loop-carried dependence exists between the two references to the array A. However, the dependence distance (the number of loop iterations from the iteration in which one reference accesses a certain memory location until the other reference accesses the same address) is not constant between loop iterations. Thus, the static dependence analysis cannot accurately determine the dependence relationship. If the value for M cannot be determined by the compiler, the static analysis also cannot determine when and if a zero distance (non-loop carried) dependence exist between the two references. In Figure 3.2(c), the problem of non-linear references is shown. Because most static memory disambiguation approaches cannot handle non-linear array indices, the reference to A[i\*i+3] cannot be disambiguated from other references to the same array. Finally, Figure 3.2(d) shows an example of the problem with performing static analysis for languages which support pointers. In this example, a simple loop that walks a linked list data structure is shown. Unless the dependence analysis is able to somehow determine that the list in acyclic, the dependence relationship between the references to ptr and  $ptr \rightarrow next$  cannot be accurately determined.

Supporters of static memory disambiguation would likely contend that the array examples shown in Figure 3.2 do not occur frequently enough in most applications to result in significant loss of accuracy for static analysis. Little or no data exist to quantify how often these situations occur on real applications. Static analysis of pointers has improved greatly in recent years, reducing this accuracy advantage of dynamic approaches. Thus, although dynamic approaches are inherently more accurate, static approaches may prove to be nearly as accurate for most applications.

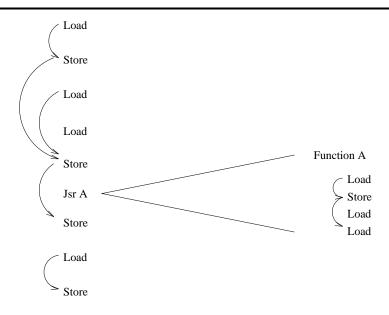

Another advantage of dynamic memory disambiguation approaches is that their compiler support is usually confined to the back end of the compiler. Code transformations to support dynamic approaches are normally performed on the low-level form of the code being compiled. Thus, a single implementation of a dynamic approach can provide memory disambiguation for an application that supports numerous front-end source languages. The transformations are independent of the source language. Static approaches, on the other hand, are normally performed on high-level source code. If an application that must support multiple source languages employs static memory disambiguation, a unique implementation will likely be required for each of the supported languages.

The primary advantage of static memory disambiguation is that it requires no support beyond the analysis performed by the compiler. In contrast, dynamic approaches can require several types of overhead. First, dynamic approaches usually require the insertion of extra instructions into the code stream to provide the run-time checking. Even for wide-issue architectures, these additional instructions may result in a performance penalty. Thus, for a static approach and a dynamic approach that provide comparable accuracy, the static approach will likely have better performance due to the instruction overhead of the dynamic approach. Second, dynamic approaches often require instruction-set architecture (ISA) support, in the form of new instructions. This requirement limits the application of some dynamic approaches for existing architecture families. Also, the addition of new instructions to the ISA which require additional bits may be very difficult and require extensive redesign. Finally, some dynamic approaches require significant hardware support. The hardware cost of the approach must be considered along with the potential performance improvements from the improved memory disambiguation, i.e., does the performance improvement provided by the dynamic technique

outweigh the potential improvement if the same amount of chip area was applied to some alternate hardware feature (e.g., a larger cache)?

It should not be construed that the tradeoffs discussed above, or the performance comparisons provided later in this thesis, are intended to imply that either static or dynamic memory disambiguation is a better approach for all applications. The strengths and weaknesses of the approaches may make either, or possibly a combination of both, the best solution for a particular application. In fact, certain applications force the use of one approach or the other. For example, a static memory disambiguation approach that relies on use of source-level information is not possible for an application such as binary translation, in which no source-level information is available. For applications that must be compatible across an architecture family, such as the X86 family, a dynamic approach requiring changes to the ISA would not be useful.

# 3.2 Dynamic Memory Disambiguation Approaches

Dynamic memory disambiguation attempts to determine at run-time whether two references could possibly reference the same memory location. Most dynamic approaches deal specifically with memory flow dependences, attempting to remove these dependences and allow loads to execute before ambiguous stores. When a load operation, and possibly the load's dependent operations (flow dependences associated with the destination register of the load), bypass an ambiguous store operation, the operations that pass the store are being executed speculatively before it is determined that the value the load accesses is valid. This is termed data speculation. In contrast to control speculation, in which operations are executed before it is determined that they should have been executed according to original program control flow, data speculation executes instructions before it is determined that the data being used are valid.

```

R1 = R2 * R3

M(R9+R10) = R11

R4 = M(R5+R8)

R6 = R4 + 1

R1 = R2 * R3

R4 = M(R5+R8)

R4 = M(R5+R8)

R4 = R1

```

a) Original Code

b) Runtime Code

Figure 3.3 Run-time Memory Disambiguation Example.

In this section, several models of data speculation are discussed, requiring varying degrees of architectural support. These models also vary in what instructions can be speculated, i.e., whether only load instructions, or both the load and its dependent operations, are allowed to bypass stores. First, a compiler-only model known as run-time disambiguation is presented. As presented, this model allows only load instructions to be speculated, but it could easily be extended to also allow dependent operations to be speculated. Next, five models that use a combination of architectural and compiler support are examined. Two of these allow only loads to be speculated, and the remainder allow dependent operations to be speculated also. Finally, the hardware-only model of dynamic memory disambiguation is reviewed.

## 3.2.1 Run-time disambiguation

Nicolau has proposed a software-only data speculation technique known as run-time disambiguation [36]. Run-time disambiguation inserts explicit address comparisons and conditional branch instructions into the code which allow memory flow dependences to safely be removed, enabling load instructions to percolate upward past ambiguous stores during code scheduling. Figure 3.3 illustrates the application of run-time disambiguation. The original code segment in

Figure 3.3(a) has two store operations followed by an ambiguous load. Figure 3.3(b) reflects the application of run-time disambiguation to the code: the load has been moved above both stores, and explicit address comparison code has been added. When the address comparison code determines that the addresses of the load and the store were identical, the value being stored is simply moved into the destination register of the load. In the example shown, if the address of the load operation (R5 + R8) is the same as the store address (R9 + R10), then the subsequent move operation places the value from R11 in the load's destination (R4). Similar code is also added following the second store operation.

The major advantage of run-time disambiguation is that it requires no ISA or hardware support, and thus could be applied to existing architectures or families of architectures. However, it has several major limitations, particularly when applied to ILP processing. First, the technique can result in an extremely large amount of code growth when used with ILP compilation techniques. The number of address comparison and conditional branch instructions inserted can be prohibitive as a result of aggressive code reordering: if m loads bypass n stores,  $m \times n$  comparisons and branches are required. Second, the technique adds branch instructions to the code. Although superscalar and VLIW processors can issue and execute many operations each cycle, they are typically very limited in the number of branch operations they can execute (usually only one branch per cycle). These added branches are usually highly predictable, but they may impact performance in branch intensive code. A third limitation of run-time disambiguation is that it does not readily address the access width problem. Simple address comparison is insufficient to detect ambiguity in the presence of memory instructions of different size (e.g., an integer store followed by a character load). To ensure correct execution, a number of the least-significant-bits of the addresses must be ignored during address comparison, requiring

further instruction overhead. Finally, the technique as proposed allows only load operations, and not their dependent operations, to bypass stores. This significantly limits the scheduling freedom necessary for exploiting ILP. Run-time disambiguation could be extended to allow the load's dependent operations to bypass the store, using the compilation techniques described in Chapter 4.

## 3.2.2 Preload register update

A major limitation of run-time disambiguation discussed above is the requirement that explicit address comparisons be added to the code. The preload register update technique proposed by Chen et al. [37] attempts to relieve this problem by using hardware to perform the address comparisons and move operations. A preload instruction informs the hardware that a load is being speculated above ambiguous stores, and therefore requires its address be saved and checked against subsequent store addresses. If a match occurs between a store and load address, the hardware "updates" the destination register of the load with the store value. Address comparisons for the preload continue until a commit instruction is executed. A commit instruction is needed so that the coherence mechanism (the checking of store and load addresses and execution of potential updates) can be turned off for this particular load. This ensures that only stores that were originally located before a speculated load are allowed to update the load's destination register. The compiler must ensure that a commit instruction is not moved above or below a store instruction during code transformations.

Figure 3.4 demonstrates the preload register technique using the previous code example. Note in Figure 3.4(b) that the load has again bypassed the stores, and has been marked as a preload. Following the last store, a commit instruction has been added. Note also that, like  $\begin{array}{lll} R1 = R2*R3 & R1 = R2*R3 \\ M(R9+R10) = R11 & R4 = M(R5+R8) \ (preload) \\ M(R3+R7) = R1 & M(R9+R10) = R11 \\ R4 = M(R5+R8) & M(R3+R7) = R1 \\ R6 = R4+1 & commit \ (R4) \\ R6 = R4+1 & R6 = R4+1 \end{array}$

a) Original Code

b) Preload Register Update Code

Figure 3.4 Preload Register Update Example.

run-time disambiguation, the dependent operation (R6 = R4 + 1) is not allowed to bypass the stores.

Preload register update successfully eliminates the code growth problem of run-time disambiguation, and it does not require the addition of branches. Hardware mechanisms could also be provided to overcome the access width problem. The major limitations of the technique are that it requires both ISA and hardware support and that it does not allow the load's dependent operations to bypass stores.

#### 3.2.3 HP smart load

Hewlett Packard has developed a scheme, similar to preload register update, which also allows load instructions to be moved above ambiguous stores [38]. Every speculated load defines a watch window which indicates how many instructions above its original position the load has been speculated. The register file is modified to store the address of the preload in addition to the data, and includes counters used to determine when the preload's watch window is no longer active. Additionally, a 2-bit flag records whether the register contains an active (being watched) load value and whether a subsequent store has matched the speculated load's address.

If an incoming instruction is a load and it has been speculated, its destination register has to be initialized. This initialization includes setting the counter to the number of instructions above its original position that a load has been speculated and setting the flag to indicate the register contains an active load. When a store instruction is issued, its address must be checked against all the active load addresses found in the register file. If a match is found, the corresponding bit in the register file is set to record the match. When the original position of a speculated load instruction is reached, a new load is generated if the flag state indicates that a store address match has occurred.

The compiler support required for this technique is also very similar to preload register update. Rather than marking the load as a preload as shown in Figure 3.4(b), the smart load technique would mark it as being speculated two instructions. Thus, after the two store operations it bypassed have been executed, the counter associated with R4 would have the value zero and the load would be committed. No explicit commit instruction is required.

One variation on this scheme utilizes forwarding. If a store address conflicts with a speculative load address, the data contained in the store are used instead of the data obtained by the load. This method is very similar to preload register updating, and makes generation of the extra load instruction unnecessary.

#### 3.2.4 Speculative disambiguation

Huang et al. have proposed speculative disambiguation [39], a combined hardware and compiler technique to allow aggressive code reordering using predicated instructions. It is similar to run-time disambiguation, but employs compiler techniques that allow both a load and its dependent instructions to bypass an ambiguous store. The method also allows two

| R1 = R2 * R3<br>M(R9+R10) = R11               | R4 = M(R5+R8)<br>R6 = R4 + 1                     | p = (R5+R8==R9+R10) | q = (R5+R8==R3+R7) |

|-----------------------------------------------|--------------------------------------------------|---------------------|--------------------|

| M(R3+R7) = R1<br>R4 = M(R5+R8)<br>R6 = R4 + 1 | R1 = R2 * R3<br>M(R9+R10) = R11<br>M(R3+R7) = R1 | R6 = R11 + 1 (pq')  | R6 = R1 + 1 (q)    |

a) Original Code

b) Speculative Disambiguation Code

Figure 3.5 Speculative Disambiguation Example.

ambiguous stores to be reordered. This is accomplished by generating code for both the case when the two instructions are independent and for when they are dependent. The two versions of the code are conditioned by opposite predicates, so that only one version of the code is actually executed.

Figure 3.5 illustrates this technique using the running code example. In Figure 3.5(b), the predicated code is shown in several columns, corresponding to different predicate cases. The first column shows the case in which the load is independent of the stores, and it can be freely scheduled past the stores. The second column handles the case in which the first store conflicts with the load, but not the second. This is indicated by predicate p being true and predicate q being false. In this case, the add instruction which originally used R4 now uses the store value, R11, as its input. Note that the load is not re-executed in the case of a conflict, but all uses of the load's destination register are re-executed using the alternate value. The third column shows the case when the load conflicts with the second store, indicated by predicate q being true. Here, the add instruction is re-executed using the value stored in R1.

Note the code growth from a single load with only one dependent operation bypassing two stores. In the presence of aggressive code reordering, code growth would be prohibitive. Additionally, the issue bandwidth of the ILP processor would quickly be saturated. Thus, the technique cannot be generally applied to support ILP compilation, and is more suitable for narrow-issue processors requiring only minimal code reordering. The primary advantages of the technique are that it requires no additional hardware overhead (for processors already supporting predication) and that it does allow the load's dependent operations to bypass stores to a limited extent.

#### 3.2.5 Unsafe loads

Silberman and Ebcioglu presented a dynamic memory disambiguation scheme as part of their framework for supporting heterogeneous instruction set architectures [40]. This framework was developed to allow applications written for one instruction set to be migrated to a higher performance architecture without a significant investment by the user or developer.

They use both a base machine engine which executes the original instruction set architecture and a native machine engine with a higher performance architecture (e.g., a RISC engine) to implement their scheme. Two versions of the code are generated, one for each engine. For best performance, the goal is to execute the native version of the code as much as possible, periodically updating the base machine state at predetermined checkpoints. The approach employs the concept of both architected registers (registers present in original instruction set) and nonarchitected registers (extra registers present in the native engine).

In the native version of the code, they allow loads whose destination is a nonarchitected register to be speculated above ambiguous stores. The nonarchitected registers have additional fields which store the memory address of the load, its length, and an extension tag which indicates whether an address conflict has occurred.

At each checkpoint, the nonarchitected registers are copied into the architected registers to update state. If the extension flag of the nonarchitected register is set, an address conflict has occurred since the previous checkpoint and the native machine state may not be valid. In this case, the processor re-executes the section of code containing the speculated load in the base machine engine and re-enters the native engine at the next opportunity.

Although applied within the context of the heterogeneous instruction set architectures, this approach to dynamic disambiguation has general application. The hardware requirements are very similar to the hardware requirements for the memory conflict buffer approach presented in Chapter 4. Although requiring extensive hardware support, the technique allows both loads and their dependent instructions to bypass stores.

# 3.2.6 Hardware-only disambiguation

Hardware-only dynamic memory disambiguation techniques have been widely used for architectures which employ dynamic instruction scheduling. Early dynamic architectures such as the IBM 360/91 [41] and the CDC 6600 [42] employed simple store queues which allowed subsequent loads to execute out-of-order. The HPS architecture [43] proposed node tables which buffered memory operations awaiting operands, allowing subsequent memory operations to execute. A store queue was also employed to allow loads to bypass stores. Franklin and Sohi proposed the address resolution buffer [44], which also allows dynamic reordering of memory operations. It provides special support allowing subsequent memory operations to execute even if the address of an earlier store operation has not been resolved. For wide-issue ILP architectures, each of these dynamic scheduling techniques is limited by the size of the visible instruction win-

dow, restricting the aggressive code reordering necessary to obtain high utilization of multiple functional units.

# 3.3 Static Memory Disambiguation Approaches

Static memory disambiguation, or dependence analysis, attempts to determine the relationship between two references at compile-time. Most frequently, dependence analysis has been applied at the source code level, and is used to facilitate source-to-source code transformations. In-depth static analysis has seldom been applied to assist compilation of low-level code; in most commercial compilers, memory disambiguation for low-level code is performed using only information available within the low-level code (i.e., no source-level information). A few of the newest optimizing compilers attempt to pass some limited source information to the intermediate code, but this information is usually limited to array references. Because so little work has previously been done on performing dependence analysis to facilitate low-level code optimization and scheduling, the discussion in this section focuses on techniques which are being developed primarily to support source-level transformations. This related work is presented in the context of the several complications to dependence analysis which must be addressed to provide accuracy.