# AN EFFICIENT FRAMEWORK FOR PERFORMING EXECUTION-CONSTRAINT-SENSITIVE TRANSFORMATIONS THAT INCREASE INSTRUCTION-LEVEL PARALLELISM

### BY

### JOHN CHRISTOPHER GYLLENHAAL

B.S., University of Arizona, 1991 M.S., University of Illinois, 1994

### **THESIS**

Submitted in partial fulfillment of the requirements for the degree of Doctor of Philosophy in Electrical Engineering in the Graduate College of the University of Illinois at Urbana-Champaign, 1997

Urbana, Illinois

### AN EFFICIENT FRAMEWORK FOR PERFORMING EXECUTION-CONSTRAINT-SENSITIVE TRANSFORMATIONS THAT INCREASE INSTRUCTION-LEVEL PARALLELISM

John Christopher Gyllenhaal, Ph.D.

Department of Electrical and Computer Engineering

University of Illinois at Urbana-Champaign, 1997

Wen-mei W. Hwu, Advisor

The increasing amount of instruction-level parallelism required to fully utilize high issue-rate processors forces the compiler to perform increasingly transformations, many of which require adding extra operations in order to remove those dependences constraining performance. Although aggressive application of these transformations is necessary in order to realize the full performance potential, overlyaggressive application can negate their benefit or even degrade performance. This thesis investigates a general framework for applying these transformations at schedule time, which is typically the only time the processor's execution constraints are visible to the compiler. Feedback from the instruction scheduler is then used to aggressively and intelligently apply these transformations. This results in consistently better performance than traditional application methods because the application of transformations can now be more fully adapted to the processor's execution constraints. Techniques for optimizing the processor's machine description for efficient use by the scheduler, and for incrementally updating the dependence graph after performing each transformation, allow the utilization of scheduler feedback with relatively small compile-time overhead.

# **DEDICATION**

To: Liesl, Mom, and Dad.

### **ACKNOWLEDGMENTS**

Without the support of many great people, this dissertation would not have been written. I wish to thank my advisor, Professor Wen-mei Hwu, who provided valuable guidance in many technical and nontechnical areas during my graduate studies; the members of the IMPACT group, both past and present, who developed the fantastic infrastructure that was used for this research; Dr. Rick Hank, Dr. Roger Bringmann, Dr. Scott Mahlke, Dr. Dave Gallagher, Dr. Dan Lavery, Sabrina Hwu, Grant Haab, Brian Deitrich, David August, and Teresa Johnson, who over the years, graciously acted as a sounding board even when they were extremely busy with their own research; Dr. Bob Rau, Dr. Mike Schlansker, Dr. Vinod Kathail, and the rest of the CAR group at HP Labs, who provided valuable insight and discussion concerning countless machine description issues; my parents, Malcolm and Joy Gyllenhaal, who always believed in me; my wife's parents, Donald and Dorothy Little, who made me a part of their family; and my wife, Liesl, who, in addition to being the best thing that has ever happened to me, edited this entire dissertation. I deeply appreciate the help I received from each of you.

# TABLE OF CONTENTS

|                                                                                                | Page |

|------------------------------------------------------------------------------------------------|------|

| 1. INTRODUCTION                                                                                | 1    |

| 1.1 Overview                                                                                   |      |

| 1.1 Overview                                                                                   | 1    |

| 2. THE ILP TRANSFORMATIONS EVALUATED                                                           | 8    |

| 2.1 Introduction                                                                               | 8    |

| 2.2 Renaming With Copy                                                                         | 8    |

| 2.3 Integer Expression Reformulation                                                           |      |

|                                                                                                |      |

| 3. PROPOSED APPROACH FOR SCHEDULE-TIME TRANSFORMATIONS                                         |      |

| 3.1 Introduction                                                                               |      |

| 3.2 The Schedule-Based Application Algorithm                                                   |      |

| 3.3 The Calculation of Transformation Priorities                                               |      |

| 3.4 Application of the Two ILP Transformations Evaluated                                       |      |

| 3.5 Related Work                                                                               | 47   |

| 4. PERFORMANCE BENEFITS OF SCHEDULE-TIME TRANSFORMATIONS                                       | 40   |

| 4.1 Introduction                                                                               |      |

| 4.1 Introduction  4.2 Criteria for Control-Block Level Comparisons                             |      |

| 4.3 The Processor Configurations                                                               |      |

| 4.4 The Four Application Approaches Evaluated                                                  |      |

| 4.5 How the Results Were Generated                                                             |      |

| 4.6 Overview of the Rest of This Chapter                                                       |      |

| 4.7 Control-Block Level Analysis of Renaming With Copy                                         |      |

|                                                                                                |      |

| 4.7.1 The four-issue processor configuration                                                   |      |

| 4.7.2 The two-issue processor configuration 4.7.3 The one-issue processor configuration 4.7.3. |      |

|                                                                                                |      |

| 4.7.4 The eight-issue processor configuration                                                  |      |

| 4.8.1 The four-issue processor configuration                                                   |      |

| 4.9 Control-Block Level Analysis of Both Transformations                                       |      |

| 4.9.1 The four-issue processor configuration                                                   |      |

| 4.10 Overall Results                                                                           |      |

| 4.10.1 Overall results for the four-issue processor configuration                              |      |

| 4.10.2 Overall results for the eight-issue processor configuration                             |      |

| 4.10.3 Overall results for the two-issue processor configuration                               |      |

| 4.10.4 Overall results for the one-issue processor configuration                               |      |

| 4.10.4 Overall results for the one-issue processor configuration                               | 114  |

| 5. INCREMENTAL DEPENDENCE GRAPH GENERATION                                                     | 117  |

| 5.1 Introduction                                                                               |      |

| 5.2 The Register Action Table                                                                  |      |

| 5.2.1 Designed to efficiently answer four time-critical queries                                |      |

| 5.2.2 Handling of overlapping registers                                | 120 |

|------------------------------------------------------------------------|-----|

| 5.2.3 Control, memory, and synchronization pseudoregister operands     | 122 |

| 5.2.4 Precalculation of the results for the four time-critical queries |     |

| 5.2.5 Incremental update of the register action table                  |     |

| 5.3 Building and Updating the Dependence Graph                         |     |

| 5.3.1 Drawing outgoing destination register dependences                |     |

| 5.3.2 Drawing incoming destination register dependences                |     |

| 5.3.3 Drawing outgoing source register dependences                     |     |

| 5.3.4 Drawing incoming source register dependences                     |     |

| 5.3.5 Drawing control, memory, and synchronization dependences         |     |

| 5.3.6 Drawing dependences for overlapping registers                    |     |

| 5.3.7 Drawing dependences for predicated code                          |     |

| 5.3.8 Building the dependence graph for the entire control block       | 149 |

| 5.3.9 Incrementally updating the dependence graph                      |     |

| 5.4 Related Work                                                       | 154 |

|                                                                        |     |

| 6. OPTIMIZATION OF MACHINE DESCRIPTIONS FOR EFFICIENT USE              |     |

| 6.1 Introduction                                                       |     |

| 6.2 Modeling Resource Constraints                                      |     |

| 6.3 A New Representation: AND/OR-Trees                                 |     |

| 6.4 Original MDES Characteristics                                      |     |

| 6.5 Eliminating Redundant or Unused MDES Information                   |     |

| 6.6 Utilizing Bit-Vector Representations                               |     |

| 6.7 Optimizing for Bit-Vector Representations                          |     |

| 6.8 Optimizing AND/OR-Trees for Resource Conflict Detection            |     |

| 6.9 Aggregate Effect of All Transformations                            |     |

| 6.10 Related Work                                                      | 187 |

|                                                                        |     |

| 7. COMPILE-TIME IMPLICATIONS OF SCHEDULE-TIME                          | 100 |

| TRANSFORMATIONS                                                        |     |

| 7.1 Introduction                                                       |     |

| 7.2 Compile-Time Requirements of the HP C Compiler                     |     |

| 7.3 Time Requirements of DHASY List Scheduling                         |     |

| 7.4 Time Breakdown for Performing Schedule-Time Transformations        |     |

| 7.5 Projection of Future Time Requirements                             | 199 |

| 8. CONCLUSIONS AND FUTURE WORK                                         | 202 |

| APPENDIX A. PERFORMANCE RESULTS FOR ALL PROCESSOR                      |     |

| CONFIGURATIONS                                                         | 205 |

| REFERENCES                                                             |     |

| VITΔ                                                                   | 263 |

# LIST OF TABLES

| Table                |                                                                                                                                                                                                                                 | Page |

|----------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|

| 4.1:<br>4.2:         | The four processor configurations evaluated  Operation latencies                                                                                                                                                                |      |

|                      |                                                                                                                                                                                                                                 |      |

| 6.1:                 | Option breakdown and scheduling characteristics for the four-issue processor configuration.                                                                                                                                     | 163  |

| 6.2:                 | Option breakdown and scheduling characteristics for the one-issue processor configuration.                                                                                                                                      | 169  |

| 6.3:                 | Option breakdown and scheduling characteristics for the two-issue processor configuration.                                                                                                                                      | 169  |

| 6.4:                 | Option breakdown and scheduling characteristics for the eight-issue processor configuration.                                                                                                                                    |      |

| 6.5:                 | Original scheduling characteristics of the machine descriptions for the four processor configurations.                                                                                                                          |      |

| 6.6:                 | Original MDES memory requirements for the four processor configurations.                                                                                                                                                        |      |

| 6.7:                 | MDES memory requirements after eliminating redundant and unused                                                                                                                                                                 |      |

| 6.8:                 | information                                                                                                                                                                                                                     |      |

| 6.9:                 | MDES size characteristics before and after a bit-vector representation is used (one cycle/word).                                                                                                                                |      |

| 6.10:                | Scheduling characteristics before and after a bit-vector representation is used (one cycle/word).                                                                                                                               |      |

| 6.11:                | MDES memory requirements before and after transforming resource usage times (one cycle per word).                                                                                                                               |      |

| 6.12:                | Scheduling characteristics before and after transforming resource usage times and sorting the resulting usages to check time zero first (one cycle per word).                                                                   |      |

| 6.13:                |                                                                                                                                                                                                                                 |      |

| 6.14:                |                                                                                                                                                                                                                                 |      |

| 6.15:                | Aggregate effect of all transformations on MDES scheduling characteristics                                                                                                                                                      |      |

| 7.1:<br>7.2:<br>7.3: | Compile time using the HP C Compiler on the SPEC CINT92 benchmarks  Compile time using the HP C Compiler on the SPEC CINT95 benchmarks  Time required to list-schedule all control blocks using the DHASY scheduling heuristic. | 191  |

| 7.4: | A breakdown of the time required by the components of the schedule-time |       |

|------|-------------------------------------------------------------------------|-------|

|      | transformation algorithm utilizing the optimized four-issue MDES        | . 196 |

| 7.5: | Projection of time requirements for future schedule-time transformation |       |

|      | loads for the four-issue processor configuration                        | . 200 |

# LIST OF FIGURES

| Figure |                                                                                                                                                                                          | Page |

|--------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|

| 1.1:   | Example of the renaming-with-copy transformation                                                                                                                                         | 2    |

| 1.2:   | Example of the integer-expression-reformulation transformation                                                                                                                           | 4    |

| 2.1:   | Example of the lifetime renaming transformation.                                                                                                                                         |      |

| 2.2:   | An example of the renaming-with-copy transformation                                                                                                                                      |      |

| 2.3:   | An example of renaming with copy increasing dependence height                                                                                                                            |      |

| 2.4:   | Two examples of integer expression reformulation.                                                                                                                                        |      |

| 2.5:   | The effect of parallelizing expressions on code performance                                                                                                                              |      |

| 2.6:   | Example applications of integer expression reformulation                                                                                                                                 |      |

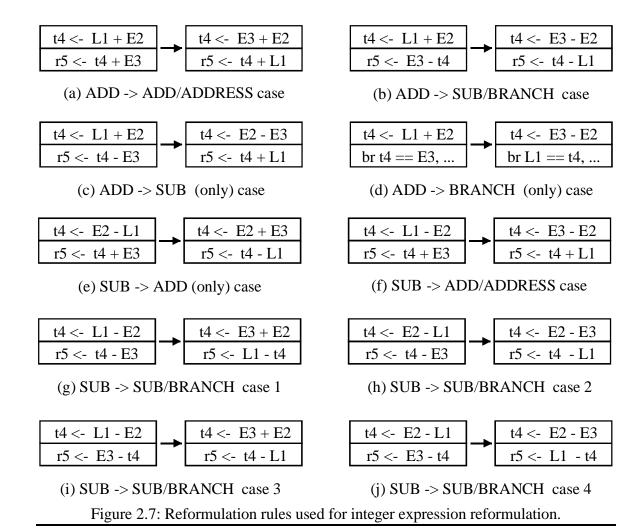

| 2.7:   | Reformulation rules used for integer expression reformulation                                                                                                                            |      |

| 2.8:   | Example of making the reformulation rules assumptions true                                                                                                                               |      |

| 2.9:   | An example of more accurate information being available at schedule time                                                                                                                 | 21   |

| 3.1:   | Schedule-based application algorithm.                                                                                                                                                    | 24   |

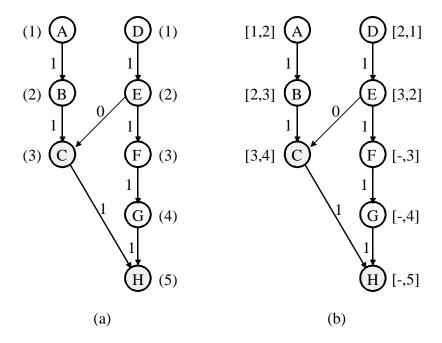

| 3.2:   | An example dependence graph indicating each operation's (a) early time and (b) late times                                                                                                | 29   |

| 3.3:   | Algorithm for calculating the early time for each operation in a control block                                                                                                           | 30   |

| 3.4:   | Algorithm for calculating the late times for each operation in a control                                                                                                                 |      |

| 3.5:   | block                                                                                                                                                                                    |      |

| 3.6:   |                                                                                                                                                                                          |      |

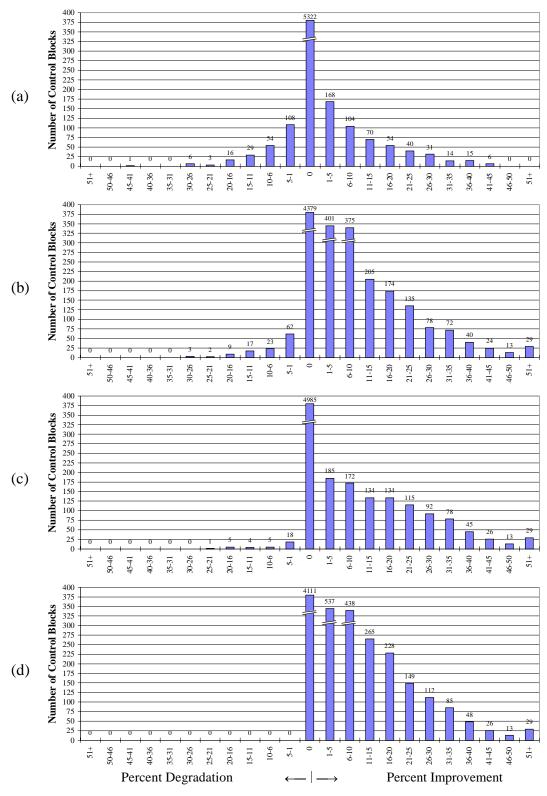

|        | (a) An example control block and (b) its dependence graph.                                                                                                                               |      |

| 3.7:   | Algorithm used to transform each control block.                                                                                                                                          | 44   |

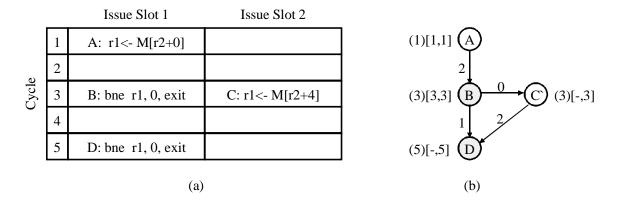

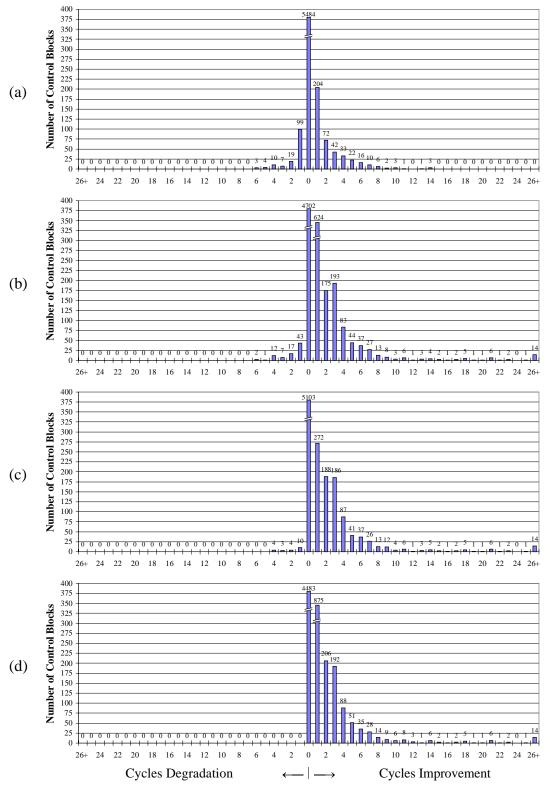

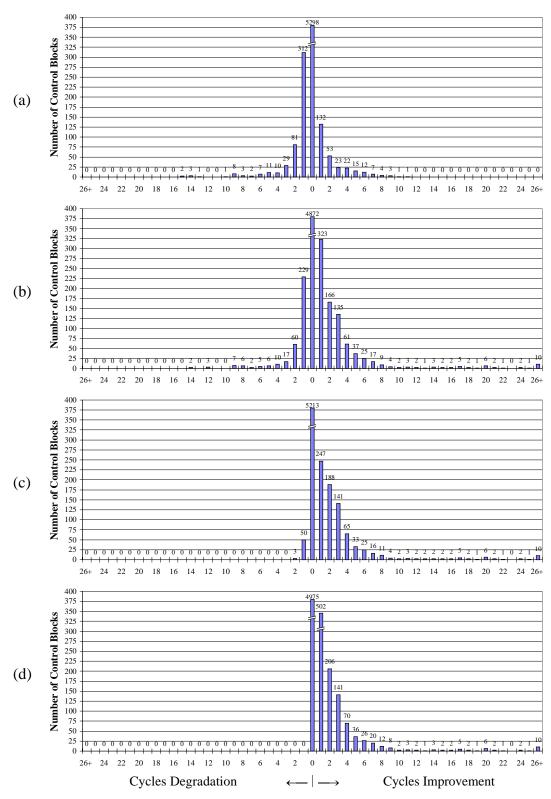

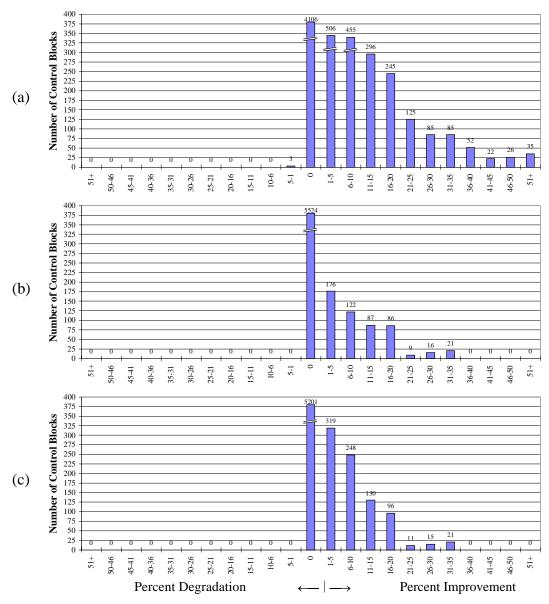

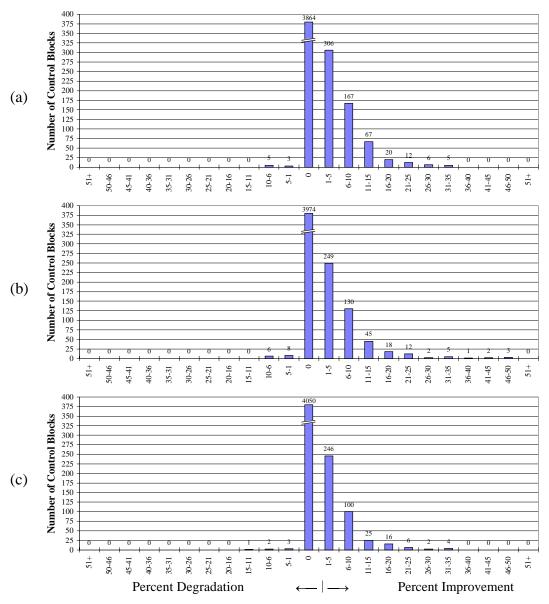

| 4.1:   | Percent change for (a) heuristic-based, (b) dependence-based, (c) estimate-based, and (d) schedule-based application of renaming with copy for the                                       |      |

|        | four-issue processor configuration.                                                                                                                                                      | 59   |

| 4.2:   | Change in cycles for (a) heuristic-based, (b) dependence-based, (c) estimate-based, and (d) schedule-based application of renaming with copy for the four-issue processor configuration. | 62   |

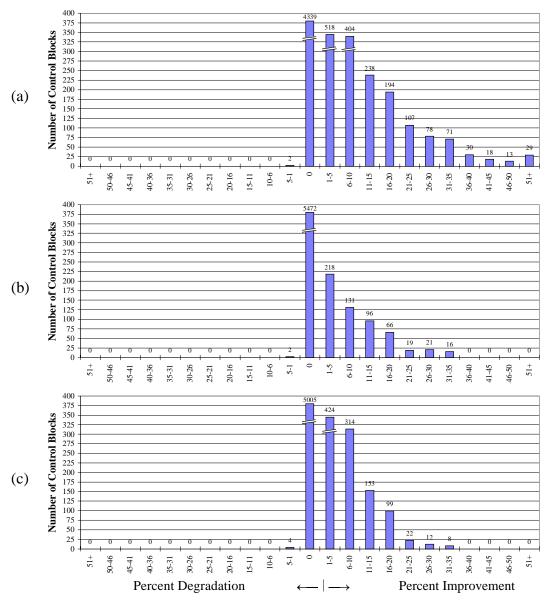

| 4.3:   | Percent benefit of schedule-based application over (a) heuristic-based,                                                                                                                  | 02   |

| 1.5.   | (b) dependence-based, and (c) estimate-based application of renaming with                                                                                                                |      |

| 1 1.   | copy for the four-issue processor configuration.                                                                                                                                         | 04   |

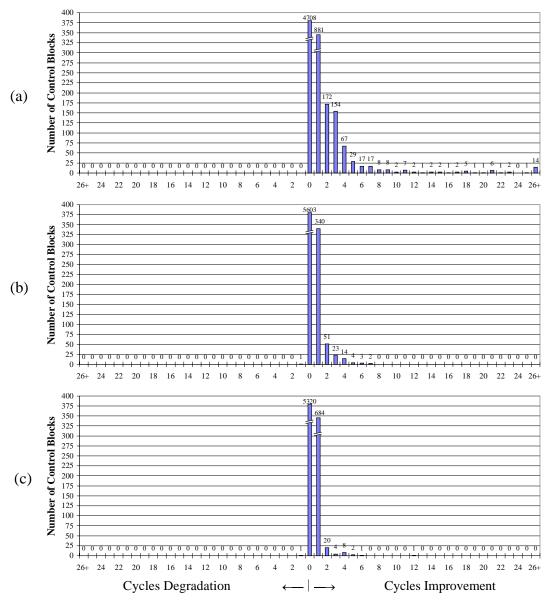

| 4.4:   | Benefit in cycles of schedule-based application over (a) heuristic-based, (b) dependence-based, and (c) estimate-based application of renaming with                                      |      |

|        | copy for the four-issue processor configuration.                                                                                                                                         | 66   |

| 4.5:   | Percent change for (a) heuristic-based, (b) dependence-based, (c) estimate-                                                                                                              |      |

|        | based, and (d) schedule-based application of renaming with copy for the                                                                                                                  |      |

|        | two-issue processor configuration.                                                                                                                                                       | 69   |

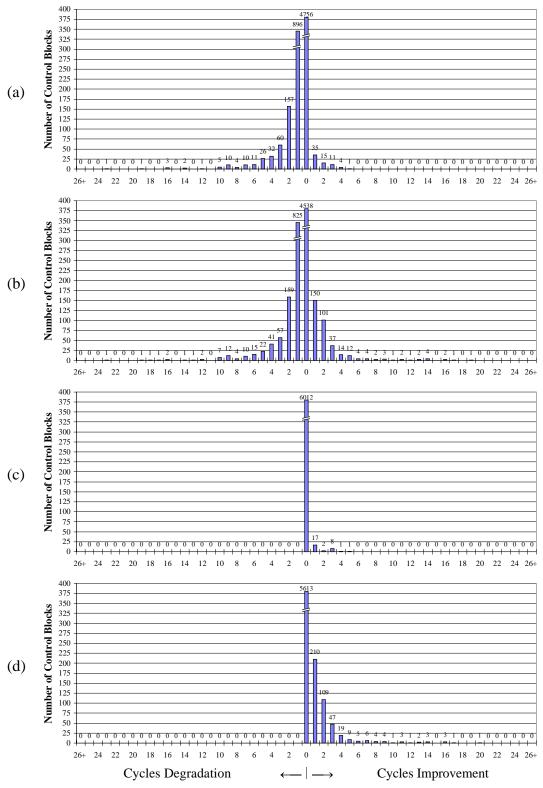

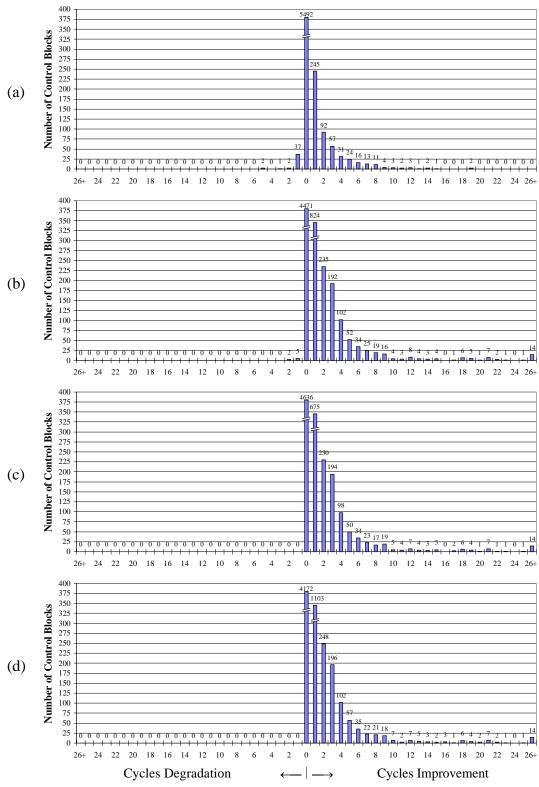

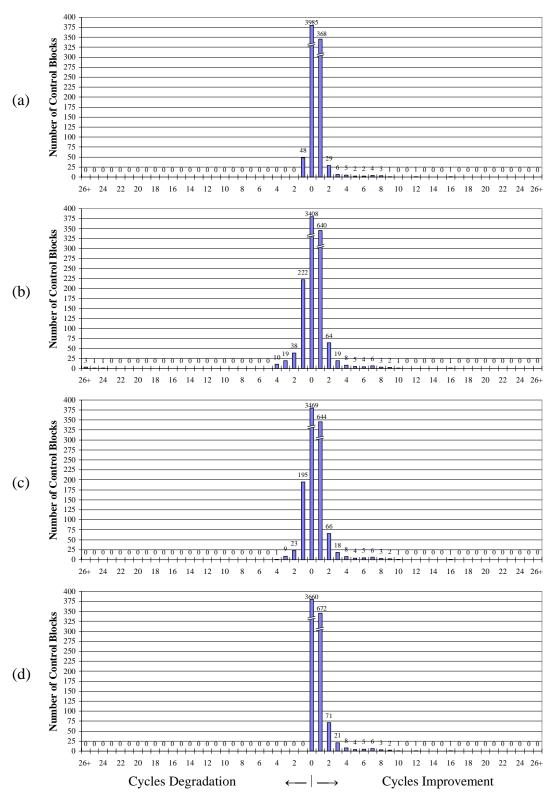

| 4.6:  | Change in cycles for (a) heuristic-based, (b) dependence-based,             |     |

|-------|-----------------------------------------------------------------------------|-----|

|       | (c) estimate-based, and (d) schedule-based application of renaming with     |     |

|       | copy for the two-issue processor configuration                              | 71  |

| 4.7:  | Percent change for (a) heuristic-based, (b) dependence-based, (c) estimate- |     |

|       | based, and (d) schedule-based application of renaming with copy for the     |     |

|       | one-issue processor configuration.                                          | 73  |

| 4.8:  | Change in cycles for (a) heuristic-based, (b) dependence-based,             |     |

|       | (c) estimate-based, and (d) schedule-based application of renaming with     |     |

|       | copy for the one-issue processor configuration.                             | 75  |

| 4.9:  | Percent change for (a) heuristic-based, (b) dependence-based, (c) estimate- |     |

|       | based, and (d) schedule-based application of renaming with copy for the     |     |

|       | $\mathcal{E}$                                                               | 77  |

| 4.10: | Percent benefit of schedule-based application over (a) heuristic-based,     |     |

|       | (b) dependence-based, and (c) estimate-based application of renaming with   |     |

|       | copy for the eight-issue processor configuration.                           | 80  |

| 4.11: | Change in cycles for (a) heuristic-based, (b) dependence-based,             |     |

|       | (c) estimate-based, and (d) schedule-based application of renaming with     |     |

|       | copy for the eight-issue processor configuration.                           | 82  |

| 4.12: | Benefit in cycles of schedule-based application over (a) heuristic-based,   |     |

|       | (b) dependence-based, and (c) estimate-based application of renaming with   |     |

|       | copy for the eight-issue processor configuration.                           | 83  |

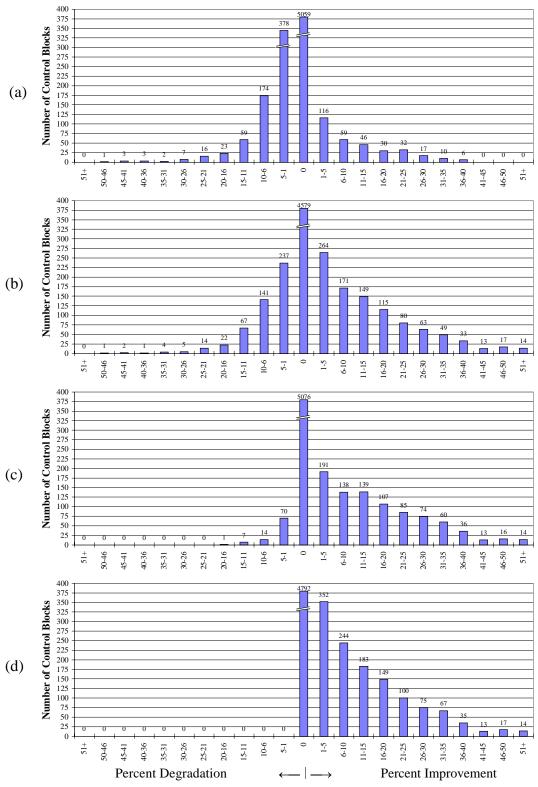

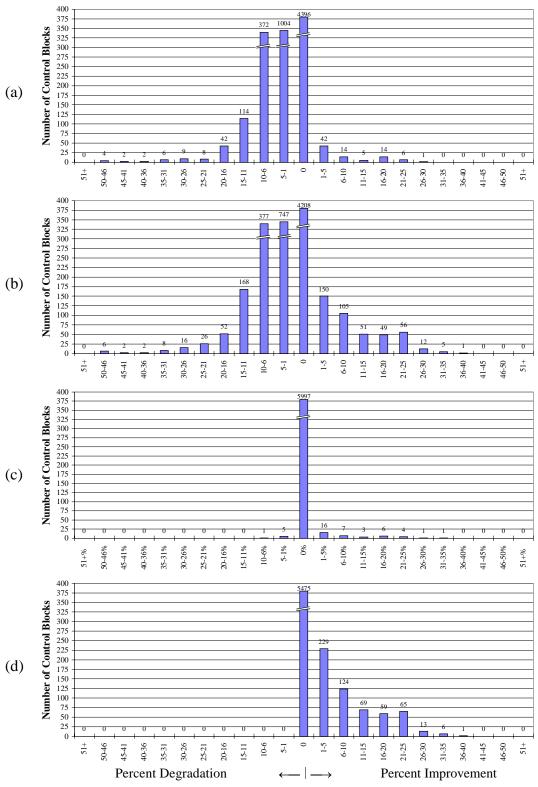

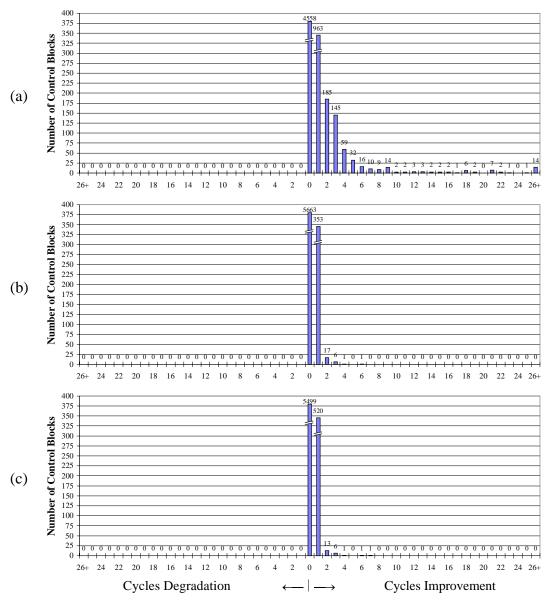

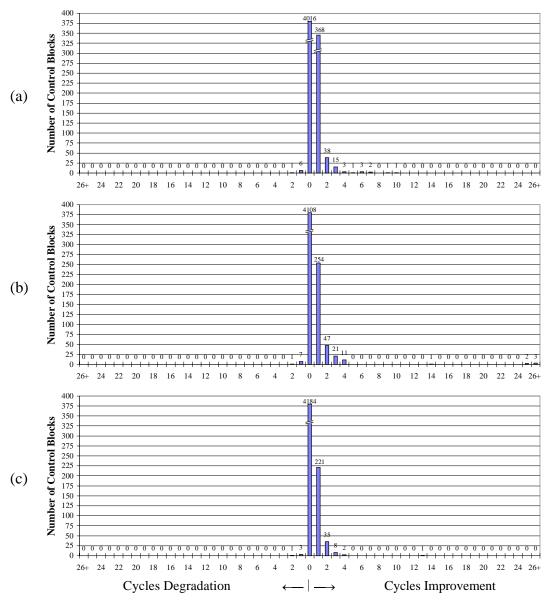

| 4.13: | Percent change for (a) heuristic-based, (b) dependence-based, (c) estimate- |     |

|       | based, and (d) schedule-based application of expression reformulation for   |     |

|       | the four-issue processor configuration.                                     | 86  |

| 4.14: | Percent benefit of schedule-based application over (a) heuristic-based,     |     |

|       | (b) dependence-based, and (c) estimate-based application of expression      |     |

|       | reformulation for the four-issue processor configuration                    | 90  |

| 4.15: | Change in cycles for (a) heuristic-based, (b) dependence-based,             |     |

|       | (c) estimate-based, and (d) schedule-based application of expression        |     |

|       | reformulation for the four-issue processor configuration.                   | 93  |

| 4.16: | Benefit in cycles of schedule-based application over (a) heuristic-based,   |     |

|       | (b) dependence-based, and (c) estimate-based application of expression      |     |

|       | reformulation for the four-issue processor configuration.                   | 94  |

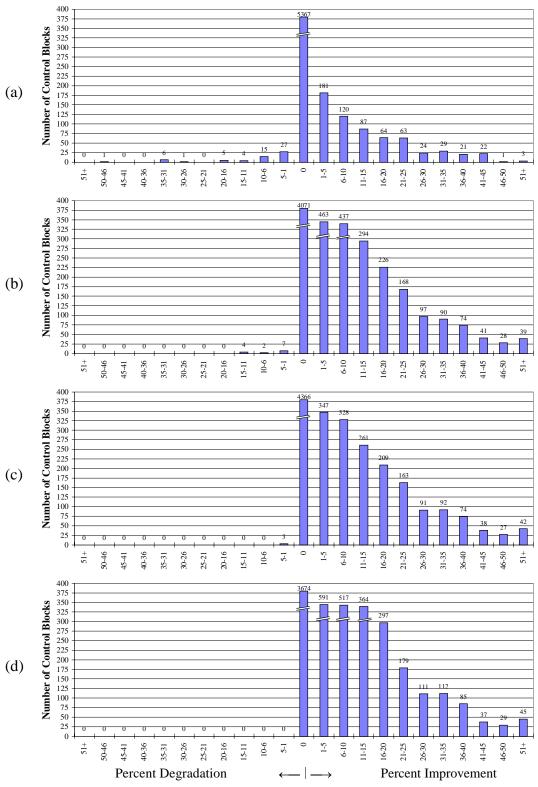

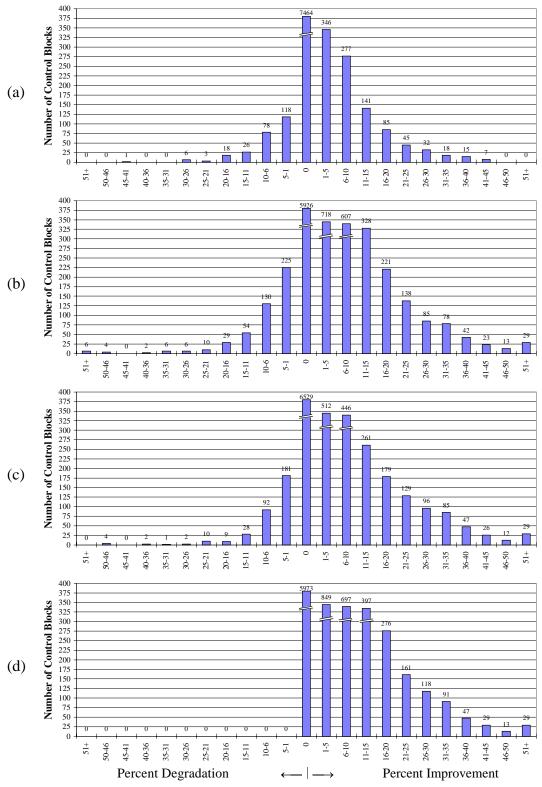

| 4.17: | Percent change for (a) heuristic-based, (b) dependence-based, (c) estimate- |     |

|       | based, and (d) schedule-based application of both transformations for the   |     |

|       | four-issue processor configuration.                                         | 96  |

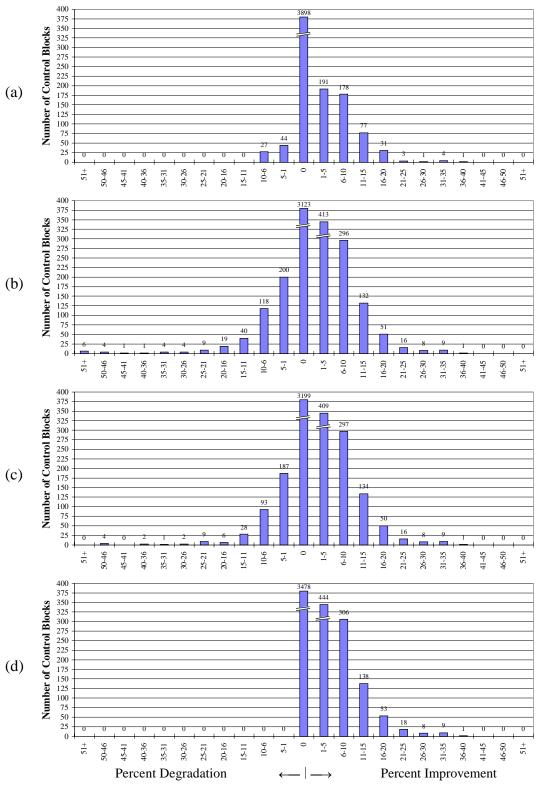

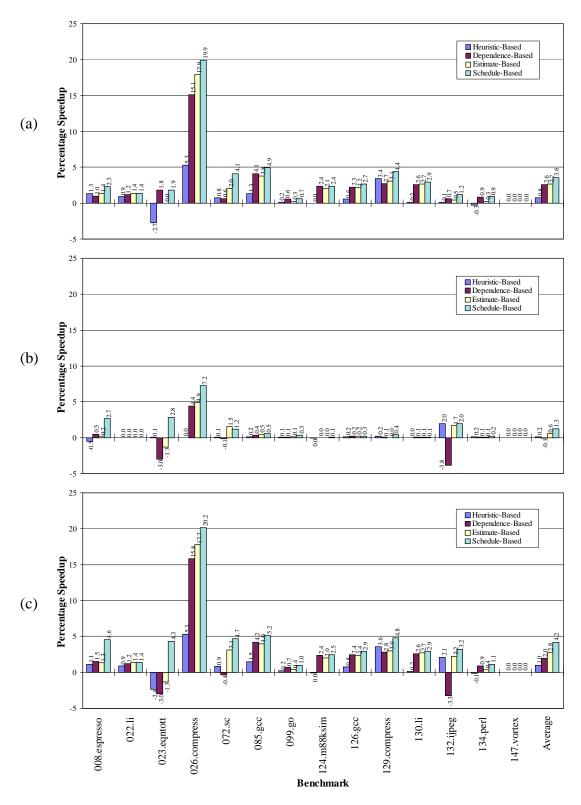

| 4.18: | Speedup due to the application of (a) renaming with copy, (b) expression    |     |

|       | reformulation, and (c) both transformations for the four-issue processor    | 100 |

| 4.40  | configuration                                                               | 102 |

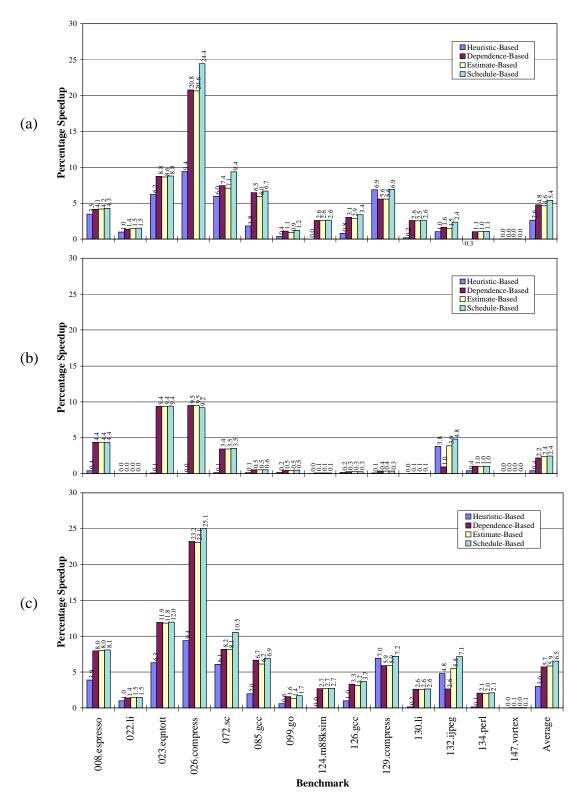

| 4.19: | Speedup due to the application of (a) renaming with copy, (b) expression    |     |

|       | reformulation, and (c) both transformations for the eight-issue processor   | 110 |

| 4.20  | configuration.                                                              | 110 |

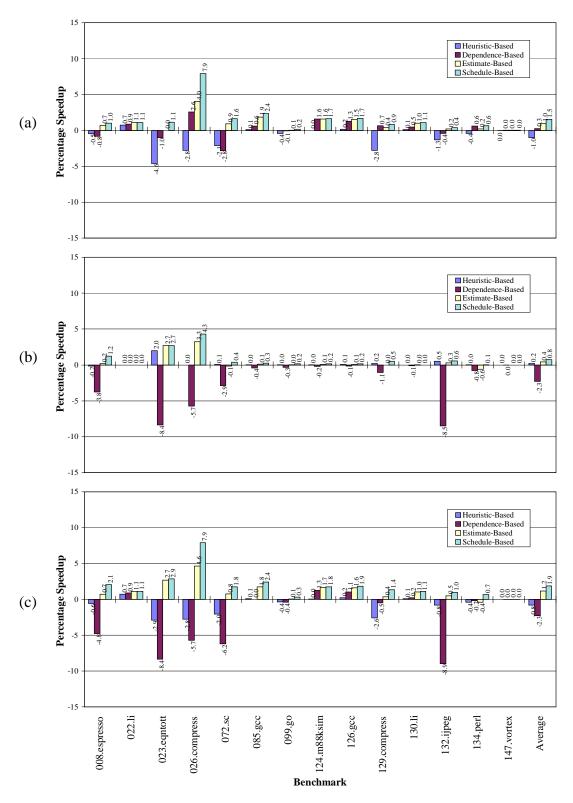

| 4.20: | Speedup due to the application of (a) renaming with copy, (b) expression    |     |

|       | reformulation, and (c) both transformations for the two-issue processor     |     |

|       | configuration.                                                              | 112 |

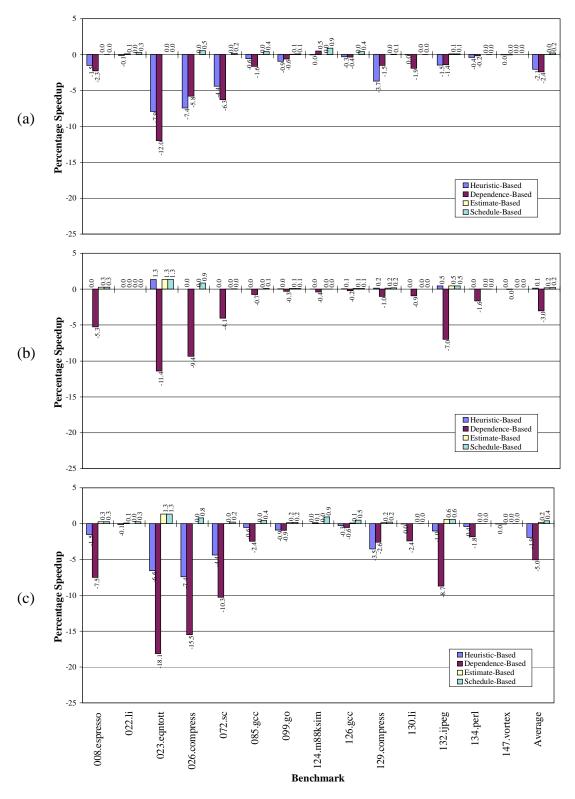

| 4.21:          | Speedup due to the application of (a) renaming with copy, (b) expression reformulation, and (c) both transformations for the one-issue processor configuration. | 115   |

|----------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------|-------|

| 5.1:           | An example code segment and its register action table.                                                                                                          | 119   |

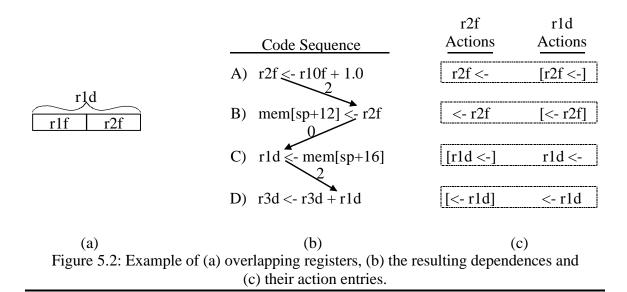

| 5.2:           | Example of (a) overlapping registers, (b) the resulting dependences and                                                                                         | 100   |

| <i>-</i> 2     | (c) their action entries.                                                                                                                                       |       |

| 5.3:           | Algorithm for building enhanced linked lists                                                                                                                    |       |

| 5.4:           | Algorithm for deleting action entry from register action table                                                                                                  |       |

| 5.5:<br>5.6:   | Algorithm for adding action entry to register action table                                                                                                      |       |

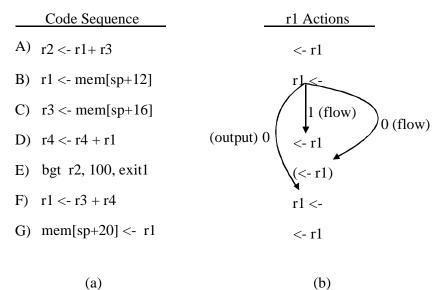

|                | dependences.                                                                                                                                                    | 136   |

| 5.7:           | (a) An example code segment and (b) the resulting action entries for Register r1 with the outgoing dependences drawn for the definition of                      |       |

|                | Register r1 in Operation B                                                                                                                                      | 137   |

| 5.8:           | Simplified algorithm for building incoming destination register dependences.                                                                                    | . 139 |

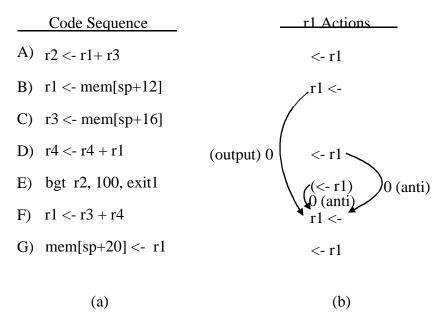

| 5.9:           | (a) An example code segment and (b) the resulting action entries for                                                                                            | 107   |

|                | Register r1 with the incoming dependences drawn for the definition of Register r1 in Operation F.                                                               | 1.40  |

| 5 10.          |                                                                                                                                                                 |       |

| 5.10:<br>5.11: | Simplified algorithm for building outgoing source register dependences                                                                                          | 141   |

| J.11.          | Register r1 with the only outgoing dependence drawn for the use of                                                                                              |       |

|                | Register r1 in Operation D.                                                                                                                                     | 1/11  |

| 5.12:          | Simplified algorithm for building incoming source register dependences                                                                                          |       |

| 5.12:          | (a) An example code segment and (b) the resulting action entries for                                                                                            | 172   |

| 3.13.          | Register r1 with the only incoming dependence drawn for the use of                                                                                              | 1.40  |

| 5 1 1.         | Register r1 in Operation D                                                                                                                                      |       |

| 5.14:          |                                                                                                                                                                 | 144   |

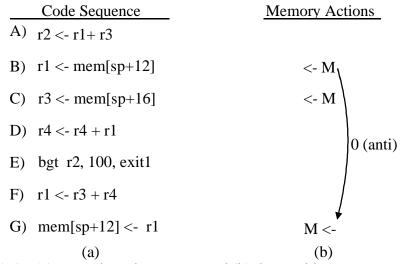

| 5.15:          | (a) An example code segment and (b) the resulting memory action entries with the only outgoing memory dependence drawn for Operation B                          | 111   |

| 5.16:          | Enhanced algorithm for building outgoing source register dependences that                                                                                       | 144   |

| 5.10.          | supports overlapping registers                                                                                                                                  | 1.45  |

| 5.17:          | (a) Example of overlapping register and (b) the register anti dependences                                                                                       | 143   |

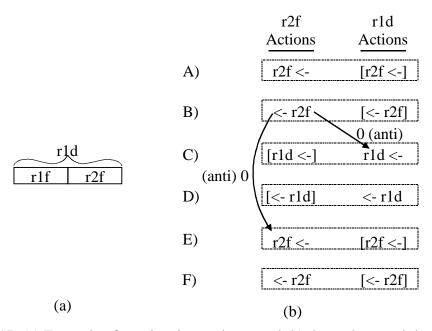

| 3.17.          | drawn for the use of r2f in Operation B.                                                                                                                        | 146   |

| 5.18:          | Enhanced algorithm for building outgoing source register dependences that                                                                                       | 140   |

| J.10.          | supports predicated execution.                                                                                                                                  | 1/10  |

| 5 10.          | Simplified algorithm for deleting a source register action entry and                                                                                            | 140   |

| 5.19:          | incrementally updating the dependence graph.                                                                                                                    | 150   |

| 5.20:          | Simplified algorithm for adding a source register action entry and                                                                                              | 130   |

| J.2U.          | incrementally updating the dependence graph.                                                                                                                    | 150   |

| 5.21:          | • 1 0 1                                                                                                                                                         | 130   |

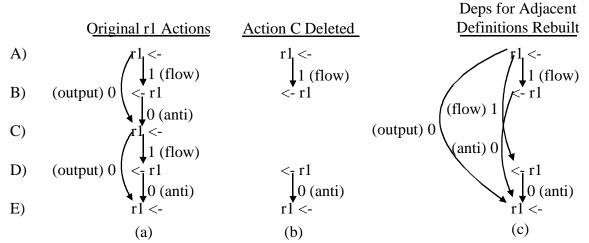

| J.Z1:          | Simplified algorithm for deleting a destination register action entry and incrementally updating the dependence graph.                                          | 151   |

|                | merementary updating the dependence graph                                                                                                                       | 1.7.1 |

| 5.22: | Action C is deleted, and (c) after rebuilding dependences for adjacent definitions (Actions A and E).                                                                                                                           | 152 |

|-------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

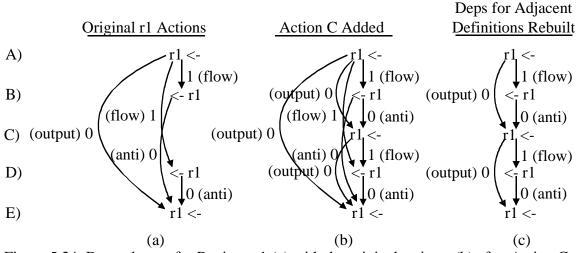

| 5.23: | Simplified algorithm for adding a destination register action entry and incrementally updating the dependence graph.                                                                                                            | 153 |

| 5.24: | Dependences for Register r1 (a) with the original actions, (b) after Action C is added, and (c) after rebuilding dependences for adjacent definitions (Actions A and E).                                                        | 153 |

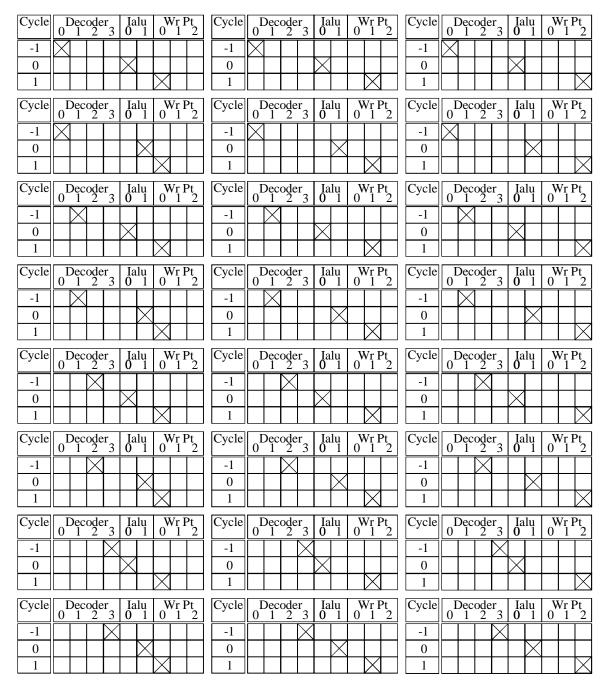

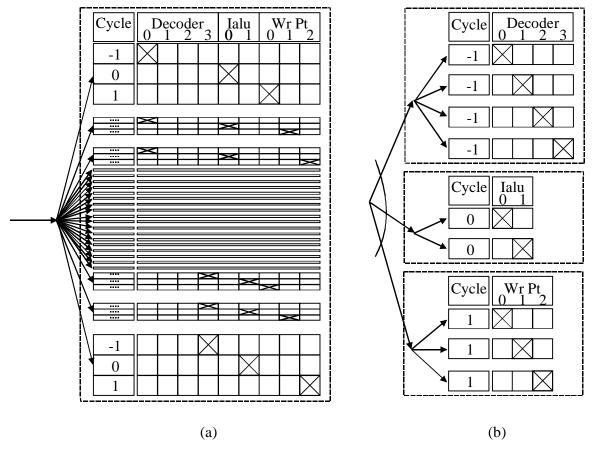

| 6.1:  | The twenty-four reservation tables that represent the resources used by the four-issue processor configuration's integer literal load operation                                                                                 | 161 |

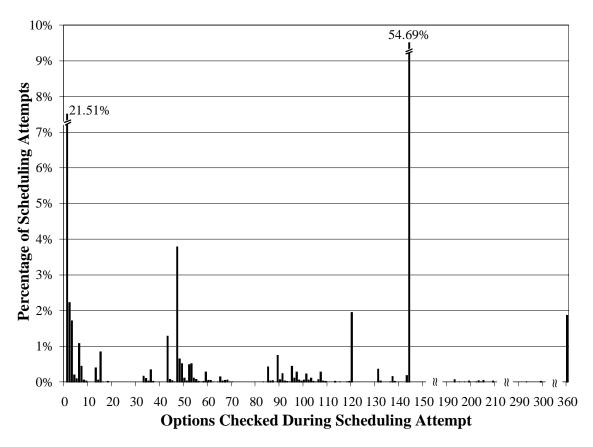

| 6.2:  | Distribution of options checked during each scheduling attempt using the four-issue processor configuration.                                                                                                                    | 164 |

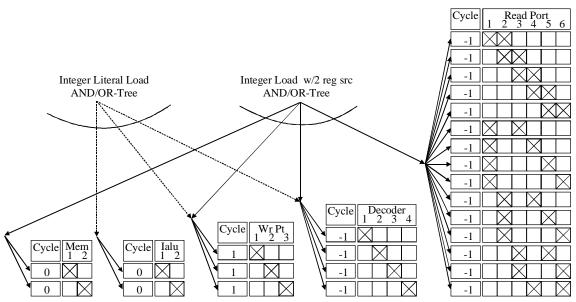

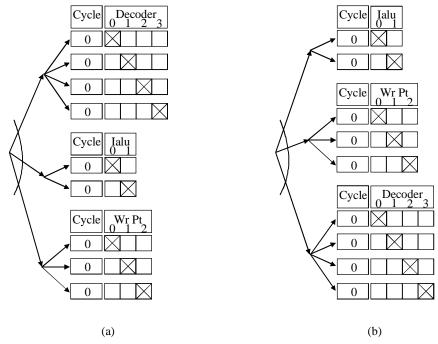

| 6.3:  | Two methods of modeling the resource constraints of the four-issue processor configuration's integer literal load operation. (a) The traditional OR-Tree representation. (b) The proposed AND/OR-Tree representation            | 166 |

| 6.4:  | An example of how the AND/OR-tree representation can facilitate the sharing of OR-trees.                                                                                                                                        |     |

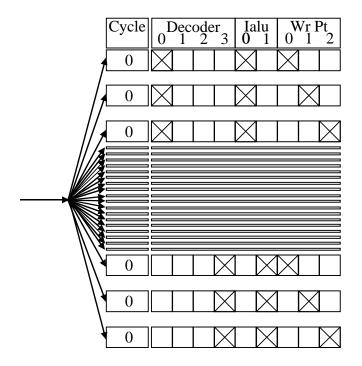

| 6.5:  | The OR-tree modeling the resource constraints for the four-issue processor configuration's integer literal load operation, after transforming the resource usage times in order to better utilize the bit-vector representation |     |

| 6.6:  | An example of optimizing the order of the OR-trees in an AND/OR-tree for resource conflict detection. (a) Original order specified. (b) After optimizing the order.                                                             |     |

| A.1:  | Percent change for (a) heuristic-based, (b) dependence-based, (c) estimate-based, and (d) schedule-based application of renaming with copy for the one-issue processor configuration                                            | 206 |

| A.2:  | Percent benefit of schedule-based application over (a) heuristic-based, (b) dependence-based, and (c) estimate-based application of renaming with copy for the one-issue processor configuration.                               | 207 |

| A.3:  | Percent change for (a) heuristic-based, (b) dependence-based, (c) estimate-based, and (d) schedule-based application of expression reformulation for                                                                            | 208 |

| A.4:  | the one-issue processor configuration                                                                                                                                                                                           | 208 |

| A.5:  | Percent change for (a) heuristic-based, (b) dependence-based, (c) estimate-based, and (d) schedule-based application of both transformations for the one-issue processor configuration.                                         | 210 |

| A.6:  | Percent benefit of schedule-based application over (a) heuristic-based, (b) dependence-based, and (c) estimate-based application of both transformations for the one-issue processor configuration                              |     |

| A.7:  | Change in cycles for (a) heuristic-based, (b) dependence-based,             |      |

|-------|-----------------------------------------------------------------------------|------|

|       | (c) estimate-based, and (d) schedule-based application of renaming with     |      |

|       | copy for the one-issue processor configuration.                             | 212  |

| A.8:  | Benefit in cycles of schedule-based application over (a) heuristic-based,   |      |

|       | (b) dependence-based, and (c) estimate-based application of renaming with   |      |

|       | copy for the one-issue processor configuration.                             | 213  |

| A.9:  | Change in cycles for (a) heuristic-based, (b) dependence-based,             |      |

|       | (c) estimate-based, and (d) schedule-based application of expression        |      |

|       | reformulation for the one-issue processor configuration                     | 214  |

| A.10: | Benefit in cycles of schedule-based application over (a) heuristic-based,   |      |

|       | (b) dependence-based, and (c) estimate-based application of expression      |      |

|       | reformulation for the one-issue processor configuration                     | 215  |

| A.11: | Change in cycles for (a) heuristic-based, (b) dependence-based,             |      |

|       | (c) estimate-based, and (d) schedule-based application of both              |      |

|       | transformations for the one-issue processor configuration                   | 216  |

| A.12: | Benefit in cycles of schedule-based application over (a) heuristic-based,   |      |

|       | (b) dependence-based, and (c) estimate-based application of both            |      |

|       | transformations for the one-issue processor configuration                   | 217  |

| A.13: | Percent change for (a) heuristic-based, (b) dependence-based, (c) estimate- |      |

|       | based, and (d) schedule-based application of renaming with copy for the     |      |

|       | two-issue processor configuration.                                          | 218  |

| A.14: | Percent benefit of schedule-based application over (a) heuristic-based,     |      |

|       | (b) dependence-based, and (c) estimate-based application of renaming with   |      |

|       | copy for the two-issue processor configuration.                             | 219  |

| A.15: | Percent change for (a) heuristic-based, (b) dependence-based, (c) estimate- | = 17 |

|       | based, and (d) schedule-based application of expression reformulation for   |      |

|       | the two-issue processor configuration                                       | 220  |

| A.16: | Percent benefit of schedule-based application over (a) heuristic-based,     | •    |

|       | (b) dependence-based, and (c) estimate-based application of expression      |      |

|       | reformulation for the two-issue processor configuration.                    | 221  |

| A.17: | Percent change for (a) heuristic-based, (b) dependence-based, (c) estimate- |      |

|       | based, and (d) schedule-based application of both transformations for the   |      |

|       | two-issue processor configuration.                                          | 222  |

| A.18: | Percent benefit of schedule-based application over (a) heuristic-based,     |      |

|       | (b) dependence-based, and (c) estimate-based application of both            |      |

|       | transformations for the two-issue processor configuration.                  | 223  |

| A.19: |                                                                             |      |

|       | (c) estimate-based, and (d) schedule-based application of renaming with     |      |

|       | copy for the two-issue processor configuration                              | 224  |

| A.20: | Benefit in cycles of schedule-based application over (a) heuristic-based,   |      |

|       | (b) dependence-based, and (c) estimate-based application of renaming with   |      |

|       | copy for the two-issue processor configuration                              | 225  |

| A.21: | Change in cycles for (a) heuristic-based, (b) dependence-based,             |      |

|       | (c) estimate-based, and (d) schedule-based application of expression        |      |

|       | reformulation for the two-issue processor configuration.                    | 226  |

|       | 1 0                                                                         |      |

| A.22:  | Benefit in cycles of schedule-based application over (a) heuristic-based,   |     |

|--------|-----------------------------------------------------------------------------|-----|

|        | (b) dependence-based, and (c) estimate-based application of expression      |     |

|        | reformulation for the two-issue processor configuration.                    | 227 |

| A.23:  | Change in cycles for (a) heuristic-based, (b) dependence-based,             |     |

|        | (c) estimate-based, and (d) schedule-based application of both              |     |

|        | transformations for the two-issue processor configuration.                  | 228 |

| A.24:  |                                                                             |     |

| 11.21. | (b) dependence-based, and (c) estimate-based application of both            |     |

|        | transformations for the two-issue processor configuration.                  | 229 |

| ۸ 25٠  | Percent change for (a) heuristic-based, (b) dependence-based, (c) estimate- | 22) |

| A.25:  |                                                                             |     |

|        | based, and (d) schedule-based application of renaming with copy for the     | 220 |

| 1.06   | four-issue processor configuration.                                         | 230 |

| A.26:  | Percent benefit of schedule-based application over (a) heuristic-based,     |     |

|        | (b) dependence-based, and (c) estimate-based application of renaming with   |     |

|        | copy for the four-issue processor configuration.                            | 231 |

| A.27:  | Percent change for (a) heuristic-based, (b) dependence-based, (c) estimate- |     |

|        | based, and (d) schedule-based application of expression reformulation for   |     |

|        | the four-issue processor configuration.                                     | 232 |

| A.28:  | Percent benefit of schedule-based application over (a) heuristic-based,     |     |

|        | (b) dependence-based, and (c) estimate-based application of expression      |     |

|        | reformulation for the four-issue processor configuration                    | 233 |

| A.29:  | Percent change for (a) heuristic-based, (b) dependence-based, (c) estimate- |     |

|        | based, and (d) schedule-based application of both transformations for the   |     |

|        | four-issue processor configuration.                                         | 234 |

| A.30:  | Percent benefit of schedule-based application over (a) heuristic-based,     |     |

|        | (b) dependence-based, and (c) estimate-based application of both            |     |

|        | transformations for the four-issue processor configuration                  | 235 |

| A.31:  | Change in cycles for (a) heuristic-based, (b) dependence-based,             |     |

|        | (c) estimate-based, and (d) schedule-based application of renaming with     |     |

|        | copy for the four-issue processor configuration.                            | 236 |

| A.32:  | Benefit in cycles of schedule-based application over (a) heuristic-based,   |     |

|        | (b) dependence-based, and (c) estimate-based application of renaming with   |     |

|        | copy for the four-issue processor configuration.                            | 237 |

| A.33:  | Change in cycles for (a) heuristic-based, (b) dependence-based,             | 0,  |

| 11.00. | (c) estimate-based, and (d) schedule-based application of expression        |     |

|        | reformulation for the four-issue processor configuration                    | 238 |

| Δ 3/1. | Benefit in cycles of schedule-based application over (a) heuristic-based,   | 250 |

| П.Эт.  | (b) dependence-based, and (c) estimate-based application of expression      |     |

|        | reformulation for the four-issue processor configuration                    | 239 |

| ۸ 25.  | <u> </u>                                                                    | 239 |

| A.35:  |                                                                             |     |

|        | (c) estimate-based, and (d) schedule-based application of both              | 240 |

| 1 26   | transformations for the four-issue processor configuration.                 | 240 |

| A.36:  | Benefit in cycles of schedule-based application over (a) heuristic-based,   |     |

|        | (b) dependence-based, and (c) estimate-based application of both            |     |

|        | transformations for the four-issue processor configuration                  | 241 |

| A.37:  | Percent change for (a) heuristic-based, (b) dependence-based, (c) estimate-based, and (d) schedule-based application of renaming with copy for the |     |

|--------|----------------------------------------------------------------------------------------------------------------------------------------------------|-----|

|        | eight-issue processor configuration.                                                                                                               | 242 |

| A.38:  | Percent benefit of schedule-based application over (a) heuristic-based,                                                                            |     |

|        | (b) dependence-based, and (c) estimate-based application of renaming with                                                                          |     |

|        | copy for the eight-issue processor configuration.                                                                                                  | 243 |

| A.39:  | Percent change for (a) heuristic-based, (b) dependence-based, (c) estimate-                                                                        |     |

|        | based, and (d) schedule-based application of expression reformulation for                                                                          |     |

|        | the eight-issue processor configuration.                                                                                                           | 244 |

| A.40:  | Percent benefit of schedule-based application over (a) heuristic-based,                                                                            |     |

| 11.101 | (b) dependence-based, and (c) estimate-based application of expression                                                                             |     |

|        | reformulation for the eight-issue processor configuration                                                                                          | 245 |

| A.41:  | Percent change for (a) heuristic-based, (b) dependence-based, (c) estimate-                                                                        | 273 |

| 71.11. | based, and (d) schedule-based application of both transformations for the                                                                          |     |

|        | eight-issue processor configuration.                                                                                                               | 246 |

| A.42:  | Percent benefit of schedule-based application over (a) heuristic-based,                                                                            | 270 |

| A.42.  | (b) dependence-based, and (c) estimate-based application of both                                                                                   |     |

|        | transformations for the eight-issue processor configuration                                                                                        | 247 |

| A.43:  | Change in cycles for (a) heuristic-based, (b) dependence-based,                                                                                    | 41  |

| A.43.  |                                                                                                                                                    |     |

|        | (c) estimate-based, and (d) schedule-based application of renaming with                                                                            | 248 |

| A 11.  | copy for the eight-issue processor configuration.                                                                                                  | 240 |

| A.44:  |                                                                                                                                                    |     |

|        | (b) dependence-based, and (c) estimate-based application of renaming with                                                                          | 240 |

| ۸ 15.  | copy for the eight-issue processor configuration.                                                                                                  | 249 |

| A.45:  | Change in cycles for (a) heuristic-based, (b) dependence-based,                                                                                    |     |

|        | (c) estimate-based, and (d) schedule-based application of expression                                                                               | 250 |

| A 16.  | reformulation for the eight-issue processor configuration                                                                                          | 250 |

| A.46:  | Benefit in cycles of schedule-based application over (a) heuristic-based,                                                                          |     |

|        | (b) dependence-based, and (c) estimate-based application of expression                                                                             | 251 |

| A 17.  |                                                                                                                                                    | 251 |

| A.47:  | Change in cycles for (a) heuristic-based, (b) dependence-based,                                                                                    |     |

|        | (c) estimate-based, and (d) schedule-based application of both                                                                                     | 252 |

| A 40.  | transformations for the eight-issue processor configuration                                                                                        | 252 |

| A.48:  | Benefit in cycles of schedule-based application over (a) heuristic-based,                                                                          |     |

|        | (b) dependence-based, and (c) estimate-based application of both                                                                                   | 252 |

| 1 10   | transformations for the eight-issue processor configuration                                                                                        | 253 |

| A.49:  | Speedup due to the application of (a) renaming with copy, (b) expression                                                                           |     |

|        | reformulation, and (c) both transformations for the one-issue processor                                                                            | 254 |

|        | configuration.                                                                                                                                     | 254 |

| A.50:  | Speedup due to the application of (a) renaming with copy, (b) expression                                                                           |     |

|        | reformulation, and (c) both transformations for the two-issue processor                                                                            |     |

|        | configuration.                                                                                                                                     | 255 |

| A.51:  | Speedup due to the application of (a) renaming with copy, (b) expression                                                                           |     |

|        | reformulation, and (c) both transformations for the four-issue processor                                                                           |     |

|        | configuration.                                                                                                                                     | 256 |

| A.52: | Speedup due to the application of (a) renaming with copy, (b) expression  |     |

|-------|---------------------------------------------------------------------------|-----|

|       | reformulation, and (c) both transformations for the eight-issue processor |     |

|       | configuration                                                             | 257 |

### 1. INTRODUCTION

### 1.1 Overview

To achieve the best performance from today's processors, compilers must aggressively minimize the dynamic operation count of programs through both traditional optimizations [1] and efficient use of the instruction set [2], [3]. The innate instruction-level parallelism (ILP) of the code, coupled with the use of a few ILP-enhancing transformations that minimally increase dynamic operation count, is usually sufficient to allow effective use of the limited resources in these processors. However, to get the best performance out of future resource-rich processors, aggressive ILP transformations are needed [4]. These transformations attempt to break dependences that limit ILP, often utilizing special hardware such as predicated execution or speculative execution support, and have been shown to be quite effective for future processors [5], [6], [7]. The drawback to these transformations is that they can dramatically increase dynamic instruction count, sometimes by more than a factor of two [8], [9].

For processors with moderate resources, applying these aggressive ILP transformations is currently difficult because of the large performance degradation that can occur when processor resources become overutilized. To illustrate the issues involved, a simple yet effective ILP transformation called *renaming with copy* [10] is applied to the code segment shown in Figure 1.1(a). This code segment is taken from a loop in the SPECcint92 benchmark 085.gcc that searches an array for non-NULL pointers in order to do some processing on them. The code segment is shown scheduled for a one-issue processor (indicated by the single issue slot in the figure), where the cycle in which

|                  | Issue Slot 1 |                 |  |  |  |  |  |  |

|------------------|--------------|-----------------|--|--|--|--|--|--|

|                  | 1            | r1<- M[r2+0]    |  |  |  |  |  |  |

|                  | 2            |                 |  |  |  |  |  |  |

| cle              | 3            | bne r1, 0, exit |  |  |  |  |  |  |

| $C_{\mathbf{y}}$ | 4            | r1<- M[r2+4]    |  |  |  |  |  |  |

|                  | 5            |                 |  |  |  |  |  |  |

|                  | 6            | bne r1, 0, exit |  |  |  |  |  |  |

| Issue Slot 1 |                       |  |  |  |  |  |

|--------------|-----------------------|--|--|--|--|--|

| 1            | r1<- M[r2+0]          |  |  |  |  |  |

| 2            | t1<- M[r2+4]          |  |  |  |  |  |

| 3            | bne r1, 0, exit       |  |  |  |  |  |

| 4            | r1<- t1               |  |  |  |  |  |

| 5            | bne t1, 0, exit       |  |  |  |  |  |

|              | 1<br>2<br>3<br>4<br>5 |  |  |  |  |  |

| -    | Issue Slot 1 |                 |  |  |  |  |  |

|------|--------------|-----------------|--|--|--|--|--|

|      | 1            | r1<- M[r2+0]    |  |  |  |  |  |

|      | 2            | (unavailable)   |  |  |  |  |  |

| (۵   | 3            | bne r1, 0, exit |  |  |  |  |  |

| ycle | 4            | t1<- M[r2+4]    |  |  |  |  |  |

| C    | 5            |                 |  |  |  |  |  |

|      | 6            | r1<- t1         |  |  |  |  |  |

|      | 7            | bne t1, 0, exit |  |  |  |  |  |

|      |              |                 |  |  |  |  |  |

(a) Original code

(b) After renaming with copy (c) Resources overutilized

Figure 1.1: Example of the renaming-with-copy transformation.

each operation is scheduled is shown in the left column. Each load takes two cycles and, as shown in Figure 1.1(a), the total scheduled code length for this segment is six cycles. The highlighted load in Cycle 4 is prevented from executing in Cycle 2 because the Register r1 is used by the branch in Cycle 3 and is redefined by the load. The load's destination register cannot be simply renamed because the exit code expects the non-NULL pointer to be in r1.

However, the load's destination register can be renamed, say to t1, if a copy of t1 to r1 is inserted after the load. If this renaming-with-copy transformation is done and the renamed load can be moved into Cycle 2, then the total scheduled code length for this segment can be reduced to five cycles, as shown in Figure 1.1(b). In this case, a 25% increase in dynamic operation count has resulted in a 17% performance improvement for this code segment. However, if after applying the transformation the renamed load could not be moved into Cycle 2 because of a resource constraint, then performance would instead be degraded by 17% as shown in Figure 1.1(c). In this second case, performance is lost and resources are wasted by the addition of the extra copy operation. For resource-rich processors, this second case rarely occurs and so the transformation is often applied

liberally. For moderate-resource processors, the second case occurs frequently enough that care must be taken in its application to prevent overall performance loss.

Interest in this area has recently become intense because most next-generation processors fall within this class of moderate-resource processors. Several performance projections using code compiled with the traditional approach of minimizing dynamic operations has shown poor processor utilization on these processors. For example, on a recently announced four-issue SPARC64, this compilation model has been projected to yield, ignoring cache effects, only an average of 1.52 instructions per cycle (IPC) on SPECcint92 code [11]. Although several methods of estimating resource constraints have been proposed that could be adapted to help guide application of ILP transformations [4], [12], [13], it is intrinsically more desirable to be able to use exact resource and schedule layout information. This thesis proposes a new machine-description-driven transformation framework that makes such exact information available by allowing ILP transformations to be efficiently performed and evaluated during instruction scheduling.

The primary mechanism used to evaluate each potential ILP transformation is the effect the transformation has on the scheduled height of the code segment being processed. The *scheduled height* is a common first-order execution-time estimate that takes into account the processor's resource constraints, the various data and control dependences between operations, and the algorithm used for scheduling [14]. It can be quickly calculated after instruction scheduling using profile information and the cycle in which each operation was scheduled. Although it ignores second-order effects caused by branch prediction and the memory hierarchy, it is one of the best static estimates of

|     |   | Issue Slot 1     | Issue Slot 2 |

|-----|---|------------------|--------------|

|     | 1 | r1<- r5∧r6       |              |

| cle | 2 | r2<- r1+r7       |              |

| Cy  | 3 | bgt r2, r8, exit | r3<- r2+r9   |

|     | 4 | r4<- r3∧r10      |              |

|              |   | Issue Slot 1     | Issue Slot 2 |

|--------------|---|------------------|--------------|

| ycle         | 1 | r1<- r5∧r6       | t1<- r7 + r9 |

|              | 2 | r2<- r1+r7       | r3<- r1+t1   |

| $\mathbf{C}$ | 3 | bgt r2, r8, exit | r4<- r3∧r10  |

(a) Original code

(b) After reformulation

Figure 1.2: Example of the integer-expression-reformulation transformation.

performance available and has been used extensively to show the benefit of ILP transformations [5], [15]. This evaluation mechanism facilitates the use of search algorithms to find the set of transformations that produces a heuristically minimum estimated execution time for each code segment.

In order to evaluate the benefit of the proposed framework, two important ILP transformations were implemented using this framework. Both of these transformations were already being extensively used within the IMPACT compiler [16]. However, despite extensive tuning of their application heuristics, they were found to cause performance degradation in some code segments and miss important opportunities in other code segments. The first ILP transformation, *renaming with copy*, breaks anti and output dependences on destination registers as illustrated earlier in Figure 1.1. The second ILP transformation, *integer expression reformulation*, is a form of critical path reduction [17] that reformulates integer arithmetic expressions in order to improve the performance of a code segment. In Figure 1.2(a), the value in r3 is the result of a summation of r1, r7, and r9 and is used by the calculation of r4 in Cycle 4. The value of r1 is not ready until Cycle 2, which delays the calculation of r3 in its current formulation. However, if the calculation of r3 is changed so that r1 is added last instead of first, the code segment's performance can be improved 25% as shown in Figure 1.2(b). Although

sometimes existing operations only need to be modified by this transformation, usually one or more operations need to be created in order to perform this transformation. As with renaming with copy, if these extra operations cause the processor resources to be overutilized, degraded performance can result.

Using these ILP transformations, this thesis examines in detail the performance benefits gained from using the proposed framework's exact schedule information compared to what is currently done, and to what may be possible if approximations were used instead. In order to make fair comparisons between using exact schedule information, using approximations, and using the IMPACT compiler's existing heuristics to guide the application of the ILP transformations, the proposed framework is used for all of the experiments. For the experiments involving approximations, the accuracy of the machine description used to guide the transformations is varied with respect to the processor targeted. This allows existing approaches that utilize only dependence graph information [5] or approximations based on simplified processor models [4] to be evaluated. For the experiments involving the IMPACT compiler's existing heuristics, the transformations' application heuristics were faithfully ported to the new framework from IMPACT's current ILP optimizer, which is typically invoked well before scheduling. These experiments show that only by utilizing the proposed framework's exact schedule information can a compiler achieve consistent performance improvement from the application of ILP transformations.

The first major contribution of this thesis is the proposed schedule-based application framework that facilitates the aggressive and intelligent application of execution-constraint-sensitive transformations. The proposed linear-time transformation

selection algorithm yields both significantly and consistently better performance than traditional application methods because the application of transformations can now be more fully adapted to the processor's execution constraints.

A critical issue that this thesis examines in detail is the compile-time cost of using the proposed scheduled-height-based search algorithm. For each combination of ILP transformations considered, the transformed code segment must be rescheduled in order to recalculate the scheduled height. This may result in a code segment being repeatedly scheduled, with a different set of ILP transformations applied each time. If a conventional scheduling framework is used, the compile-time cost may not be acceptable.

The second major contribution of this thesis is a set of novel techniques that drastically reduce the time required to reschedule the code segment after a set of ILP transformations has been performed. The proposed algorithm for incremental dependence graph generation allows near-constant-time updates of the dependence graph after performing each transformation. The proposed machine description optimizations generate an efficient low-level representation of the processor's complex execution constraints from a high-level machine description language. The compile-time benefits of these techniques are extensively analyzed using a highly-tuned, state-of-the-art implementation of the proposed framework.

Chapter 2 describes in detail the renaming-with-copy and integer-expression-reformulation transformations, which will be used to evaluate the proposed approach for applying transformations. Chapter 3 describes the algorithms proposed for applying transformations at schedule time and Chapter 4 compares the benchmark performance achieved using this approach to several other possible approaches. Chapter 5 describes

an algorithm for incremental dependence graph generation that significantly reduces the time required to perform schedule-time transformations. Chapter 6 describes how resource constraints are typically modeled and presents a set of novel techniques that drastically reduce the time required to perform both scheduling and schedule-time transformations. Chapter 7 evaluates the effectiveness of the above techniques in reducing the compile time and estimates the compile-time cost if an extensive set of transformations is applied at schedule-time. Chapter 8 summarizes the results of this research and describes some interesting areas for future application.

#### 2. THE ILP TRANSFORMATIONS EVALUATED

### 2.1 Introduction

This thesis examines the challenges involved in applying ILP transformations to processors with moderate resources and proposes an new framework for applying these transformations during instruction scheduling. The qualitative and quantitative benefits of applying transformations during scheduling will be analyzed using the two ILP transformations, integer expression reformulation and renaming with copy, that were briefly introduced in Chapter 1. These two transformations were selected for several reasons. The first is that the challenges involved in applying them is representative of a wide array of ILP transformations, such as memory speculation, branch combining, and promotion with copy. The second is that both of these transformations had been previously implemented in the IMPACT compiler, allowing a direct comparison to an existing application technology as well as to approaches based on approximate information. Third, in addition to a more effective application of these transformations directly improving performance, the application of these transformations also should increase the benefit of many other ILP transformations.

### 2.2 Renaming With Copy

Register anti dependences occur between the redefinition of a register's value and the uses of the register's previous value. For example in Figure 2.1(a), a register anti dependence exists between the use of Register r1 in Cycle 3 and the redefinition of Register r1 in Cycle 3. This dependence prevents the reordering of these two operations

|      |   | Issue Slot 1  | Issue Slot 2  |

|------|---|---------------|---------------|

|      | 1 | r1 <- M[r9+0] |               |

| e    | 2 |               |               |

| ycle | 3 | r2 <- r1 + r7 | r1 <- M[r8+0] |

|      | 4 |               |               |

|      | 5 | r3 <- r1 + r6 |               |

|     |   | Issue Slot 1  | Issue Slot 2  |

|-----|---|---------------|---------------|

| e   | 1 | t4 <- M[r9+0] | r1 <- M[r8+0] |

| ycl | 2 |               |               |

|     | 3 | r2 <- t4 + r7 | r3 <- r1 + r6 |

(a) Original code

(b) After renaming (no operations added)

Figure 2.1: Example of the lifetime renaming transformation.

in order to prevent the use of r1 in Cycle 3 from receiving an incorrect value. Similarly, *register output dependences* occur between the redefinition of a register's value and the definition of the register's previous value. For example in Figure 2.1(a), a register output dependence exists between the definition of Register r1 in Cycle 1 and the redefinition of Register r1 in Cycle 3. This dependence prevents the reordering of these two definitions in order to prevent the use of r1 in Cycle 5 from receiving an incorrect value. Typically, as in this example, anti dependences are more constraining than output dependences. However both types of dependences can limit instruction-level parallelism by preventing the overlap of computation.

Register renaming refers to a class of transformations that break register anti and output dependences by renaming (changing) a virtual register used by a set of operations [5]. A widely used approach, referred to as lifetime renaming, identifies all of the disjoint register lifetimes within a function and assigns each of these disjoint lifetimes a new virtual register. A register lifetime is a set of definitions and uses of a particular register where the uses only consume the values produced by definitions in the set and no uses outside the set consume the values produced by these definitions. A register lifetime can be divided up into one or more disjoint register lifetimes where each nonoverlapping

|       |   | Issue Slot 1    | Issue Slot 2 |             | Is |

|-------|---|-----------------|--------------|-------------|----|

|       | 1 | r1<- M[r2+0]    |              | 1           | r1 |

| မ     | 2 |                 |              | <u> </u>    |    |

| ycle  | 3 | bne r1, 0, exit | r1<- M[r2+4] | <u>کُ</u> 3 | bn |

|       | 4 |                 |              | 4           | bn |

|       | 5 | bne r1, 0, exit |              |             | -  |

| exit: | 1 | r4<- M[r1+0]    |              | exit: 1     | r4 |

|       |   |                 |              |             |    |

|     |   | Issue Slot 1    | Issue Slot 2 |

|-----|---|-----------------|--------------|

|     | 1 | r1<- M[r2+0]    | t3<- M[r2+4] |

| cle | 2 |                 |              |

| Cy  | 3 | bne r1, 0, exit | r1 <- t3     |

|     | 4 | bne t3, 0, exit |              |

exit: 1 r4<- M[r1+0] ...

(a) Original code

(b) After renaming with copy

Figure 2.2: An example of the renaming-with-copy transformation.

lifetime is the minimal set of definitions and uses required to form a valid register lifetime. An example of a disjoint register lifetime for Register r1 in Figure 2.1(a) is the definition of r1 in Cycle 1 and the use of r1 in Cycle 3. Assigning this disjoint register lifetime a new virtual register (Register t4) breaks the register and output dependences with the redefinition of r1 in Cycle 3, allowing more computation to be overlapped and improving performance 40% as shown in Figure 2.1(b). Because lifetime renaming always operates on disjoint register lifetimes, no fixup code (extra operations) is needed in order to perform the transformation. As one of the few ILP transformations that does not increase the program's dynamic operation count, this transformation is almost universally applied in production and research compilers.

However, register anti and output dependences can also occur between operations within the same lifetime. For example, in Figure 2.2(a), the definition of Register r1 in Cycle 1 and the definition of Register r1 in Cycle 3 reside in the same register lifetime because they both reach the same use of r1 in code labeled 'exit.' As a result, the register anti dependence between the use of r1 in Cycle 3 and the redefinition of r1 in Cycle 3 cannot be removed with lifetime renaming and another register naming transformation

|       |   | Issue Slot 1     | Issue Slot 2    |       |   | Issue Slot 1    | Issue Slot 2     |

|-------|---|------------------|-----------------|-------|---|-----------------|------------------|

| loop: | 1 | r2 <- r1         | r1 < -M[r1 + 8] | loop: | 1 | t4 < -M[r1 + 8] | r2 <- r1         |

| cle   | 2 | beq r2, r3, exit |                 | cle   | 2 |                 |                  |

| Cy    | 3 | bne r1, 0, loop  |                 | Cy    | 3 | r1 <-t4         | beq r2, r3, exit |

| •     |   |                  |                 |       | 4 | bne t4, 0, loop |                  |

(a) Original code

(b) After renaming with copy

Figure 2.3: An example of renaming with copy increasing dependence height.

must be used. Note that in all this thesis' figures, branch operations (e.g., bne r1, 0, exit in Figure 2.2(a)) are assumed to not have any delay slots and operations scheduled after the branch operation (e.g., r1 < M[r2+4]) only execute if the branch is not taken.

The renaming transformation utilized by the IMPACT compiler when lifetime renaming is not sufficient is *renaming with copy* [5]. This transformation splits a lifetime into two disjoint lifetimes, renames one of them and fixes up the other with a copy (move) operation. Applying this transformation to Figure 2.2(a) yields the code shown Figure 2.2(b). The redefinition of Register r1 in Cycle 3 and use of r1 in Cycle 5 is first renamed to a new virtual Register t3, and then an operation is added to copy the value of t3 to r1 so that the code at 'exit' always gets the proper value for r1. Applying this transformation to this code segment allows more computation to be overlapped, improving performance by 20%.

Unlike the lifetime renaming transformation, renaming with copy increases the program's dynamic operation count. As shown earlier in Figure 1.1(c), care must be taken to prevent overutilization of processor resources. Moreover, the additional copy operation can actually increase the dependence height of a code segment, degrading performance even if enough resources are available as shown in Figure 2.3. In Figure 2.3(a), the register anti dependence between the use of Register r1 and redefinition