©Copyright by

Liangchuan Hsu

1997

# A ROBUST FOUNDATION FOR BINARY TRANSLATION OF X86 CODE

### BY

### LIANGCHUAN HSU

B.S., Chung-Cheng Institute of Technology, 1986

M.S., Naval Postgraduate School, 1990

#### THESIS

Submitted in partial fulfillment of the requirements for the degree of Doctor of Philosophy in Computer Science in the Graduate College of the University of Illinois at Urbana-Champaign, 1997

Urbana, Illinois

# A ROBUST FOUNDATION FOR BINARY TRANSLATION OF X86 CODE

Liangchuan Hsu, Ph.D.

Department of Computer Science

University of Illinois at Urbana-Champaign, 1997

Wen-mei W. Hwu, Advisor

Software venders are unwilling to compile new software for a new processor until the marketplace of the processor becomes large enough. As a result, utilization of most new hardware features is delayed. Binary Translation allows programs compiled for older machines to take advantage of all the new features that have since been added. Binary translation can help introduce new instruction set architecture (ISA) features to the software base.

This dissertation develops a solid foundation for binary translation. A hybrid approach to resolving all of branch target problems is proposed and evaluated. It attempts to resolve as many targets as possible statically, and uses a run-time support when the target cannot be resolved at translation time.

Self-modifying code is one of the major hurdles to binary translation. This dissertation describes a self-modifying code detector to prevent the binary translator from translating self-modifying code. In order to illustrate the usefulness of the binary translation framework, an optimizer that improves the load time of executable is designed and implemented in the framework.

To my wife, Chiu-hua, and my children, Amy and Andy. Thank you for your love, support and longsuffering!

# Acknowledgments

First and foremost, I would like to thank my advisor, Professor Wen-mei W. Hwu, for his insight and guidance throughout my studies. Not only was it an honor to work with someone of his caliber, but it was also a pleasure. He truly cares about the needs of his students. Next, I would like to thank Sabrina. It always enjoyed having a barbecue at "Hwuville".

This research would not have been possible without the support of the IMPACT research group. Members of the group were always willing to provide any help required - from research discussions to practice talks. I deeply appreciate the assistance of Roger Bringmann, Scott Mahlke, Dave Gallagher, Richard Hank, Dan Lavery, John Gyllenhaal, David August, Andrew Hsieh, Teresa Johnson, Brian Deitrich, Le-chun Wu, Ben-Chung Cheng, and Matt Trommer.

Thanks to Kemal Ebcioglu and Eric Altman of IBM T. J. Watson Research Laboratory for their valuable discussions about the VLIW architecture. Their technical ability and insight across the entire spectrum of computer architecture are remarkable. I also would like to thank Alfons Hoogervorst, a friend I made on an internet newsgroup. He answered a lot of my questions about x86 protected-mode system programming.

Finally, I must thank my wife, Chiu-hua, and my children, Amy and Andy, for their love and support during this difficult time in graduate school. They are the ones who truly sacrificed to make my graduate studies possible. I also thank my mother-in-law, Yang, for helping to take care of our children in the past year. During the last year of my graduate studies, Chiu-hua had to return to Taiwan to resume her job. She works on week days in Taoyuan and takes

the train to Chiayi on weekends to spend time with our children. Thanks, and we are eagerly awaiting again having a complete family!

# Table of Contents

| Chapter |                 |                                                   |      |  |

|---------|-----------------|---------------------------------------------------|------|--|

| 1       | Intr            | oduction                                          | 1    |  |

| 2       | Pre             | vious Work                                        | 5    |  |

|         | 2.1             | Related Work in Industry                          | . 5  |  |

|         | 2.2             | Related Work in Academia                          | . 10 |  |

| 3       | Bac             | kground                                           | 12   |  |

| •       | 3.1             | Binary Translation Model                          |      |  |

|         | 3.2             | Executable File Header                            |      |  |

|         | 0.2             | 3.2.1 The NE Header                               |      |  |

|         |                 | 3.2.2 Tables in the NE File                       |      |  |

|         |                 | 3.2.3 Per-Segment Data Information                |      |  |

|         | 3.3             | Dynamic Linking                                   |      |  |

|         | 0.0             | Dynamic Binking                                   | 10   |  |

| 4       | $\mathbf{Bin}$  | ary Front-End                                     | 20   |  |

|         | 4.1             | Parsing Binaries                                  | . 20 |  |

|         | 4.2             | Decoding CISC Instructions                        |      |  |

|         |                 | 4.2.1 The Decoding Process                        | . 24 |  |

|         |                 | 4.2.2 Control-Flow Analysis                       | . 25 |  |

|         | 4.3             | Verifying the Decoding Process                    |      |  |

|         | 4.4             | Executing the Translated Code                     |      |  |

| 5       | Edi             | ting Binaries                                     | 35   |  |

| •       | 5.1             | Relocation for Determinable Targets               |      |  |

|         | 0.1             | 5.1.1 Intra-Segment Targets                       |      |  |

|         |                 | 5.1.2 Inter-Segment Targets                       |      |  |

|         |                 | 5.1.3 Callback Functions                          |      |  |

|         |                 | 5.1.4 Hashing Jumps with Regular Patterns         |      |  |

|         |                 | 5.1.5 Indirect DLL Function Calls                 |      |  |

|         | 5.2             | Relocation for Non-Determinable Target            |      |  |

|         | 0.2             | 5.2.1 Non-Determinable Branch Targets             |      |  |

|         |                 | 5.2.2 Adjusting Non-Determinable Branch Targets   |      |  |

|         |                 | 5.2.3 Analysis of Non-Determinable Branch Targets |      |  |

|         | 5.3             | Incremental Translation                           |      |  |

|         |                 |                                                   |      |  |

| 6       | $\mathbf{Self}$ | -Modifying Code                                   | 55   |  |

|         | 6.1             | Overview of X86 Protected Mode Architecture       |      |  |

|         | 6.2             | Detection Strategies                              |      |  |

|         | 6.3             | Handling Self-Modifying Code                      | . 62 |  |

| 7 | Pos  | st Translation                               | 66 |

|---|------|----------------------------------------------|----|

|   | 7.1  | Modification of Executable Header            | 67 |

|   | 7.2  | Modification of Executable Body              | 68 |

|   | 7.3  | Dealing with Size Expansion                  | 69 |

|   | 7.4  | Designing the New Executable File            | 73 |

| 8 | Imp  | proving the Program Load Time                | 76 |

|   | 8.1  | Description of Load Process and Costs        | 76 |

|   | 8.2  | Examples of Load Time Inefficiencies         | 79 |

|   | 8.3  | Improving the Load Time                      | 81 |

|   |      | 8.3.1 Profile-Driven Compilation             | 81 |

|   |      | 8.3.2 Executable Translation                 | 82 |

|   |      | 8.3.3 Gangload                               |    |

| 9 | Con  | aclusions                                    |    |

|   | 9.1  | Contribution                                 | 85 |

|   | 9.2  | Future Work                                  | 86 |

|   |      | 9.2.1 Performing Machine-Level Optimizations | 86 |

|   |      | 9.2.2 Removing Segment Operations            |    |

|   |      | 9.2.3 Translating 32-Bit Code                |    |

|   |      | 9.2.4 Porting 32-Bit Code to 64-Bit Code     |    |

|   | Refe | Gerences                                     | 90 |

|   | Vita | a                                            | 92 |

# List of Tables

| Tabl | e                                                                                     | Pa | age |

|------|---------------------------------------------------------------------------------------|----|-----|

| 5.1  | The percentage of non-determinable branch targets based on dynamic instruction count. |    | 51  |

| 5.2  | The percentage of non-determinable branch targets based on dynamic instruction        |    |     |

| 5.3  | count of special operations                                                           |    |     |

| 6.1  | Application segment types                                                             |    | 64  |

# List of Figures

| Figu | re                                                                             | Page |

|------|--------------------------------------------------------------------------------|------|

| 3.1  | The binary translation framework                                               | . 13 |

| 3.2  | The NE file format.                                                            | . 14 |

| 3.3  | The segment flag word in the NE file                                           | . 16 |

| 3.4  | A source program written in C                                                  | . 19 |

| 4.1  | Internal data structure for in-memory segments                                 | . 23 |

| 4.2  | Verifying the decoding process.                                                | . 27 |

| 4.3  | Operations that share the same addressing mode                                 | . 28 |

| 4.4  | Ambiguous situations in generating new binary code                             |      |

| 4.5  | An algorithm for translating and executing the new segment                     | . 30 |

| 4.6  | An algorithm for trapping each loaded segment                                  |      |

| 4.7  | Switching mechanism: a code example                                            | . 32 |

| 4.8  | Switching mechanism: the executable file                                       |      |

| 4.9  | Switching mechanism: the code in memory.                                       |      |

| 4.10 | Switching mechanism: trapping and redirecting execution flow                   | . 34 |

| 5.1  | Adjusting the branch target.                                                   | . 37 |

| 5.2  | Adjusting the inter-segment branch target                                      | . 38 |

| 5.3  | Hashing jumps with regular patterns                                            | . 41 |

| 5.4  | Example of calling a dynamically loaded function                               | . 42 |

| 5.5  | Indirect call to the dynamically loaded function (from Microsoft Word)         | . 43 |

| 5.6  | Hashing jumps with irregular patterns                                          | . 44 |

| 5.7  | A dynamically determined branch target                                         | . 45 |

| 5.8  | Branches with non-determinable targets                                         | . 45 |

| 5.9  | Replacing a non-determinable branch instruction with a VMM call                | . 46 |

| 5.10 | The address mapping table                                                      | . 48 |

| 5.11 | Internal segment data structure augmented with editing information             | . 48 |

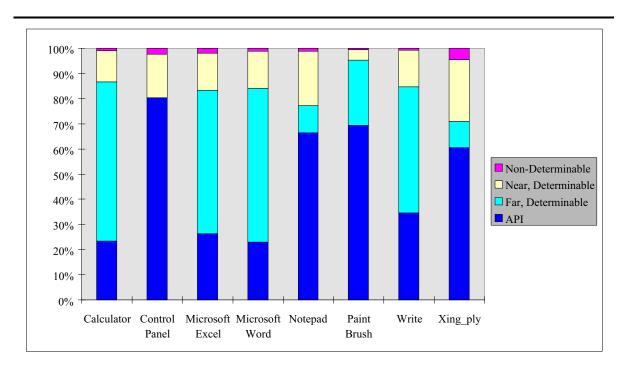

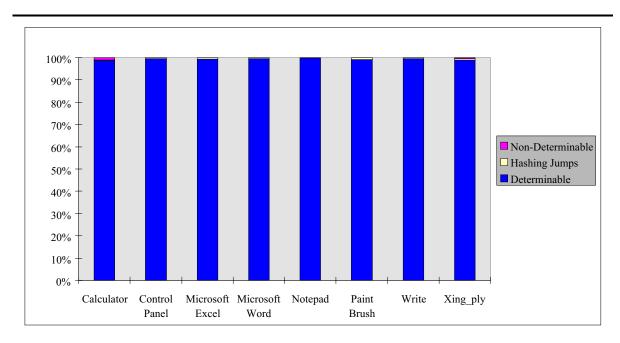

| 5.12 | Distribution of CALL instructions.                                             | . 49 |

| 5.13 | Distribution of <i>JMP</i> instructions                                        | . 50 |

| 5.14 | A code example of incremental translation ( $\mathit{CALC.EXE}$ )              | . 53 |

| 6.1  | The x86 memory address translation process.                                    | . 56 |

| 6.2  | A piece of code that generates self-modifying code.                            | . 58 |

| 6.3  | Information in selector table                                                  |      |

| 6.4  | Comparison of LDT entries: one without aliased segments in application program |      |

|      | and the other with aliased segments                                            | . 63 |

| 7.1  | Two situations resulted after segment size expansion                           |      |

| 7.2  | Comparison of original and new HELLOWIN.EXE files                              | . 74 |

| 8.1 | Segment loading distribution for MicroEmacs startup | 79 |

|-----|-----------------------------------------------------|----|

| 8.2 | Segment loading distribution for Excel startup.     | 81 |

### Chapter 1

### Introduction

Software venders are unwilling to compile new software for a new processor until the marketplace of the processor becomes large enough. For example, when the Pentium Pro was introduced to the market, most new software was still compiled for the Pentium until the Pentium Pro market matured. As a result, utilization of most new hardware features is delayed.

Also, profiling and optimizing library and third-party code often require binary translation.

The lifespan of such software is usually longer than hardware upon which it was originally developed. However, recompilation of the source code may not be possible.

Binary Translation is a technique used to transform one executable program generated for an old processor into an executable for another newer processor. This allows programs compiled for older machines to take advantage of all the new features that have since been added. Binary translation can help introduce new Instruction Set Architecture (ISA) features to the software base.

The objective of this thesis is to develop a solid foundation for binary translation. The most important problems solved in the thesis work are:

• Analyzing binary code

- Allowing code size to change

- Enabling partial translation, conservative mixed execution of original code and translated code

- Improving program load time

- Detecting self-modifying code

- Minimizing the overhead of translation

This thesis consists of 9 Chapters. Chapter 2 surveys some industry and academia related research work on binary translation. Industry primarily uses binary translation during processor development to facilitate the transformation of a code base developed for one architecture to the other architecture. Binary translation is also of academic interest and Chapter 2 explores some reasons why.

Chapter 3 introduces the framework of the binary translator presented in this thesis. Some background knowledge used throughout the thesis will be introduced in this chapter as well. Some of the background material needed throughout the thesis, such as executable file format and dynamic linking, will also be discussed in this chapter.

Chapter 4 discusses the front-end of the binary translator. The front-end deals with reading in a binary program, decoding it into an intermediate representation, and invoking the code translator. This chapter analyzes the binary code and performs control-flow analysis. In order to verify the decoding process, two essential components were implemented in the thesis: a binary code generator and a execution switching mechanism. The binary code generator produces binary code from the intermediate representation. After the translated binary code is generated,

the execution switching mechanism redirects the program control to the translated code during execution.

After decoding the original binaries, some instrumentation code may be inserted. This code is used to make measurements, such as performance of the binary code. The binary code may also be optimized. In either case, the addresses of some instructions may have to be relocated due to the change in code size. Chapter 5 discusses this instruction relocation problem. Relocation of code can affect the branch target in the translated code. This target may or may not be known during translation. This thesis proposes a hybrid approach to resolving branch target problems. The hybrid approach resolves as many targets as possible statically, and uses a run-time support when the target cannot be resolved at translation time. In order to evaluate the run-time overhead of the proposed approach, this chapter presents a detailed analysis performed over some popular benchmark programs.

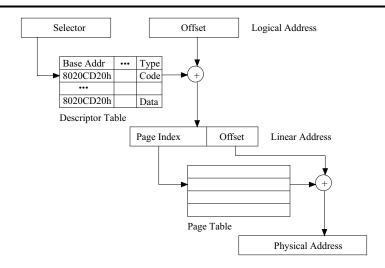

Self-modifying code is one of the major hurdles in binary translation, and by its nature is machine dependent. Since the x86 architecture was used to develop the binary translation framework in this thesis, Chapter 6 covers the x86 memory architecture description. This thesis implements a self-modifying code detector to prevent the binary translator from translating self-modifying code.

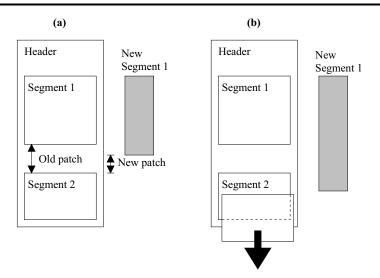

Writing the translated code to secondary storage as a new executable file marks the full translation cycle. Saving the translated code helps the translator avoid retranslating it when it is executed again. Some information dynamically maintained by the translator needs to be included in the new executable file. In order to make the new executable file work, the translator also needs to modify the original executable file when it creates the new file. Chapter 7 discusses some of these post translation issues.

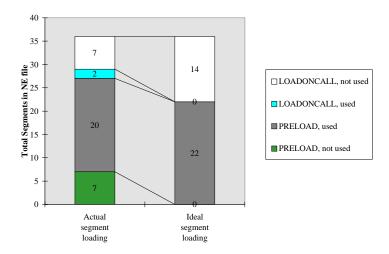

The program load time is one of the most perceptible performance factors from the user's point of view. The segment loading pattern of a program can be profiled during development. However, the profiling data used in development may not match that of individual users. Chapter 8 addresses this problem, and provides a solution to improve the load time for an executable program. This solution is based on dynamic profiling of users workload. The translator uses the collected information to optimize the load time by modifying the segment attributes in the executable file.

Finally, Chapter 9 draws some conclusions about the work, presents the contribution of the thesis, and outlines a few research directions in the future from different aspects.

### Chapter 2

# **Previous Work**

Microprocessor technology has evolved quickly in recent years due to the improvement of VLSI technology. As a result, hardware systems have become out of date in just a few years. The lifetime of software, on the other hand, often outlives the system for which it was developed. To ensure that existing software can be run on a new machine, hardware manufacturers need to provide backward compatibility. Currently, compatibility is preserved by fixing the ISA. Preserving compatibility through the ISA, however, limits the performance improvement that the new hardware can have for old programs. Software compiled for one generation of hardware may not be able to take advantage of features present in the next generation.

This chapter surveys some of the related work on binary translation. Section 2.1 surveys the related work in industry and Section 2.2 surveys the related work in academia.

### 2.1 Related Work in Industry

Digital Equipment Corporation used binary translation to allow VAX code and MIPS code to be run on an Alpha AXP machine [27]. They created two translators: VEST, which translates OpenVMS binary images to OpenVMS AXP images, and mx, which translates ULTRIX MIPS images to DEC OSF/1 AXP images. They also ported the Open VMS operating system from

the VAX architecture to the Alpha AXP architecture [13]. The migration tool contains two components: a binary translator and a run-time environment. The VEST translator performs backward symbolic execution [28] of VAX instructions to resolve as many computed branch targets as possible. A run-time lookup is used when more than one possible computed target exists. The run-time environment supports completely automatic translation by including a fallback interpreter of old code, and extensive run-time feedback to avoid using the interpreter except for dynamically created code. When the binary translator encounters a branch with a non-determinable target, it generates code to call lookup routines. The lookup routine maps an instruction address in the old architecture to a new address. If an address mapping exists, the control switches to the translated code for execution. Otherwise, the interpreter will be invoked to execute the destination code. The interpretation continues until a control flow change. There is no detailed report about run-time overhead in [27].

Recently, Digital Equipment Corporation introduced a product, FX!32 [8] [30], which incorporated partial translation. FX!32 combines both interpretation and binary translation techniques to translate x86 Win32 applications on Windows NT Alpha. FX!32 consists of three interoperating components: a run-time environment (runtime), a binary translator, and a server. The runtime contains an emulator that implements the entire x86 user-mode instruction set and the complete x86 Win32 environment. When the user runs an application program, Windows NT invokes the runtime. When the application is first executed, the runtime will emulate it. When the application is unloaded, the server looks for a new or enlarged profile. A new profile means that a previously unseen x86 image has been executed and may require optimization. An enlarged profile indicates that the runtime found more new code in the pre-

vious execution. In either case, the server invokes the background optimizer to translate the x86 code into Alpha code.

The binary translator implemented in this thesis differs from FX!32 in several aspects. First, FX!32 implemented the translation by modifying the NT loader. The binary translator in this thesis, on the contrary, implemented the translation on top of Windows. This difference affects almost all the implementations of the translation. Second, FX!32 redirects X86-based NT API calls to corresponding Alpha-based NT calls. Alpha derives most of the performance gain from the native compiled NT API source which is intensively used in Windows application programs. This thesis assumes no existing source code.

IBM proposed an experimental binary translator in order to port binary programs from their S/390 architecture to a Very Long Instruction Word (VLIW) architecture [26]. The architectural framework consists of the migrant engine, the native engine, and the switching monitor. A translator takes the base object code and produces the native object code to run on the native engine. The switch table is used during fallback from the native code to the base code or vice versa. This table maps groups of base instructions to groups of native instructions.

The execution of application is started by setting the migrant engine's program counter (mPC) to the entry address into base code. The switching monitor continually checks the mPC, looking for a match with one of the base code address entries in the switching table. If a match occurs, the corresponding native code address is loaded into the native program counter, or shadow program counter (sPC). The control is then switched to the native code for execution. The execution continues until the end of the translated code is reached. This may be a branch whose target cannot be determined at translation time. If there is no corresponding native code entry point for this target, the mPC is set to point at the base instruction which

is the logical successor to the last instruction in the previously executed base code. [26] also proposed a hardware support for detecting self-modifying code.

DAISY [9] described some hardware features for a VLIW machine. It intended to emulate existing architectures, so that existing software, including the operating system, runs without changes on the VLIW machine. DAISY partitioned the memory into 3 sections. The low portion is mapped to the physical address space of the old (base) architecture. The middle portion consists of read-only virtual machine monitor software. The top section stores the translated code. Each address in the low portion is mapped to an address in the top portion. The code translation unit is a page. Several VLIW primitive branch instructions were also defined. The VLIW primitive for branches with a non-determinable target can be implemented either by hardware or by software. The software approach is similar to [15].

Tandem used binary translation for migrating software from the TNS (Tandem NonStop Series) CISC-based computer family onto the TNS/R (Tandem NonStop Series/RISC) computer family based on the MIPS RISC architecture [1]. The approach to resolving various puzzles about the unpredictable dynamic effects of the original CISC code is to make a best guess based on static analysis. If the guess turns out to be incorrect, the processor falls into interpretive execution mode for a short time This approach requires the presence of a CISC interpreter and all of the original CISC code for potential use by the interpreter. Tandem defined the points for entry to and recovery from interpreter mode. There is no clear description about how the switching between the translated RISC code and the original CISC code was implemented.

Motorola used PowerPC Migration Tools to enable a smooth transition of existing applications (guest) to the PowerPC architecture (target) [2]. Migration tools consist of 4 components: A Front-End (parser) that parses the object code or assembly code, a Back-End (code generator)

that generates the target code, an Interpretive, which is a macro that interprets the instruction's semantics, and finally, the Runtime support, which provides the target machine with an execution environment for the guest code. There were four different configurations for the Migration tools. In the Emulator configuration, a binary parser decodes one instruction at a time and invokes a handler that uses "C" code to compute the semantics of the guest instruction. In the Translator configuration, an assembly parser reads in assembly (source) code and invokes a handler that constructs the intermediate data structures. These data structures are input to the subsequent code optimizations and generation. It takes one pass through the whole source code. In the Translating Interpreter configuration, the interpreted instruction can be directly generated from the translating interpreter without needing to interpret the same instruction when it is visited again. The Binary Translator configuration is similar to the Translator except that its input is the binary code. The paper did not give a detailed discussion of this configuration.

Sun Microsystems introduced Wabi to run Microsoft Windows applications on the Solaris desktop [29]. Three core Windows dynamic link libraries: USER.DLL, KERNEL.DLL, and GDI.DLL have their equivalent in Solaris. Without the need to emulate most of the operating system code, much of the performance loss can be avoided. Other Windows executables can have three options for translation. If the architectural platform is x86, the executable will pass through to the hardware without needing to emulate the instructions. If the platform is not x86, Wabi either interprets op-code by op-code or translates a block of instructions at a time. For the latter case, the translated instructions are stored in the translator cache. Loops in application code are translated once and executed multiple times.

#### 2.2 Related Work in Academia

Larus and Ball [15] described the analysis of rewriting executable files for their profiling and tracing tool, qpt. In order to solve the non-determinable target problem, qpt uses a program's original code segment as a translation table to map from an address in the original program to addresses in the new program. A few instructions are inserted before a branch with an unknown target. These instructions compare the target of the branch at run-time. If the target turns out to be within the old code, the code dereferences the translation table to find the new target for the branch. In this thesis, the approach to resolving a non-determinable branch target is similar to that of qpt.

Wahbe et al [31] presented adaptable binaries for implementing robust binary transformation. They demonstrated that the information necessary to support adaptable binaries can be compactly recorded. However, they assumed that this necessary information was propagated from the compiler. This thesis makes no assumption on any rules or compilers used for generating the original executables.

Wahbe et al [31] also indicated several difficult problems in binary transformation. Among other things, there is one issue which is of particular interest to this thesis. [31] mentioned that there is no robust method for distinguishing code from data in the presence of indirect control transfers. Therefore, one solution to this problem, as implemented in Pixie [7], is to duplicate the code segment and instrument only the duplicated code. This thesis uses a different approach to solving this problem. For example, not all kinds of the hashing jump targets are difficult to resolve. Chapter 5 will give a more detailed discussion on this problem.

The Morph Project [4] was proposed to enable the evolution of executables by repartitioning the compilation process and by re-writing the executable. Morph consists of four software components. The Morph back-end generates executable programs with annotations that can be used by the editor to retarget the code. The Morph editor performs host-specific optimizations for the specific hardware platform. PostMorph analyzes existing executables and creates application-specific optimization templates for retargeting. The Morph continuous monitoring system generates profile data.

PostMorph uses conservative methods, such as single-step debugging or simulation, to trace the control flow and data reference activity. The output of this process is classified as safe, unsafe, and rarely used. Code marked as rarely used will not be optimized. Unsafe code may require manual transformation. Morph did not examine the issue on transforming unsafe code.

Etch [3] was proposed to evaluate and optimize the x86 application program. Etch is invoked with an executable and a Dynamic Link Library (DLL). The DLL includes a set of routines which are called for instructions in the executable. After scanning and instrumenting the executable, Etch writes a new executable that can be run. The new executable includes all referenced functions in the callback routines as well as the Etch runtime library. The instrumentation routines run as a side effect of running the new program. Lee et al [3] did not discuss the instruction address relocation problem that arises due to editing binaries.

### Chapter 3

# Background

### 3.1 Binary Translation Model

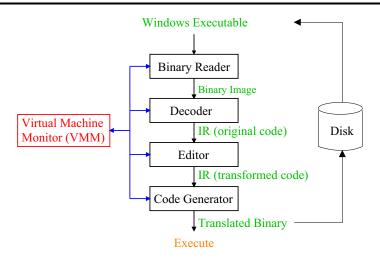

The framework proposed in this thesis is designed to handle x86 code. The original executable is a 16-bit Windows application program. The translated executable will contain instrumentation code or will be optimized code. Figure 3.1 illustrates the overall system.

The framework contains a front-end for reading in a binary program and decoding CISC instructions. This thesis will introduce the translator front-end in Chapter 4. It also contains an execution editor which performs insertion of instrumentation code or optimization. Editing binary program issues will be discussed in Chapter 5. The translator also includes a code generator that dynamically generates new binary code. After the new code is generated, the translator may run it and measure the performance via either hardware execution or simulation.

More specifically, this thesis addresses the issues involved in implementing a solid translation framework. Issues addressed include reading binaries, decoding, solving address relocation problems, enabling partial translation, supporting a run-time switching mechanism, and measuring the overhead of translation. At the final stage of translation, the translated code will be written to disk for reuse.

Figure 3.1 The binary translation framework.

### 3.2 Executable File Header

This section describes the 16-bit Windows executable file format. Since much of the work in the thesis was implemented based on the information given in the executable file, it is better to introduce the executable file format in this section.

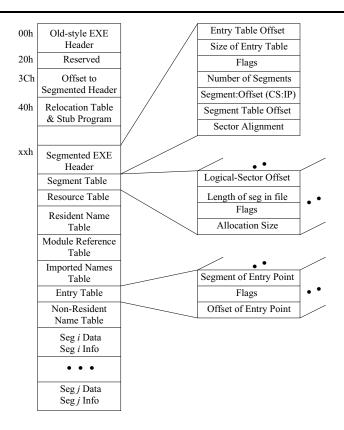

The 16-bit Windows executable file is also called *New Executable*, or *NE*, as distinguished from old DOS executables. Instead of giving a comprehensive NE file description, this section only introduces those portions which are pertinent to the thesis. For a complete description, the reader may refer to [18]. Figure 3.2 illustrates the NE file format [18], with some modifications.

The NE file contains a header, followed by a few tables, then followed by each segment data information. Section 3.2.1 will introduce the NE header. Tables that will be used during translation will be introduced in Section 3.2.2. Segment data information will be discussed in Section 3.2.3.

Figure 3.2 The NE file format.

#### 3.2.1 The NE Header

The first two bytes in the NE header are the NE signature. The translator uses this signature to determine whether it is a valid application for translation. In the header there are also offsets to several tables such as the Entry Table, Segment Table, and Resource Table. The header also contains the number of entries in these tables. By using these offsets, the translator can easily move the file pointer to locate the tables for accessing information. The number of entries in the table usually helps the translator determine the boundary when accessing information from within the table. The NE header also contains the address of the first instruction to be executed. This address has the form of segment:off set pair. Since the segment address cannot be known until the NE file is loaded into memory, the value in segment portion has the form of a logical ID.

At offset  $32_{\text{hex}}$  to the NE header there are two bytes defining the logical sector alignment shift count. This word indicates the alignment size for the NE file. It will be used when the translator performs post translation discussed in Chapter 7. The default value for this count is 9. The offsets  $37_{\text{hex}}$  through  $3F_{\text{hex}}$  are reserved with current value 0's. The translator may utilize this space to store some valuable translation information. For example, the space may be used to store the file pointer to a new added area in the NE file, such as whether a segment was translated or not. Chapter 7 will discuss more details on these issues.

#### 3.2.2 Tables in the NE File

One of the tables most frequently used by the translator is the *Segment Table*. The translator may use the segment table when a segment is loaded into memory for execution. It may also need to use the segment table when it writes the translated code to secondary storage. This

| Value   | Туре      | Description                           |

|---------|-----------|---------------------------------------|

|         |           |                                       |

| 0007h = | TYPE_MASK | Segment-type field                    |

| 0000h = | CODE      | Code-segment type                     |

| 0001h = | DATA      | Data-segment type                     |

| 0010h = | MOVEABLE  | Segment is not fixed                  |

| 0040h = | PRELOAD   | Segment will be preloaded             |

| 0100h = | RELOCINFO | Set if segment has relocation records |

| F000h = | DISCARD   | Discard priority                      |

Figure 3.3 The segment flag word in the NE file.

entry. The first word defines the logical-sector offset to the per-segment data, relative to the beginning of the file. To locate the per-segment data, this number is left shifted by the value of logical sector alignment shift count described in Section 3.2.1. The second word defines the length of the segment in the file. The third word defines the flags for the segment. As the flags defined in the third word are used in almost all the remaining chapters, this section gives a full description for these flags. The fourth word in the segment entry defines the minimal allocation size for the segment. In most code segments, this value will be identical to the segment length.

Figure 3.3 defines all the possible attributes for each segment [18]. Each segment in the NE file can be either CODE or DATA, but not both. The PRELOAD attribute indicates whether or not the loader should load the segment before the program begins execution. The MOVEABLE attribute indicates whether or not the operating system can move it in linear address space. The DISCARD attribute indicates whether or not Windows may discard it from memory if there is not enough space. If there are several target locations referenced by the segment, and these locations cannot be determined before run-time, then this segment will

contain the relocation information for these targets. The *RELOCINFO* attribute indicates whether or not the segment contains any relocation information.

The Resource Table contains the entries for each resource used in the executable file. In Windows, a resource can be an icon, cursor, mouse, or others. Although the translator only translates code, getting information about the resource table can be crucial as far as post translation and program reuse is concerned. Modifying the original executable file implies that the offset of resource in the file may be changed as well. By carefully adjusting the offsets, the translated executable file can be executed without error. Chapter 7 will discuss the modification of the Resource Table after translation.

The Entry Table contains bundles of entry-point definitions. When a function in the segment is to be exported, there must be an entry in the entry table. Because Windows is a dynamic linking environment, the callers of this exported function cannot know the final address of this function until the segment is loaded and the address is resolved by the loader. The information in this table will be used both during translation and after translation.

### 3.2.3 Per-Segment Data Information

The contents of each segment can be indexed by a combination of both the logical sector from the entry of the segment table and an alignment shift count from the header. If the segment has relocation fixups, as indicated in the segment table entry flags words, these fixup records immediately follow the content. The addresses of exported functions in an application program cannot be known before the program is loaded. Therefore, the program may call some functions whose addresses may not be immediately available. One example is that most Windows application programs may call Windows Application Program Interface (API) functions.

The target addresses for these API functions will be fixed when the application is loaded into memory.

If the operand of an instruction references a target that cannot be resolved before loading, then there is an entry containing the address of this operand. The translator does not need to know the values for these fixup records. However, it may need to know the address of each operand which needs a fixup record. If the translator modifies the content of the original segment and if such modification results in changes of the offsets of some instructions, then it needs to adjust the location for these operands, so that an operand of translated code can be correctly fixed when it is loaded into memory again. These issues are discussed in more detail in Chapter 5 and Chapter 7.

### 3.3 Dynamic Linking

One feature of the Windows operating system is that all executable programs, including applications and the operating system itself, are dynamically linked before execution. As opposed to static linking in which the linker links together all the object code referenced into an executable at compile time, dynamic linking is a method in which the program loader links the modules at run-time.

To illustrate the merit of dynamic linking, let us look at an example that compares the dynamic linking with static linking. In Figure 3.4, the application program contains a library function call, printf(). In static linking, the linker inserts the object code of printf() into the object code of the program foo.c before it generates the executable file. For example, assuming there are 100 user programs executing simultaneously with each one calling printf(), then there are 100 instances of printf() loaded into main memory. With dynamic linking, on the other

```

#include <stdio.h>

int main(void) {

/* do something, and then call system library function */

printf("Hello world\n");

}

```

Figure 3.4 A source program written in C.

hand, only one instance of printf() needs to be loaded into main memory. As a result, dynamic linking utilizes memory better than static linking.

The translator implemented in this thesis performs dynamic translation for the binary program, which means that the translation of a code segment begins after the loader loads this segment. As such, most targets that cannot be determined statically have been resolved by the loader during dynamic linking. However, even after loading, not all of the targets can be found until the program actually runs. Chapter 5 will address this problem.

For a more detailed introduction to dynamic linking and dynamic link library, the reader may refer to [16] [17].

### Chapter 4

# Binary Front-End

The frond-end of the binary translator consists of reading in binary code and decoding it to an intermediate representation. This chapter discusses these issues in Section 4.1 and Section 4.2 respectively. Verifying the decoding process is also important to the preliminary stage of translation. This chapter addresses this problem in Section 4.3. The execution of translated code will be discussed in Section 4.4.

### 4.1 Parsing Binaries

Parsing the executable program can be done statically or dynamically. There are a few differences between these two approaches. For each executable file, there is a complete file header describing all information about the program. When the executable program is loaded into main memory for execution, some information will be discarded. One example is that the relocation fixup record associated with the segment is discarded after the loader loads the program into main memory. On the other hand, the instruction in an executable program stored in the secondary storage may contain unsolved external addresses. This is because in Windows all the libraries are dynamically loaded.

This thesis focuses on reading binaries from main memory. Translating the code when it is loaded into memory provides us with more accurate information. For example, most unknown far targets will be available before the translator starts to translate the instruction. Moreover, since not all of the code segments will be executed, performing dynamic translation guarantees that only code that is being translated will be executed. Put another way, dynamic translation supports on-demand translation.

In Windows, each segment in the executable program can be dynamically loaded into main memory. To intercept the dynamically loaded segment, the translator installs a notification callback function before the application program starts execution. A callback function is a function that will be called by Windows. Among other notifications, the translator is particularly concerned with the following messages sent by Windows:

- (1) When Windows loads a segment into memory

- (2) When Windows frees a segment from memory

- (3) When Windows is about to start a task, and

- (4) When Windows is about to exit a task.

The translator maintains an internal data structure for keeping track of each in-memory segment. Figure 4.1 illustrates the data structure implemented in the translator. Upon receiving message (1) from Windows, a NFY\_LOADSEG data structure will be passed to the translator. This structure includes six attributes: Size, Selector, SegNum, Type, Instance, and ModuleName. These attributes represent the size allocated for the segment, the selector to the segment when the segment is loaded into memory, the segment's logical segment ID in the NE file, the segment type, the number of instances that share this segment, and the name

of its owner. The selector of the segment will be defined in Section 6.1. The size, the logical ID, and the type of segment were previously described in Section 3.2. Most importantly, the data structure includes the selector's value to the segment. The selector value uniquely identifies the segment in memory. This value plays a central role in the switching mechanism. The DWORD in Figure 4.1 stands for double word which is a 4-byte unsigned integer. When the translator receives message (1) from Windows, it first checks whether the segment is code or data. If it is a code segment, it needs to check whether the segment has been translated or not. It is likely that a code segment was loaded into memory by the loader, translated by the translator, unloaded from memory by the loader, then loaded again by the loader. In this case, the translator can avoid retranslation by simply checking the Translated bit for the segment. The Present bit in Figure 4.1 indicates whether or not the translated code for the original code segment is in memory. The NewSelector in Figure 4.1 is the selector to the translated code, provided that the code is in memory.

When the translator receives message (2) from Windows, it updates the segment data structure. The *Present* bit will be cleared. Any reference to a segment whose *Present* bit is cleared will be considered as an invalid access.

When the user starts an application program, Windows first loads all of the PRELOAD segments into memory for the program, then starts execution. After loading all PRELOAD segments and before the execution is about to start, Windows will send message (3) to the translator. Upon receiving this message, the translator obtains the program's initial program counter with a selector: offset pair, or CS:IP. After translation, the translator will redirect the execution flow from this CS:IP value to its new counterpart. The translator needs the new

```

typedef struct SegNodeTypeTag {

/* NFY_LOADSEG data structure */

DWORD

Size;

WORD

Selector;

WORD

SegNum;

WORD

Type;

WORD

Instance;

LPCSTR

ModuleName;

/* New code segment information */

BYTE

Translated;

/* Translation bit of the segment */

BYTE

Present;

/* Presence bit of the segment

*/

WORD

/* Pointer to the new code seg

NewSelector;

*/

/* Info for control flow analysis */

OPER_TYPE *head_op, *tail_op;

DWORD

index;

MEM_TYPE code_map[FLOW_MEM_CHUNK_MAP_SIZE];

MEM_TYPE fallthru_stack[MAX_STACK_SIZE+1];

DWORD

top_fallthru_stack;

struct

SegNodeTypeTag

*nextSeg;

} SegNodeType;

```

Figure 4.1 Internal data structure for in-memory segments.

CS:IP not only to start executing the new code, but also to generate the new executable file when the translation is completed. Chapter 7 will discuss this point.

When the running program is about to exit, the translator will receive message (4) from Windows. After receiving this message, the translator can perform post translation task such as writing the translated code to the secondary storage.

### 4.2 Decoding CISC Instructions

### 4.2.1 The Decoding Process

After intercepting binary code from memory, the next step is to decode it into an *Intermediate Representation (IR)*. Decoding is basically a table lookup process in that the translator uses the hexadecimal value to determine the operation code. Since the length of an x86 instruction is variable, the translator may need to decode additional binaries such as addressing mode in order to determine the instruction length.

There are several options in decoding the intercepted binaries. First, the translator can decode one instruction at a time, translate it into new operations, and execute these operations. This is actually an interpretation approach. Interpretation has one advantage in that the translator will never translate data into code. However, in general interpretation is very slow [8] [10].

The second option is to decode the whole intercepted code segment, perhaps one function at a time. Decoding the whole segment provides us more opportunities for optimizing the new code. However, it is likely that the translator may decode data or patched bytes into instructions. There are two approaches to solving this problem. First, the translator may interpret the instruction the first time it parses the original code, or whenever the untranslated code is

found. Second, the translator may perform a quick control-flow analysis over the code segment before decoding it. For example, unless an address is the target of some branch instructions, the address that immediately follows a non-conditional branch will not be decoded. In this thesis, the decoding process is guided by control-flow analysis which will be discussed in Section 4.2.2.

#### 4.2.2 Control-Flow Analysis

Given a dynamically-loaded code segment and a starting instruction pointer, the controlflow analyzer starts decoding instructions without actually running them. If the instruction

being decoded is not a branch, then the analyzer only needs to advance the program counter to

the next instruction, provided that the program counter does not exceed the length of segment.

The starting instruction pointer can be either the initial IP, or any entry point in the segment.

Section 4.4 will discuss how the translator gets the instruction pointer before the control-flow

analyzer is invoked. In order to find as many instructions as possible, the control-flow analyzer

may need to iterate several times until all the entry points that belong to this segment are

visited.

During analysis, the translator maintains some information in its internal segment data structure. Control-flow information is included in the data structure illustrated in Figure 4.1. The variables headOp and tailOp in Figure 4.1 are used to maintain a list of operations in the segment. The attribute index keeps track of the total contiguous instruction areas visited for the segment. The attribute  $code\_map$  defines the lower and upper boundaries for the each contiguous instruction area. Both the attributes  $fallthru\_stack$  and  $top\_fallthru\_stack$  are used when the decoded instruction is a conditional branch or a function call. If the translator encounters a conditional branch or a function call, it will first save the fallthrough target to a

stack, and visit the taken target of conditional branch. If the translator cannot decode further, it then pops the fallthrough target and keeps decoding, until the fallthrough stack is empty. As soon as any adjacent instruction areas are found, the translator merges them to form a larger single area.

The control-flow analysis module built in the thesis is a conservative approach in that all the code area it detects must be instructions. While a conservative approach is needed to guarantee correct translation, sometimes the results may be weak. To remedy this problem, the translator must be able to support incremental translation which will be discussed in more detail in Section 5.3.

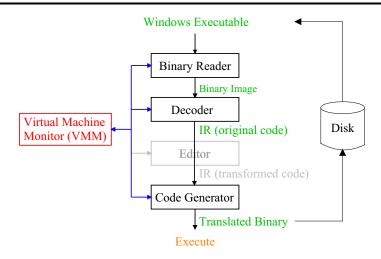

## 4.3 Verifying the Decoding Process

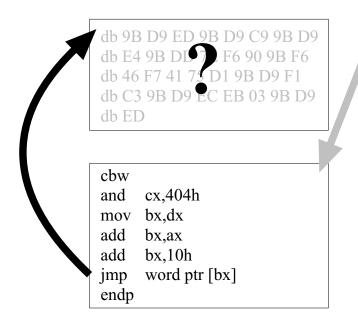

After the decoding process, the translator may need to verify the output code before it can be used for further transformation. The verification of the decoding process is difficult in general, due to the irreversibility of compilation. One might use a commercial disassembler, such as Sourcer [6], to help verify the decoding process. The translator may generate assembly code from the IR, and compare the result with the assembly code generated by Sourcer. However, this is not a reliable way to do verification. The assembly code generated by Sourcer may not be accurate. In our approach to debugging the decoding process, the translator also contains a binary code generator which translates the IR back to binaries for execution. This step bypasses the editing process, thus helping to distinguish the bugs between the decoding process and the editing process. The dashed arrow in Figure 4.2 illustrates the verification process.

The binary code generator is similar to an assembler. The main difference is that the input to the generator is not assembly code, but the IR. One could use a commercial assembler to

Figure 4.2 Verifying the decoding process.

generate the new binary code. However, there are two major concerns with this method. First, the input to the assembler must be assembly code. Sticking to a specific assembly representation usually is not a good idea for later optimization. Second, the binary code is generated from the IR after the executable program was loaded into memory for execution. Relying on an assembler usually takes more time to produce new code and sometimes the generated code must be modified to conform to the specific assembler syntax. For these reasons, this system bypasses using an assembler to generate binary code.

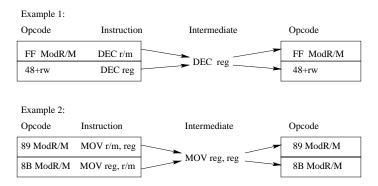

Since some operations share the same pattern of addressing modes, the code generator uses several templates to generate binary code. For example, Figure 4.3 shows that there are 8 x86 operation codes that share the same pattern of 4 addressing modes. The code generator may group them together and use a template to generate the binary code.

In addition to fully generating the x86 code from the IR, a slim version of a code generator was also implemented to accelerate the develop time. In this version, the original binary code is copied to the new code directly from the IR, provided that the instruction has not been

```

Operations:

Description:

ADC

Add with Carry

ADD

Add

AND

Logical AND

CMP

Compare Two Operands

0R

Logical Inclusive OR

SBB

Integer Subtraction with Borrow

SUB

Integer Subtraction

XOR

Logical Exclusive OR

Addressing Modes:

Destination

Source

{AL,AX,EAX},

{imm8,imm16,imm32}

\{r/m8, r/m16, r/m32\},\

{imm8,imm16,imm32}

\{r/m8, r/m16, r/m32\},\

{r8r16,r32}

{r8,r16,r32},

\{r/m8, r/m16, r/m32\}

imm:

immediate value

r/m:

either register or memory operand

register

r:

8/16/32: size of operand, in byte

```

Figure 4.3 Operations that share the same addressing mode.

Figure 4.4 Ambiguous situations in generating new binary code.

changed. For each IR, the hexadecimal code is also stored as soon as the instruction length is determined during decoding. The hexadecimal code is copied to the new code during code generation.

Since it is likely to have more than one binary code corresponding to an x86 assembly instruction, generating new code from decoded binaries may result in ambiguity. Consider Figure 4.4 for examples. In Example 1, there can be two binary codes for the decrement register instruction. The first encoding contains two bytes: FF and a ModR/M byte which determines whether the operand is memory or register. The second encoding contains only one byte since the register value is encoded as part of the operation code. Special care must be taken during code generation, since different sizes of instructions may affect the relative addresses of other instructions. This is particularly true after performing optimizations on the new code. In each IR, instruction length as well as hexadecimal code are stored. Either information can be used to determine the encoding. In Example 2, the assembly instruction moves the value of one register to the other register. This assembly may have two different binary codes that perform the identical operation. This case, however, does not affect the result since the length of these two encodings are identical.

```

i = logical segment ID;

allocate a memory space, Mem[i];

translate Seg[i] into Mem[i];

make Mem[i] executable;

obtain the selector, Sel[i], for Mem[i];

Ofs[i] = new IP;

replace the initial CS:IP with Sel[i]:Ofs[i];

return control to operating system;

```

Figure 4.5 An algorithm for translating and executing the new segment.

Another way to verify the decoding process is for the binary code generator to generate a binary image to secondary storage, and compare the output file with the one generated by commercial product. For example, the TDUMP command associated with  $Turbo\ Debugger$  can be used to dump the specific binary image of an executable program. This can then be compared with the output generated by the binary code generator.

### 4.4 Executing the Translated Code

After the intercepted code is translated, the next step is to execute the new code. At the beginning, this code will start execution from its new initial program counter. Figure 4.5 shows the algorithm for redirecting execution to the new initial program counter.

The logical segment ID in Figure 4.5 can be obtained from the internal segment data structure described in Figure 4.1. First, the translator requests a memory space from the operating system for storing the new code, then starts translation. Since allocated memory cannot be executed, the translator needs to change the access right for allocated memory before it can be executed. At the last stage, the translator replaces the original CS:IP value with its new counterpart and returns control back to the operating system. The new initial code segment

```

for each loaded segment {

find all entry points which belong to this segment;

for ( j=1; j<=Entry_Found; j++ ) {

backup the byte content MEM[OFFSET(j)]

mask the byte content MEM[OFFSET(j)] with a breakpoint;

}

}</pre>

```

Figure 4.6 An algorithm for trapping each loaded segment.

address, or Sel[i], is available as soon as the translator makes the memory executable. The new initial offset, or Ofs[i], is fully under the control of the translator. When the new code was modified, Ofs[i] may or may not be the same as IP. The translator is responsible for keeping track of such change.

In addition to redirecting execution to the new initial program counter, the translator also needs to set up some extra traps when each code segment is loaded into memory in order to capture more instructions later. Figure 4.6 shows the algorithm used by the translator during segment loading.

The entry points in Figure 4.6 can be found in the module table of an application program. For each loaded code segment, the translator will replace the byte content at all entry points with breakpoints if the segment contains any of them. The OFFSET(j) in Figure 4.6 stands for the offset of an entry point, j, to the beginning of the segment. MEM[OFFSET(j)] stands for the byte content in address OFFSET(j). As mentioned previously, the translator can obtain the program's initial program counter from Windows. Starting from this initial program counter, the translator can decode and analyze the binaries. If any instruction in the initial segment branches to another segment, the translator must detect such a branch, or this target

```

foo.c

foo() {

func_1();

func_2();

}

```

```

bar.c

func_1() {

}

func_2() {

}

```

Figure 4.7 Switching mechanism: a code example.

segment could never get a chance to be translated. As such, the translator sets up breakpoints at all entry points in the segment as traps. Whenever the target in the segment is trapped, the translator may then translate the segment.

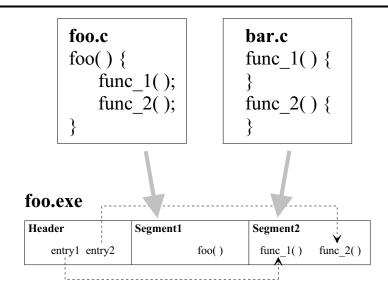

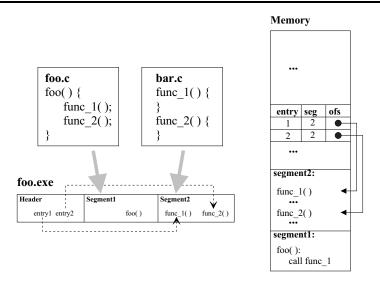

Let us consider the code example in Figure 4.7 to demonstrate how the switching mechanism works. The source program contains two files, foo.c and bar.c. Foo.c contains calls to functions defined in bar.c. If the program was compiled by using a large memory model, the compiler will generate far calls for the calling instructions in foo.c. Figure 4.8 shows the executable file for the source program. In Figure 4.8, the function foo() was stored in segment 1, the functions  $func_1()$  and  $func_2()$  were stored in segment 2. Since the address of segment 2 was not available at compile-time, the compiler generated 2 entry points in the executable header, one for  $func_1()$  and the other for  $func_2()$ .

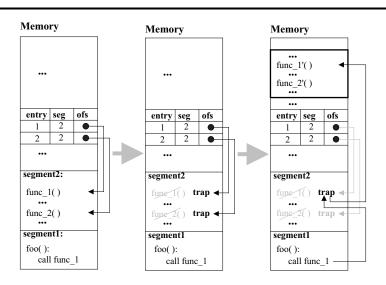

Figure 4.9 shows the code image after the executable file is loaded into memory. After segment 2 is loaded, its address is available. Now the loader fills this address in the target of calling instructions in segment 1. Figure 4.10 shows the graphical description of how the translator detects that  $func_1()$  in segment 2 is executed. The left column in Figure 4.10 shows the in-memory code image. The middle column shows the in-memory code image after the translator sets up the traps. The right column shows the execution flow. After the trap is

Figure 4.8 Switching mechanism: the executable file.

received, the translator starts translating segment 2 and redirects the execution flow to the new code. The black arrows in the right column indicate that the call to  $func_1()$  branches to a trap, then the translator redirects the branch to  $func_1()$ .

Figure 4.9 Switching mechanism: the code in memory.

Figure 4.10 Switching mechanism: trapping and redirecting execution flow.

# Chapter 5

# **Editing Binaries**

Instrumenting code or performing optimization requires editing the code and may result in code size changes. This chapter discusses the instruction relocation problem resulting from this change of code size. Section 5.1 discusses adjusting the branch target whose value can be determined at translation time. A method is proposed in Section 5.2 to solve the relocation problem in situations where the branch target cannot be determined at translation time. Since the translator needs run-time support to resolve the branch target, in this case the impact to performance is also analyzed in this section. Because of the fact that the translator may not be able to detect all possible instructions during initial translation, it may be able to find more instructions as soon as the undetermined targets discussed in Section 5.2 are resolved at run-time. Section 5.3 discusses the issue of enabling incremental translation.

# 5.1 Relocation for Determinable Targets

If the target of a branch can be determined during translation, then the translator is able to solve all the relocation problems resulting from editing. A branch instruction with a statically identifiable target can be either intra-segment or inter-segment. The solution to intra-segment instruction relocation differs from that of inter-segment. These problems will be discussed in

Section 5.1.1 and 5.1.2, respectively. The callback function and the regular hashing jump are also determinable. Section 5.1.3 discusses the problem of editing a code segment that contains callback functions, and hashing jumps with regular patterns will be discussed in Section 5.1.4 Some DLL function calls are compiled as indirect calls. Indirect DLL function calls can be statically determined and will be discussed in Section 5.1.5.

#### 5.1.1 Intra-Segment Targets

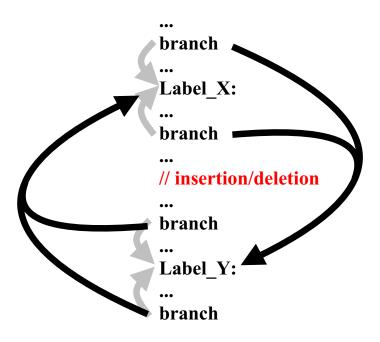

Figure 5.1 shows how to adjust a branch target after insertion or deletion. All the targets of branches in Figure 5.1 are PC-relative. Though there are intra-segment branches whose targets are not PC-relative, this solution still applies. All of the intra-segment targets are relative to the beginning of segment if they are not PC-relative. For those grey-arrow branches indicated in the figure, the translator does not need to adjust the target. For example, assume the user inserted a few bytes at location  $3000_{\rm hex}$ , the locations for those instructions after  $3000_{\rm hex}$  will be changed accordingly, but not for the instructions whose locations are prior to  $3000_{\rm hex}$ . Now if there is a branch from location  $1000_{\rm hex}$  to location  $2000_{\rm hex}$ , or vice versa, then no adjustment needs to be made. Likewise, if there is a branch from location  $4000_{\rm hex}$  to  $5000_{\rm hex}$ , or vice versa, no adjustment needs to be made either. Assume the user inserted  $100_{\rm hex}$  bytes at location  $3000_{\rm hex}$ , the location of  $4000_{\rm hex}$  and  $5000_{\rm hex}$  will become  $4100_{\rm hex}$  and  $5100_{\rm hex}$ , respectively. The net difference does not vary.

If the source and destination of the branch straddle the insertion or deletion line, however, adjustment may need to be made. These situations are indicated by the black-arrow branches in Figure 5.1. Assume the user inserted  $100_{\rm hex}$  bytes starting from location  $3000_{\rm hex}$  and there is a branch from  $2000_{\rm hex}$  to  $4000_{\rm hex}$ . Also assume the branch is PC-relative and the branch

Figure 5.1 Adjusting the branch target.

instruction takes 4 bytes. If the insertion was not made, the value of operand in the branch instruction would be  $1FFC_{hex}$  ( $4000_{hex}$  -  $2004_{hex}$ ). Now if the user inserts  $100_{hex}$  bytes in between these locations, the value of operand should be added by  $100_{hex}$  as well, that is,  $20FC_{hex}$ .

#### 5.1.2 Inter-Segment Targets

Adjusting determinable inter-segment branch targets is slightly more complicated than intra-segment, but not difficult. When a code segment is loaded into memory, the loader needs to fix up all the branch targets in other segments if these targets reference the current code segment. Likewise, changing the location of instructions in the current code segment may require the translator to adjust these targets accordingly.

Figure 5.2 Adjusting the inter-segment branch target.

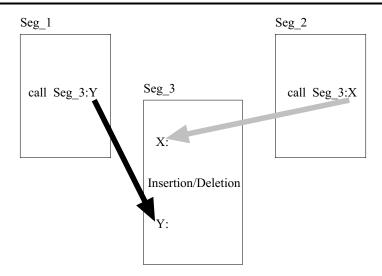

Figure 5.2 shows two cases for the inter-segment targets. The black arrow in Figure 5.2 indicates that the operand value in the calling instruction must be modified. The insertion or deletion in  $Seg\_3$  results in the change of offset Y. This change, in turn, affects the operand (target Y) of the calling instruction in  $Seg\_1$ . On the other hand, the insertion or deletion in  $Seg\_3$  does not affect the offset X. As such, no adjustment needs to be made for the calling instruction in  $Seg\_2$ .

After editing a code segment, the translator needs to iterate through all other present code segments. During iteration, the translator looks up all the relocation fixup record to find if the segment of the fixup records matches the current code segment. A detailed description of relocation fixup records may be found in Section 3.2.3. If the segment that belongs to the fixup record matches the editing segment, and the offset of fixup record is larger than an insertion or deletion point, then the translator will replace the operand with a new value. This value can be calculated during editing.

#### 5.1.3 Callback Functions

Some functions in application programs can be declared as call-back. The description of a callback function may be found in Section 4.1. The address of a callback function may also be determinable. If a code segment contains any callback function and this segment is translated, then its original segment must reside in memory as well. Section 4.4 mentioned that when a code segment is loaded into memory, the translator sets up a trap for each entry point in the original segment. When the user sends a command, for example, by pushing a window button, the operating system sends a message to the application program in response to user's action, which means that the operating system calls back the function in the application program. Assume there is an operating system instruction I which calls back the function in the application program. After the application program is loaded into memory, the loader has filled the operand of I with the address of the callback function. This address is an old address. Even if the translator translated the callback function and created a new address for the callback function, the instruction I will still reference the old address unless the translator can also modify the operand of I.

Therefore, the translator relies on the trap in the original segment to redirect the execution. As soon as the trap is received, the translator looks up the address mapping table which will be defined in Section 5.2.2, and switches the control to the new code.

As opposed to directly overwriting the offset as previous approaches did, the new address of the callback function was not overwritten by the translator at run-time. After the translation is finished, this information will then be written to disk when the translator creates a new executable file. Writing the new code to secondary storage will be discussed in Chapter 7. For now, it suffices to say that the old code segment is not required to be present when the translated program is run again. All the corresponding entry addresses in the code segment will be updated when the translator generates the new executable file. When the program is loaded again, the address of the callback function will have already become the new one.

#### 5.1.4 Hashing Jumps with Regular Patterns

A hashing jump is another branch whose targets may be determinable. The compiler usually generates a hashing jump based on a regular pattern. Several programs were analyzed with four patterns of hashing jumps summarized in Figure 5.3. All the hashing jumps in Figure 5.3 are intra-segment and indirect. The intra-segment jump implies that the size of the target specifier is 2 bytes. The indirect jump implies that the operand of the jump instruction is not the target, but rather, the offset to the target. All the hashing jump patterns in Figure 5.3 examine the number of offsets before accessing the eligible indirect target. This is accomplished by a compare instruction (cmp) and a conditional jump instruction (ja or jbe). For example, the value 7 in Pattern 1 of Figure 5.3 indicates that there are 8 possible indirect targets for the branch, ranging from 0 to 7. The "shift left (shl)" instruction or "add" instruction Figure 5.3 converts the byte index (1 byte) to the word index (2 bytes). Since register ax is used for computation and register bx is used as the base register, the "exchange (xchg)" instruction is introduced before the indirect jump instruction.

If the hashing jump was generated based on these regular patterns, the translator is able to resolve all of the hashing jump's possible targets. This is done by going to the offset of the indirect targets (for example, ofs\_0856 in Pattern 1), and fetching the values accordingly.

```

Pattern 1: (from Microsoft Paint Brush)

cmp

ax,7

; set range: 0 - 7

; punt if range > 7

short ofs_3462

ja

; double the index range, BYTE->WORD

shl

ax,1

xchg

bx,ax

; bx serves as base

word ptr cs:ofs_0865[bx] ; base indirect jump

jmp

Pattern 2: (from Microsoft Excel)

ax,0Ch

cmp

ja

ofs_1148

add

ax,ax

; another way to double the index

xchg

bx,ax

; range

word ptr cs:ofs_1121[bx]

jmp

Pattern 3: (from QVT Terminal)

ax,si

; another way to double the index

mov

ax,7

; range, si can be other register

cmp

ja

short ofs_5026

; as well

add

ax,si

xchg

bx,ax

word ptr cs:ofs_0866[bx]

jmp

Pattern 4: (from Microsoft Calculator)

ax,0Ch

cmp

short ofs_0977

jbe

; another way to skip if the

ofs_1044

; range is beyond the boundary

jmp

ofs_0977:

shl

ax,1

bx,ax

xchg

word ptr cs:ofs_0367[bx]

jmp

```

Figure 5.3 Hashing jumps with regular patterns.

```

Lib_Instance = LoadLibrary("Library_Name");

if ( Lib_Instance > 32 ) {

Func_Pointer = GetProcAddress(Lib_Instance, "Function_Name");

( *Func_Pointer )();

}

else {

ErrorHandler();

}

```

Figure 5.4 Example of calling a dynamically loaded function.

#### 5.1.5 Indirect DLL Function Calls

Application programs may dynamically request the operating system to load a library function and then call the loaded function. In Windows, this can be achieved by two system API function calls: LoadLibrary(), which requests Windows to load a specific dynamic link library, and GetProcAddress(), which obtains the address of the function in the loaded library. Figure 5.4 illustrates a code example for calling the dynamically loaded function. Upon returning from LoadLibrary(), the operating system tells the programmer whether or not the library is successfully loaded, and, if the library is not successfully loaded, the reason why. In Figure 5.4, the number 32 indicates that the library is successfully loaded if the return value is greater than 32.

Calling a dynamically loaded function is usually compiled as an indirect call. Figure 5.5 illustrates the assembly code found in Microsoft Word. At first glance, the indirect call instruction at line 14 seems unable to be determined since the content in data\_0262e is not defined until the call to GetProcAddress() at line 8 is executed. Since the translator is able to determine whether the dynamically loaded function is translated or not, the target of this type of branches is determinable.

```

(1)

call

far ptr LoadLibrary

; call LoadLibrary()

(2)

ds:data_0009e,ax

mov

(3)

cmp

ax,20h

; if return value greater than 32

(4)

short loc_2781

jbe

(5)

push

ax

(6)

push

СS

(7)

0C7h

push

(8)

call

far ptr GetProcAddress

; obtain an address to function

(9)

ds:data_0262e,ax

; address is stored in

mov

word ptr ds:data_0262e+2,dx ; data_0262e

(10)

mov

(11)

mov

ax, dx

(12)

ax, ds: data_0262e

or

(13)

short loc_2781

jz

(14)

call

dword ptr ds:data_0262e

; then call data_0262e

```

Figure 5.5 Indirect call to the dynamically loaded function (from Microsoft Word).

### 5.2 Relocation for Non-Determinable Target

Sometimes a code segment may contain some branches whose targets are prohibitively expensive to analyze on the fly. A code segment may also contain some branches whose targets cannot be determined without running the code. Section 5.2.1 will describe these cases. Section 5.2.2 proposes a run-time mechanism to solve this problem, and analyzes the occurrence for these instructions.

#### 5.2.1 Non-Determinable Branch Targets

Not all of the hashing jump patterns can be easily analyzed. Figure 5.6 shows some irregular hashing jump patterns. These patterns are found in QVT Terminal Emulator. The common situation with these patterns is that the range of the hashing jump cannot be easily determined. Determining the range often demands a complicated calculation. There is no general rule to outline a calculation pattern. For example, the value 3 in a right-shift instruction (shr) in

```

Pattern 5: (from QVT Terminal)

al,0F0h

and

sub

ax,0F000h

al,0Fh

test

ofs_0653

jnz

ax,3

shr

ax,26h

cmp

ofs_0653

ja

bx,ax

xchg

word ptr cs:ofs_0593[bx]

jmp

Pattern 6: (from QVT Terminal)

mov

c1,3

shl

al,cl

add

al, [bp-7]

xlat

inc

cl

al,cl

shr

[bp-7],al

mov

cbw

mov

bx,ax

bx,1

shl

jmp

word ptr cs:ofs_0636[bx]

```

Figure 5.6 Hashing jumps with irregular patterns.

Pattern 5 can be easily changed, depending on the compiler or assembly code writers. In this pattern, the potential targets that follow the hashing jump consist of 95 bytes. This is an odd number, which conflicts with the fact that the total byte size should be an even number for the hashing jump, since the "word ptr" cast expected a 2-byte target. For Pattern 6, determining the range may also require the translator to perform a tedious back trace and complicated calculation. It is even more difficult for the translator to automatically resolve the target if the old assembly code was hand optimized.

Figure 5.7 illustrates an example in which the target of the branch cannot be determined until the program is executed. The piece of code was detected in Microsoft Calculator. Before

```

; [ds:ofs_04C8] contains value 0

call far ptr INITTASK ; This Windows system API sets

; [ds:ofs_04C8] as side effect.

jmp word ptr ds:ofs_04C8 ; Now [ds:ofs_04C8] contains 004Bh

```

Figure 5.7 A dynamically determined branch target.

```

call sreg:[reg+disp] ; indirect target is in memory call reg ; indirect target is in register

jmp word ptr sreg:[reg+disp] ; not including regular hashing jumps jmp reg

sreg: segment registers

reg: general registers

disp: a constant value denoting the offset

```

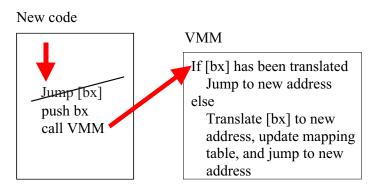

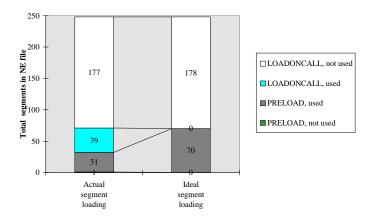

Figure 5.8 Branches with non-determinable targets.