# ENHANCING INSTRUCTION LEVEL PARALLELISM THROUGH COMPILER-CONTROLLED SPECULATION

#### BY

#### ROGER ALEXANDER BRINGMANN

B.S., University of South Alabama, 1983 M.S., University of Illinois at Urbana-Champaign, 1992

#### THESIS

Submitted in partial fulfillment of the requirements for the degree of Doctor of Philosophy in Computer Science in the Graduate College of the University of Illinois at Urbana-Champaign, 1995

Urbana, Illinois

# ENHANCING INSTRUCTION LEVEL PARALLELISM THROUGH COMPILER-CONTROLLED SPECULATION

Roger Alexander Bringmann, Ph.D.

Department of Computer Science

University of Illinois at Urbana-Champaign, 1995

Wen-mei W. Hwu, Advisor

The available instruction level parallelism (ILP) is extremely limited within basic blocks of non-numeric programs [1] [2] [3]. An effective VLIW or superscalar processor must optimize and schedule instructions across basic block boundaries to achieve higher performance. An effective structure for ILP compilation is the *superblock* [4]. The formation and optimization of superblocks increase ILP available to the scheduler along important execution paths by systematically removing constraints due to the unimportant paths. Superblock scheduling is then applied to extract the available ILP and map it to the processor resources.

The major technique employed to achieve compact superblock schedules is speculative execution. Speculative execution refers to executing an instruction before knowing that its execution is required. Such an instruction will be referred to as a speculative instruction. In the general sense, speculative execution may be engineered at run-time using dynamic scheduling or at compile-time. Superblock techniques utilize compile-time engineered speculative execution, or speculative code motion. A compiler may utilize speculative code motion to achieve higher performance in three major ways. First, in regions of the program where insufficient ILP exists to fully utilize the processor resources, useful instructions may be executed. Second, instructions starting long dependence chains may be executed early to reduce the length of critical paths. Finally, long latency instructions may be initiated early to overlap their execution with useful computation. Speculative execution is generally employed by all aggressive scheduling techniques. For example, Tirumalai et al. showed that modulo scheduling of while loops de-

pends on speculative support to achieve high performance [5]. Without speculative support, very little execution overlap between loop iterations is achieved.

This dissertation discusses the problems that must be addressed to perform compile-time speculation for acyclic global scheduling, classifies existing speculation models based upon how they solve these problems and discusses two new compile-time or compiler-controlled speculation models - write-back suppression speculation and safe speculation.

## **DEDICATION**

To my wife, Mary, and my children, Carrie and Johnathan.

Thank you for your love and your support!

#### ACKNOWLEDGMENTS

First and foremost, I would like to acknowledge my advisor, Professor Wen-mei W. Hwu, for his intellectual, financial, professional, and emotional support. I value his advise and look forward to applying what I have learned from him as I continue my career in industry.

As a member of the IMPACT group, I was able to meet and work with a number of amazing people in industry. I would like to thank Mike Johnson and David Witt from AMD, David Ditzell and Steve Richardson from SUN MicroSystems, Jack Mills from Intel, and Mike Schlansker and Vinod Kathail for technical conversations and insights over the years. I would like to thank Dr. Bob Ramakrishna Rau for his valuable insights on instruction speculation and scheduling.

The research would not have been possible without the support of the IMPACT research group - past and present. I would like to acknowledge their support in the form of coding, practice talks, research discussions, and friends. Many thanks to Sadun Anik, Dave August, Pohua Chang, William Chen, Derek Cho, Tom Conte, Brian Dietrich, Dave Gallagher, John Gyllenhaal, Grant Haab, Rick Hank, Andrew Hsieh, Liang Hsu, Sabrina Hwu, Tokuzo Kiyohara, Dan Lavery, Scott Mahlke, Krishna Subramanian, and Yoji Yamada. I would also like to thank Vicki McDaniel, the secretary for the IMPACT group, for her friendship and assistance.

Next, I would like to acknowledge friends who have made graduate school an enjoyable experience. I would like to thank Neal Alewine for the friendship of a fellow southerner who was also going back to graduate school after a prolonged period of time. I would like to thank Scott Mahlke and Rick Hank for putting up with me as a room mate during my last year and

a half. I would like to thank John Gyllenhaal and Liesl Little for the fun and pain provided by workout partners. Finally, I would like to acknowledge Sharad Mehrotra, Bill Pottenger and Krishna Subramanian for their friendship and support as we worked through the comprehensive exam process.

I would like to thank my parents, Norma and Wolfgang, for their encouragement towards excellence in school as well as their encouragement to pursue my doctoral dreams. I would also like to thank them for the emotional support when things were difficult. I would like to thank my brother, Michael, for the natural brotherly rivalry that helped motivate me to return for my doctorate after he completed his. I would also like to thank my in-laws, John and Elizabeth Cooper, for their support during graduate school.

Most importantly, I must thank my wife, Mary, and my children, Carrie and Johnathan, for their love. They stood behind me and believed in me when I decided to step away from a successful industry career and pursue my doctorate. They were there to help me enjoy the good times in my graduate studies and have provided the critical emotional support through the difficult times. The last year and a half have been very difficult for all of us and I hope that I can more than make up for this very soon!

## TABLE OF CONTENTS

| CI | HAPT | TER                                                      | PAGE |

|----|------|----------------------------------------------------------|------|

| 1  | INT  | RODUCTION                                                |      |

|    | 1.1  | Contributions                                            | 2    |

|    | 1.2  | Overview                                                 | 4    |

| 2  | OVI  | ERVIEW OF THE IMPACT COMPILER                            | 6    |

|    | 2.1  | The IMPACT Compiler                                      | 6    |

|    | 2.2  | Superblocks                                              | 10   |

|    |      | 2.2.1 Superblock Formation                               | 10   |

|    |      | 2.2.2 Superblock Enlarging Optimizations                 | 12   |

|    |      | 2.2.3 Superblock Dependence-Removing Optimizations       |      |

| 3  | COI  | MPILER-CONTROLLED SPECULATION                            | 17   |

|    | 3.1  | Accurate Reporting and Recovery from Exceptions          |      |

|    | 3.2  | Classification of Compiler-Controlled Speculation Models |      |

|    |      | 3.2.1 Avoid Errors Models                                |      |

|    |      | 3.2.2 Ignore Errors Models                               |      |

|    |      | 3.2.3 Resolve Errors Models                              |      |

|    | 3.3  | Existing Compiler-Controlled Speculation Techniques      |      |

|    |      | 3.3.1 Avoid Error Models                                 |      |

|    |      | 3.3.2 Ignore Error Models                                |      |

|    |      | 3.3.3 Resolve Error Models                               |      |

|    | 3.4  | Scheduling in the IMPACT Compiler                        |      |

|    | 9    | 3.4.1 Overview of the IMPACT Scheduler                   | 27   |

|    |      | 3.4.2 Superblock Scheduling                              |      |

|    |      | 3.4.3 Experimental Evaluation and Analysis               |      |

| 4  | WR   | ITE-BACK SUPPRESSION                                     | 43   |

| _  | 4.1  | Overview of Write-back Suppression                       |      |

|    | 4.2  | Architectural Extensions                                 |      |

|    | 1.2  | 4.2.1 Instruction Requirements                           |      |

|    |      | 4.2.2 Hardware Requirements                              |      |

|    |      | 4.2.3 Hardware Cost Estimates                            |      |

|    | 4.3  | Compiler Support                                         |      |

|    | 1.0  | 4.3.1 Superblock Scheduler Extensions                    |      |

|    |      | 4.3.2 Register Allocator Extensions                      |      |

|    | 4.4  | Write-back Suppression and Context Switching             |      |

|    | 4.5  | Experimental Evaluation                                  |      |

|    | 1.0  | 4.5.1 Methodology                                        |      |

|    |      | 4 5 2 Results                                            | 55   |

|   | 4.6                                                       | Conclusion                                               |  |  |  |  |

|---|-----------------------------------------------------------|----------------------------------------------------------|--|--|--|--|

| 5 | SAFE SPECULATION                                          |                                                          |  |  |  |  |

|   | 5.1                                                       | Overview                                                 |  |  |  |  |

|   |                                                           | 5.1.1 Determining Safety through Operand Inspection      |  |  |  |  |

|   |                                                           | 5.1.2 Determining Safety through Equivalent Instructions |  |  |  |  |

|   |                                                           | 5.1.3 Determining Safety through Graph Traversal         |  |  |  |  |

|   |                                                           | 5.1.4 Ensuring Safety in the Presence of Optimizations   |  |  |  |  |

|   |                                                           | 5.1.5 Related Work                                       |  |  |  |  |

|   | 5.2                                                       | Compiler Support                                         |  |  |  |  |

|   |                                                           | 5.2.1 Generating Use-Def Graphs                          |  |  |  |  |

|   |                                                           | 5.2.2 Evaluating Use-Def Graphs                          |  |  |  |  |

|   |                                                           | 5.2.3 Generating Call-Graphs for C Programs              |  |  |  |  |

|   |                                                           | 5.2.4 Identifying Side-Effect Free Subroutine Calls      |  |  |  |  |

|   |                                                           | 5.2.5 Determining Safety of Instructions                 |  |  |  |  |

|   | 5.3                                                       | Experimental Evaluation                                  |  |  |  |  |

|   |                                                           | 5.3.1 Experimental Results from Call-Graph Generation    |  |  |  |  |

|   |                                                           | 5.3.2 Experimental Results of Safe Speculation           |  |  |  |  |

|   |                                                           |                                                          |  |  |  |  |

| 6 | A STUDY OF THE EFFECTS OF COMPILER-CONTROLLED SPECULATION |                                                          |  |  |  |  |

|   |                                                           | INSTRUCTION AND DATA CACHES                              |  |  |  |  |

|   | 6.1                                                       | Expected Cache Effects                                   |  |  |  |  |

|   | 6.2                                                       | Experimental Evaluation                                  |  |  |  |  |

|   |                                                           | 6.2.1 Methodology                                        |  |  |  |  |

|   |                                                           | 6.2.2 Results                                            |  |  |  |  |

|   | 6.3                                                       | Conclusions                                              |  |  |  |  |

| 7 | COL                                                       | NCLUSION                                                 |  |  |  |  |

| • | 7.1                                                       | Summary                                                  |  |  |  |  |

|   | 7.2                                                       | Future Work                                              |  |  |  |  |

|   |                                                           |                                                          |  |  |  |  |

|   | REF                                                       | ${ m FERENCES}$                                          |  |  |  |  |

|   | VIT                                                       | A 160                                                    |  |  |  |  |

## LIST OF TABLES

| Tabl              | e                                                                                                                                                                                                                                  | Page  |

|-------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------|

| 3.1<br>3.2        | Benchmarks                                                                                                                                                                                                                         |       |

| 5.1<br>5.2<br>5.3 | Library routines that were implemented to support the analysis process Standard list of side-effect free subroutine calls found in the C libraries Summary of speedup results for safe speculation and existing speculation models | . 108 |

| 6.1               | Instruction opcodes and descriptions                                                                                                                                                                                               | . 129 |

| 6.2               | Branch taken frequencies. (Total corresponds to the total entrance frequency of the                                                                                                                                                |       |

|                   | loop.)                                                                                                                                                                                                                             | . 132 |

| 6.3               | Increase in execution frequency of speculated loads in the compress loop after schedul-                                                                                                                                            |       |

|                   | ing with the general speculation model                                                                                                                                                                                             | . 135 |

| 6.4               | Cache configurations used in experiments                                                                                                                                                                                           | . 137 |

| 6.5               | Icache access and miss rates at issue 1 (direct mapped cache)                                                                                                                                                                      | . 141 |

| 6.6               | Average icache access and miss rates at issue 8 (2-way set associative cache)                                                                                                                                                      | . 142 |

| 6.7               | Icache misses for the no speculation and general speculation models of the cccp loop                                                                                                                                               |       |

|                   | example at Issue 8 (2-way set associative, 4K Icache)                                                                                                                                                                              | . 143 |

| 6.8               | Deache access and miss rates at issue 1 (direct mapped cache)                                                                                                                                                                      | . 146 |

| 6.9               | Average dcache accesses and miss rates at issue 8 (2-way set associative cache)                                                                                                                                                    | . 147 |

| 6.10              | Deache misses for the no speculation and general speculation models of the compress                                                                                                                                                |       |

|                   | loop example at Issue 8 (2-way set associative, 4K Dcache)                                                                                                                                                                         | . 148 |

|                   |                                                                                                                                                                                                                                    |       |

## LIST OF FIGURES

| Figu | re                                                                                                                   | Page |

|------|----------------------------------------------------------------------------------------------------------------------|------|

| 2.1  | The IMPACT compiler                                                                                                  | . 7  |

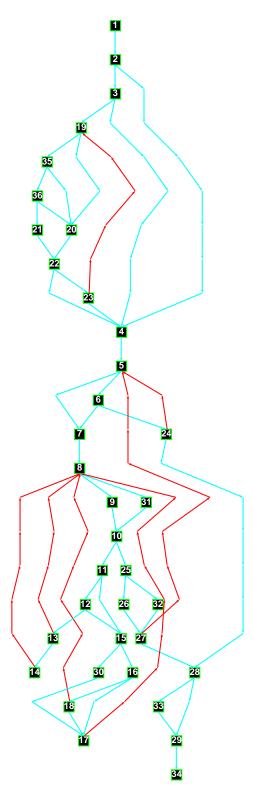

| 2.2  | An example of superblock formation                                                                                   | . 11 |

| 2.3  | An application of superblock ILP optimizations                                                                       |      |

| 3.1  | Example code segment, (a) un-scheduled code, (b) one speculated instruction, (c) two speculated instructions         | . 18 |

| 3.2  | Classifications of compiler-controlled speculation models.                                                           |      |

| 3.3  | Original code segment                                                                                                |      |

| 3.4  | Code segment after sentinel scheduling, before register allocation                                                   |      |

| 3.5  | Code segment after sentinel scheduling and register allocation                                                       |      |

| 3.6  | Organization of the IMPACT Instruction Scheduler                                                                     |      |

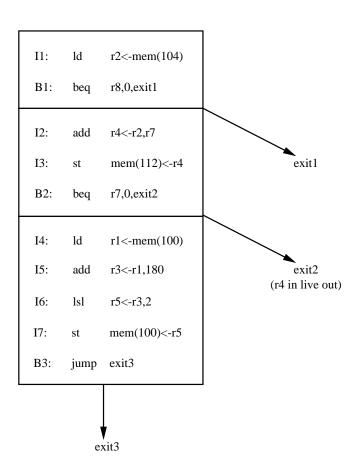

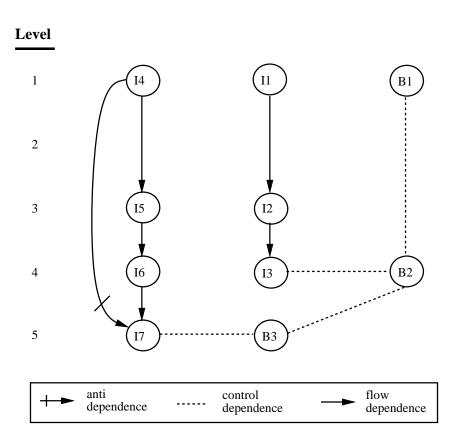

| 3.7  | An example superblock                                                                                                |      |

| 3.8  | Corresponding dependence graph for example superblock.                                                               |      |

| 3.9  | The Compute_Static_Priority algorithm determines the instruction priorities for each                                 |      |

|      | instruction                                                                                                          | . 35 |

| 3.10 | Maximum path lengths from starting instruction to branch                                                             | . 36 |

| 3.11 | Instruction priorities and schedule assuming branch probabilities are 20% for B1,                                    |      |

|      | 20% for B2 and $60%$ for B3                                                                                          | . 37 |

| 3.12 | Instruction priorities and schedule assuming branch probabilities are $20\%$ for B1, $60\%$ for B2 and $20\%$ for B3 | . 37 |

| 3.13 | Instruction priorities and schedule assuming branch probabilities are 60% for B1, 20% for B2 and 20% for B3          | . 38 |

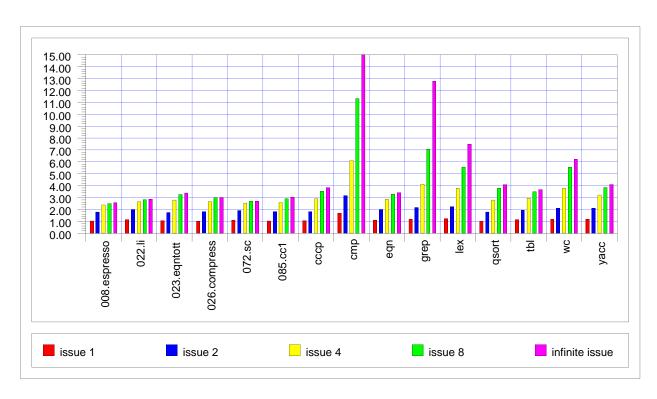

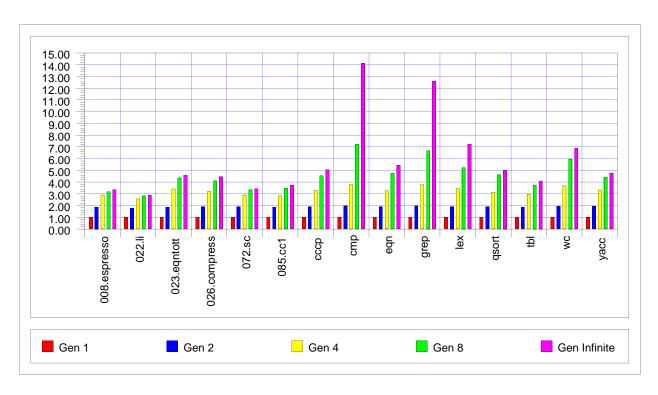

| 3.14 | Speedup results from the speculative yield scheduling heuristic                                                      |      |

| 3.15 |                                                                                                                      |      |

| 4.1  | Code segment after write-back suppression scheduling, before register allocation                                     | . 44 |

| 4.2  | Code segment after write-back suppression scheduling and register allocation                                         | . 46 |

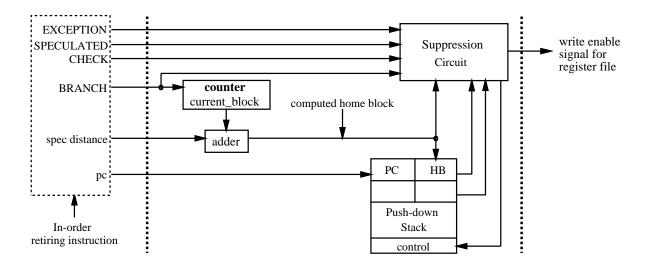

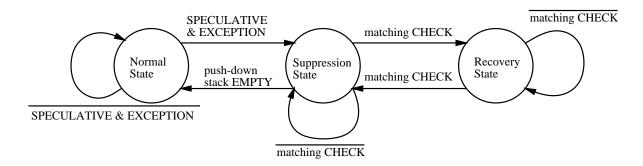

| 4.3  | Write-back suppression hardware                                                                                      | . 48 |

| 4.4  | Write-back suppression state machine                                                                                 | . 49 |

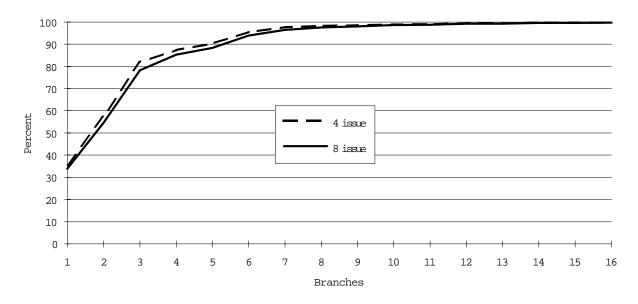

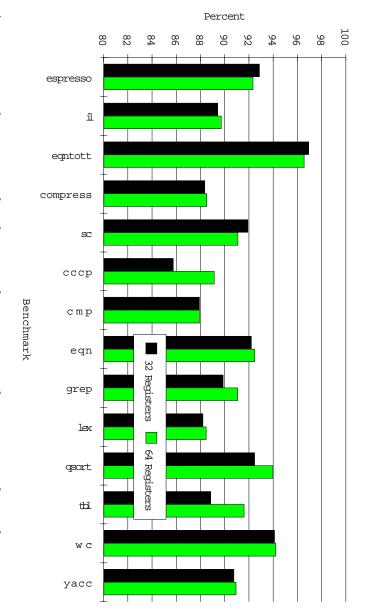

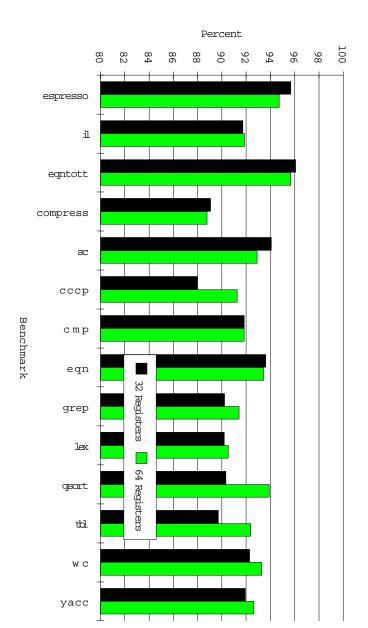

| 4.5  | Weighted speculation distances for PEIs                                                                              | . 56 |

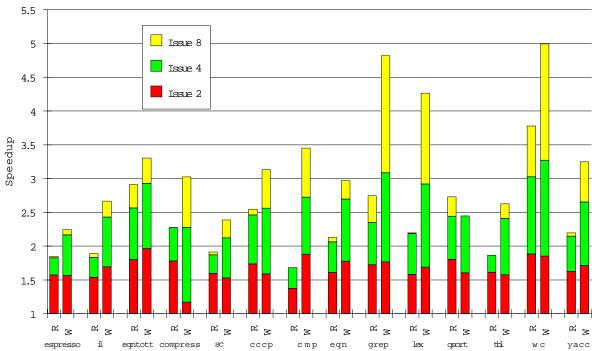

| 4.6  | Performance comparison of write-back suppression scheduling (W ) and restricted                                      |      |

|      | speculation (R) with 32 integer and 32 floating-point registers                                                      | . 57 |

| 4.7  | Performance results of write-back suppression relative to general speculation using                                  |      |

| 4.0  | an issue 1 processor.                                                                                                | . 59 |

| 4.8  | Performance results of write-back suppression relative to general speculation using                                  |      |

| 4.0  | an issue 2 processor                                                                                                 | . 59 |

| 4.9  | an issue 4 processor                                                                                                 | . 60 |

|      | all issue # piucessui                                                                                                |      |

| 4.10       | an issue 8 processor                                                                                                                                     | . 60  |

|------------|----------------------------------------------------------------------------------------------------------------------------------------------------------|-------|

| 5.1<br>5.2 | Example where potentially excepting instructions are always safe                                                                                         |       |

| r 9        | quired to determine safety.                                                                                                                              | . 68  |

| 5.3        | Examples where sentry instructions prevent run-time errors.                                                                                              |       |

| 5.4<br>5.5 | Example indicating the need to control optimization to maintain safety The Build_Use_Def_Graph algorithm generates a levelized use-def graph with cycles | . 16  |

|            | identified                                                                                                                                               | . 77  |

| 5.6        | The Recursively_Build_Use_Def_Graph algorithm generates a use-def graph starting at the initial start point.                                             | . 78  |

| 5.7        | The Traverse_Basic_Block algorithm adds relevant instructions to the current node                                                                        |       |

|            | in the use-def graph.                                                                                                                                    | . 81  |

| 5.8        | The Identify_Cycles algorithms is used to identify cycles in the graph to permit                                                                         |       |

| - 0        | correct graph levelization                                                                                                                               | . 82  |

| 5.9        | The DFS_Identify_Cycles algorithm is used to identify cycles in the graph to permit                                                                      | 0.6   |

| F 10       | correct graph levelization.                                                                                                                              | . 82  |

| 5.10       | The Levelize_Use_Def_Graph algorithm is used to push the level of all nodes to the                                                                       | 0.5   |

| F 11       | lowest levels in the graph that reach them.  Main function for wc                                                                                        |       |

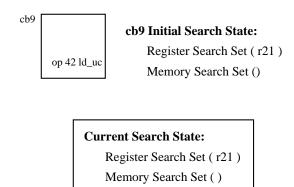

|            | Initial we loop prior to use-def graph generation.                                                                                                       |       |

|            | Instructions for we loop                                                                                                                                 |       |

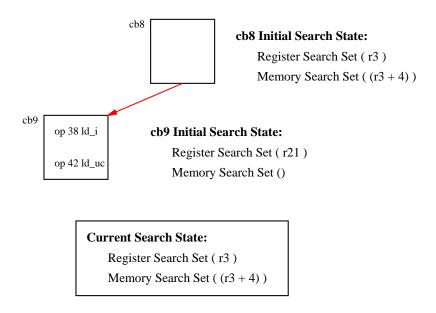

|            | Initial node of use-def graph containing instruction 42                                                                                                  |       |

|            | Final state of node after traversing all instructions in cb 9                                                                                            |       |

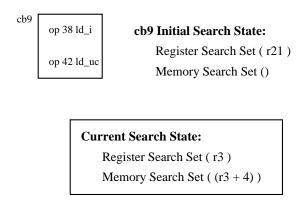

|            | Initial state of use-def graph prior to traversing cb 8                                                                                                  |       |

|            | Final state of use-def graph after traversing cb 8                                                                                                       |       |

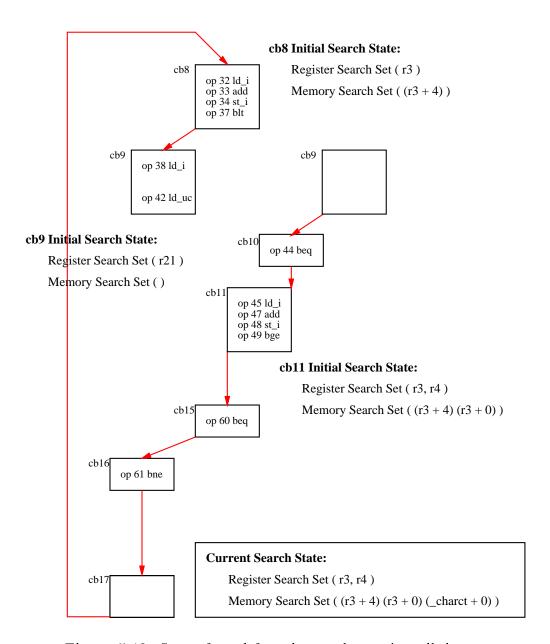

|            | State of use-def graph several recursive calls later                                                                                                     |       |

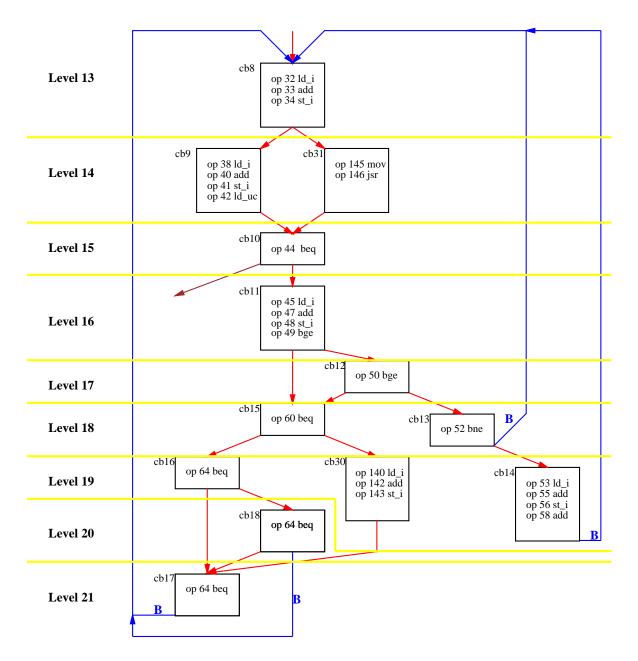

|            | Final use-def graph after merging nodes, identifying cycles and leveling graph                                                                           |       |

|            | The Evaluate_Use_Def_Graph algorithm is generate all values that reach the source                                                                        |       |

|            | operands of the instruction that terminates the graph.                                                                                                   |       |

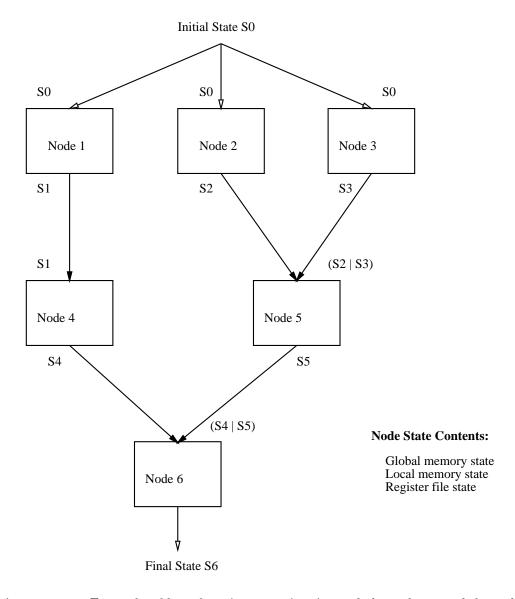

|            | Example of how function state is migrated through a use-def graph                                                                                        | . 96  |

| 5.22       | The Update_State algorithm is used to compute the register and memory state that reaches the node.                                                       | . 97  |

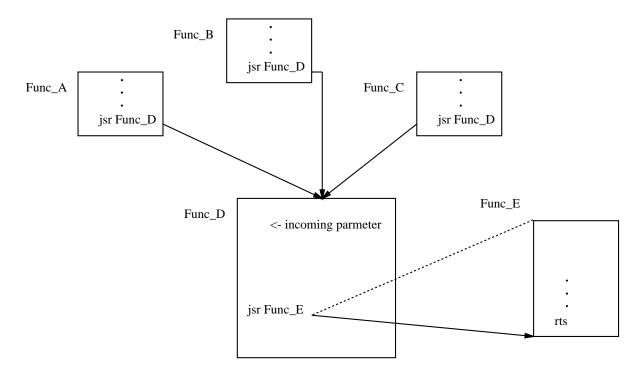

| 5.23       | Examples of how inter-procedural analysis is performed.                                                                                                  | . 99  |

|            | The Evaluate_State algorithm is used to record the register and memory state                                                                             |       |

| r or       | changes produced by a node in the use-def graph                                                                                                          | . 101 |

| 3.23       | The Evaluate_Subroutine_Call algorithm is used to record the register and memory                                                                         | 109   |

| 5 26       | state changes that occur as a result of traversing into a subroutine call The Build_Call_Graph algorithm is to generate a program call-graph             |       |

|            | The Identify_Side_Effect_Free algorithm is used to mark subroutine calls that are                                                                        | . 100 |

|            | to functions that do not modify global memory or memory that is passed in as a parameter.                                                                | 10"   |

| 5 28       | The Identify_Safe_PEI algorithm is the main calling routine used to identify instruc-                                                                    | . 107 |

| J.20       | tions that are safe for speculation with a program                                                                                                       | . 109 |

| 5.29 | The Identify_Trivially_Safe algorithm identifies instructions that can be identified as |

|------|-----------------------------------------------------------------------------------------|

|      | safe through explicit operand values                                                    |

| 5.30 | The Identify_Equivalence_Safe algorithm identifies instructions that can be identified  |

|      | as safe because of equivalent instructions that dominate the potentially excepting      |

|      | instruction                                                                             |

| 5.31 | The Identify_Non_Loop_and_Invariant_Safe algorithm identifies all non-loop and in-      |

|      | variant instructions that can be determined safe through use-def traversal 114          |

| 5.32 | The Identify_Variant_Safe algorithm identifies all variant instructions that can be     |

|      | determined safe through use-def traversal                                               |

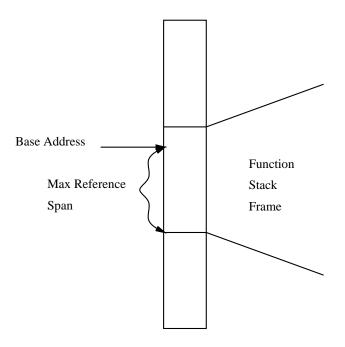

| 5.33 | Memory reference size limitations for stack based loads                                 |

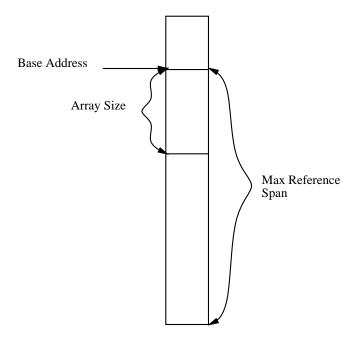

| 5.34 | Memory reference size limitations for load from global memory                           |

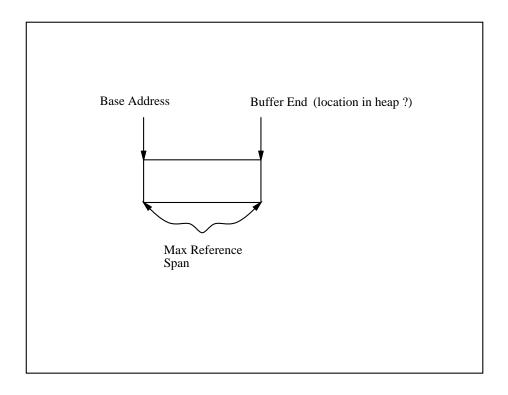

| 5.35 | Memory reference size limitations for load from dynamically allocated memory 118        |

| 5.36 | The Identify_Variant_Safe_Load algorithm identifies all variant load instructions that  |

|      | can be determined safe through use-def traversal                                        |

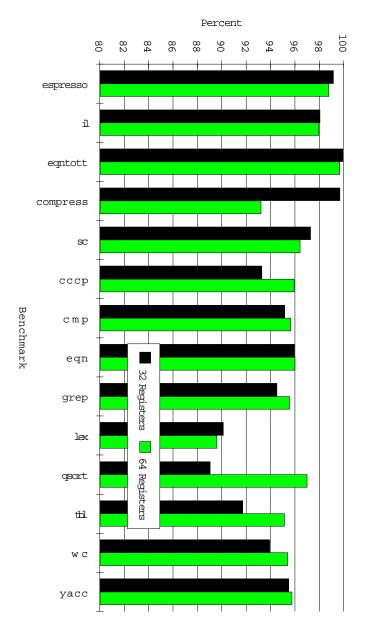

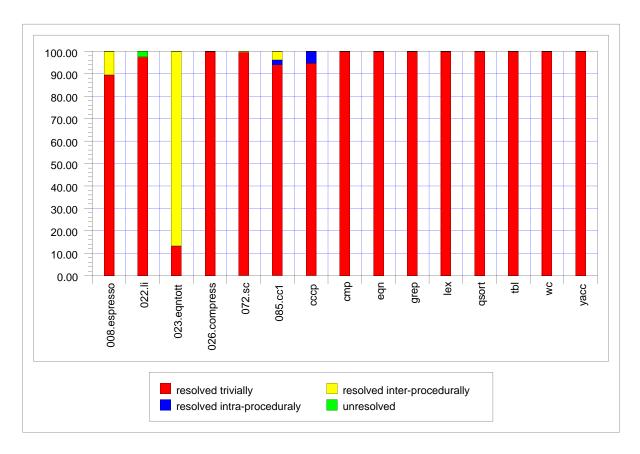

| 5.37 | Experimental results from call-graph generation                                         |

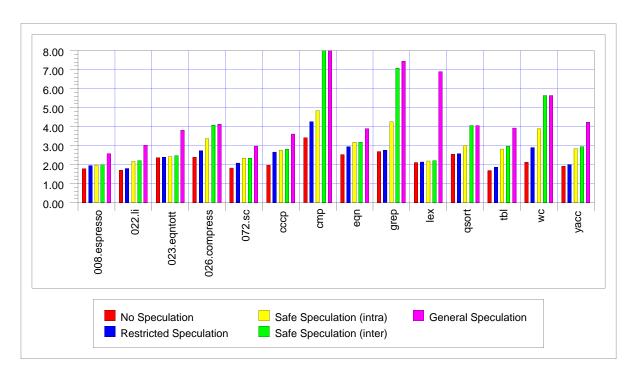

| 5.38 | Experimental results comparing safe speculation with existing speculation models 124    |

| 5.39 | C source code for the function cmppt                                                    |

| 6.1  | The most important loop in cccp scheduled using no speculation model                    |

| 6.2  | The most important loop in cccp scheduled using general speculation model 130           |

| 6.3  | Icache layout for cccp loop after no speculation model (16 instruction block) 132       |

| 6.4  | Icache layout for cccp loop after general speculation model (16 instruction block) 133  |

| 6.5  | The most important loop in compress scheduled using no speculation model 134            |

| 6.6  | The most important loop in compress scheduled using general speculation model 135       |

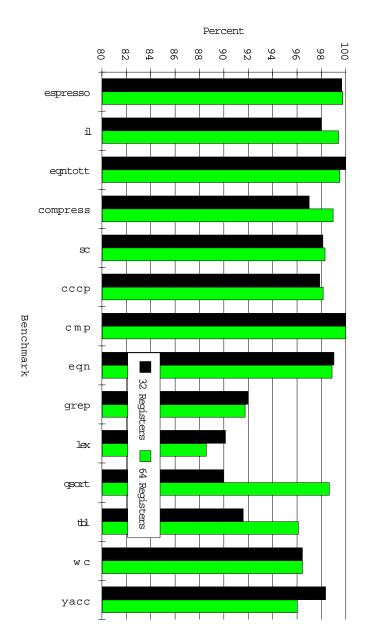

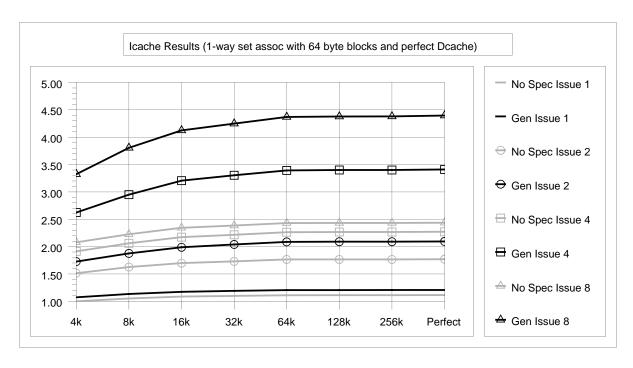

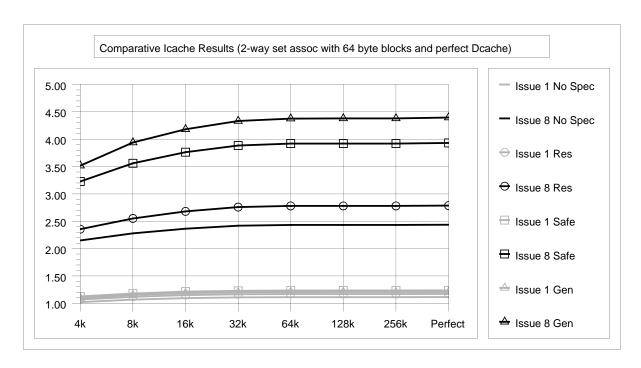

| 6.7  | Icache effects for no speculation and general speculation models                        |

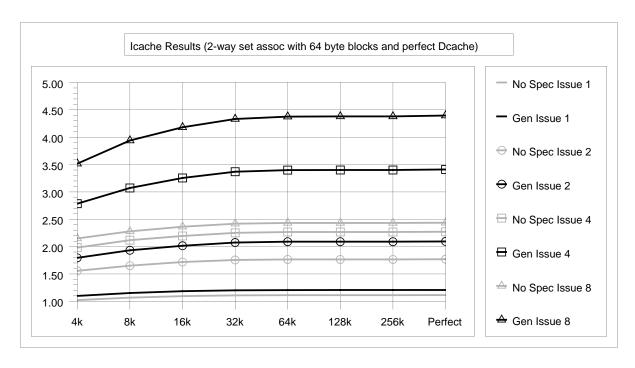

| 6.8  | Icache effects for no speculation and general speculation models                        |

| 6.9  | Icache effects for all speculation models at issue 1 and issue 8                        |

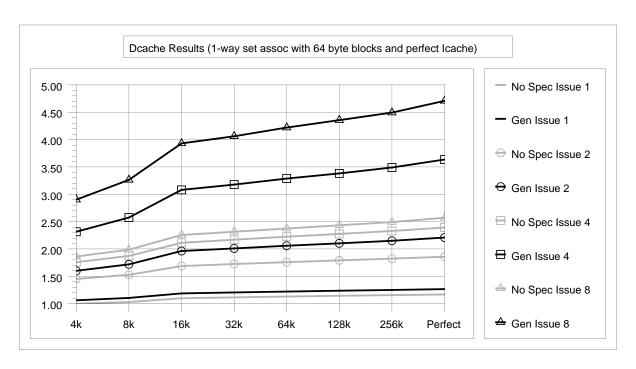

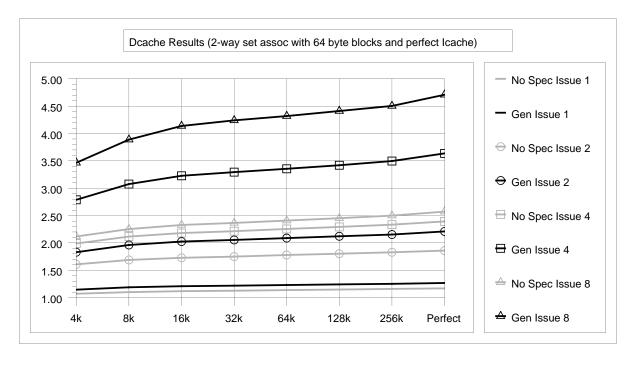

| 6.10 | Deache effects for no speculation and general speculation models                        |

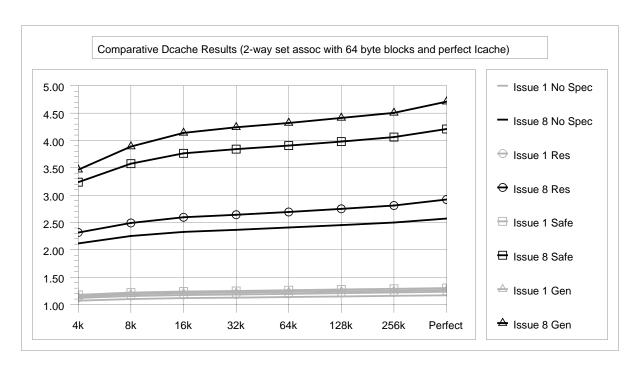

| 6.11 | Deache effects for no speculation and general speculation models                        |

| 6.12 | Deache effects for all speculation models at issue 1 and issue 8                        |

#### CHAPTER 1

#### INTRODUCTION

Instruction scheduling is the process used by the compiler to re-order instructions in an effort to minimize program execution time. Since instruction scheduling is NP-Hard, heuristics are used to approximate the best schedule. One common approach to scheduling is to perform list scheduling using greedy heuristics to approximate a globally optimal schedule [6]. Regardless of the scheduling heuristics, instructions are ordered based upon some priority mechanism. At each cycle, the instructions with the highest priority that have resolved all dependences and meet the issue requirements of the processor are scheduled.

The implementation of a scheduler is straightforward if list scheduling is applied within basic blocks. Unfortunately, there is insufficient instruction level parallelism available within basic blocks of non-numeric benchmarks to fully utilize the functional units of wide issue superscalar and VLIW architectures [1, 2, 7]. Therefore global scheduling techniques such as trace scheduling [8] and superblock scheduling [4] have been proposed to permit greater scheduling and optimization freedom beyond basic block boundaries. Using these techniques, the program is divided into a set of traces or superblocks that represent frequently executed paths. These traces or superblocks contain multiple basic blocks and as a result can contain multiple conditional branches. When building a dependence graph for a trace or superblock, control dependence arcs are added from conditional branches to subsequent instructions. In order to gain additional scheduling freedom beyond the natural basic block boundaries found within these traces or superblocks, the compiler must remove some of these control dependence arcs. This per-

mits speculation of instructions past conditional branches, thus the name compiler-controlled speculation.

When an instruction is speculated above a branch, it is executed regardless of the direction taken by the branch. To ensure correct program execution, the compiler must not alter the program execution result with speculative instruction scheduling. One requirement is that speculative instructions from one path of a conditional branch should not corrupt the source operands of instructions on the other path of the branch. This can be achieved by renaming the destination operands of the speculative instructions [4]. A more difficult requirement is that if the compiler speculates a potentially excepting instruction (PEI) from one path of a conditional branch, its exception condition must not alter the program state if the branch chooses the other path. In particular, the exception conditions from speculatively executed instructions must not corrupt the processor state or terminate the execution of the program unless their execution is confirmed by the subsequent branches.

This research focuses on compiler-controlled speculation models that have been applied to acyclic schedulers. The same speculation models provide the same benefits to cyclic scheduling models as well. The research topics were implemented in the IMPACT-I compiler developed at the University of Illinois [7]. The fundamental premise of the IMPACT project has been to provide a complete compiler implementation that allows quantification of the compiler and architectural extensions on the performance of superscalar and VLIW processors by compiling and executing large control-intensive programs.

#### 1.1 Contributions

The four major contributions of this dissertation are discussed below.

- The problems that all compiler-controlled speculation models must solve are discussed.

One of the major problems associated with all of these models is what should be done if an instruction that is beneficial to speculate can introduce run-time errors. For example, if a load is speculated above a branch that is preventing an illegal memory reference, the program could terminate during execution. These speculation models must either prevent speculation of these potentially excepting instructions, have some means of ignoring the exception until the direction of the branch is known, or ignore the exception. A classification for compiler-controlled speculation models is presented based upon the different approaches chosen to address this problem.

- Write-back suppression is an alternative to existing speculation models that require processor assistance to resolve exceptions resulting from compile-time speculation. This implementation takes advantage of in-order retire mechanisms present in many existing processors to systematically suppress register file updates for subsequent speculative instructions in the event of an error. This reduces the register pressure requirements which permits more aggressive speculation. Additionally, the technique requires much less processor support than existing techniques. Experimental results show that this technique can achieve performance results close to the most aggressive speculation models that ignore errors entirely.

- Safe speculation is presented as an alternative speculation model that permits aggressive compile-time speculation without processor extensions. This model uses intra-procedural and inter-procedural analysis to identify instructions that will not cause run-time errors and are therefore always safe to speculate. Additionally, the analysis methods provide information to later compilation phases to ensure that no transformations are performed

that would invalidate the safety analysis. This permits aggressive speculation of memory references to dynamically allocated buffers within loops. This model can be used in conjunction with other speculation models such as write-back suppression to reduce the instruction overhead required to detect exceptions by identifying instructions that will definitely not cause an exception.

• Previous work on compiler-controlled speculation has ignored the possible cache effects introduced from speculation. Indeed, aggressive speculation can lead to significantly higher instruction and data cache misses. This work has shown that even though aggressive speculation does introduce higher cache miss rates, the overhead from these additional cache misses does not negate the benefits of using aggressive speculation models even with very small caches. A detailed study of the effectiveness of limited and aggressive speculation models is performed to show these effects for both instruction and data caches. These studies show the effects over a variety of processor issue rates and cache configurations.

#### 1.2 Overview

This dissertation is composed of 7 chapters. Chapter 2 presents an overview of the organization and operation of the IMPACT Compiler. All compiler techniques discussed in this thesis are implemented within the framework of the IMPACT compiler.

Chapter 3 introduces the concept of compiler-controlled speculation. It describes the requirements that all compiler-controlled speculation models must address and classifies existing models based upon how they address these requirements. Examples speculation models are presented which fall into each of the speculation classes. Finally, an overview of the IMPACT scheduler is presented along with the global scheduling heuristics which take advantage of these

speculation models. Experimental results are presented to demonstrate the effectiveness of these scheduling heuristics. Write-back suppression is presented in Chapter 4 to present an alternative compiler-controlled speculation model that requires some processor assistance to perform recovery.

Safe speculation is presented in Chapter 5 as an alternative speculation model that can additionally be used the enhance the performance of existing speculation models. This model takes advantage of intra-procedural and inter-procedural analysis to determine instructions that meet the requirements discussed in Chapter 3. The algorithms presented have been implemented and tested on a suite of C benchmarks. Additionally the effectiveness of these techniques are compared against a number of existing speculation models.

Chapter 6 studies how limited and aggressive speculation models may affect instruction and data caches. These studies are shown over a variety of block sizes, cache sizes and associativities. The results are analyzed and conclusions on these effects are presented. Finally, Chapter 7 presents conclusions and directions for future research.

#### CHAPTER 2

#### OVERVIEW OF THE IMPACT COMPILER

### 2.1 The IMPACT Compiler

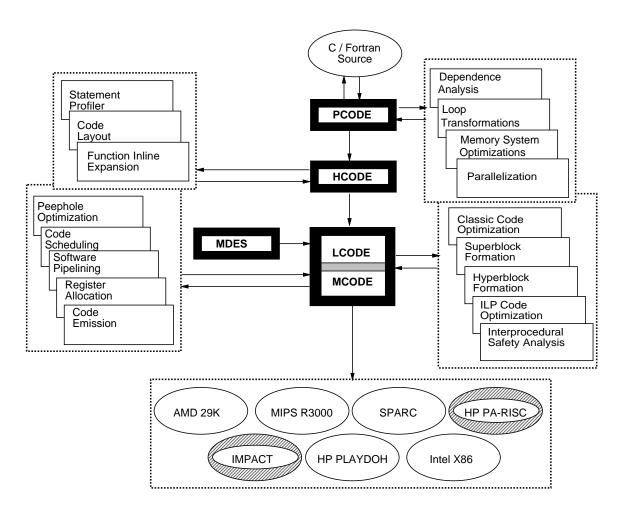

A block diagram of the IMPACT compiler is presented in Figure 2.1. The compiler is divided into 3 distinct parts based on the level of intermediate representation (IR) used. The highest level IR, *Pcode*, is a parallel C code representation with loop constructs intact. The Pcode level is ideal memory dependence analysis [9], loop-level transformations [10], and memory system optimizations [11]. The middle IR is referred to as *Hcode*. Hcode is a flattened C representation with simple if-then-else and goto control flow constructs. In Hcode, statement level profiling is performed. Additionally, profile-guided code layout and function in-line expansion are performed at this level [12].

The final level of IR in the IMPACT compiler is referred to as *Lcode*. Lcode is a generalized register transfer language similar in structure to most load/store processor assembly instruction sets. Lcode is logically subdivided into 2 subcomponents, the machine independent IR, Lcode, and the machine specific IR, *Mcode*. The data structures for both Lcode and Mcode are identical. The difference is that Mcode is broken down such that there is a one to one mapping between Mcode instructions to the target machines assembly language. Therefore, to convert Lcode to Mcode, the code generator breaks up Lcode instructions into 1 or more instructions which directly map to the target architecture. The annotation of Lcode instructions to Mcode instructions is performed for a variety of reasons including limited addressing modes, translating

Figure 2.1 The IMPACT compiler.

unsupported Lcode instructions into their equivalent supported Mcode instructions, and literal size mismatch [13].

At the Lcode level, all machine independent classic optimizations are applied [14]. These include constant propagation, forward copy propagation, backward copy propagation, common subexpression elimination, redundant load elimination, strength reduction, constant folding, constant combining, operation folding, operation cancellation, dead code elimination, jump optimization, unreachable code elimination, loop invariant code removal, loop global variable migration, loop induction variable strength reduction, loop induction variable elimination, and loop induction variable re-association. Additionally at the Lcode level, the intra-procedural and inter-procedural safety analysis discussed in this dissertation are performed. This includes identifying safe instructions for speculation and function calls that do not modify memory (side-effect free).

Superblock and hyperblock compilation techniques are all performed at the Lcode level [15]. Superblock support includes superblock formation using execution profile information, superblock classical optimization, and superblock ILP optimization. When predicated execution support is available in the target architecture, hyperblocks rather than superblocks are used as the underlying compilation structure. All superblock optimization techniques have also been extended to operate on hyperblocks. In addition, a set of hyperblock-specific optimizations to further exploit predicated execution support are available.

All code generation in the IMPACT compiler is performed at the Lcode level. The two largest components of code generation are the instruction scheduler and register allocator. Scheduling is performed via either acyclic global scheduling [16, 17] or software pipelining using modulo scheduling [18]. For the acyclic global scheduling, code scheduling is applied both

before register allocation (prepass scheduling) and after register allocation (postpass scheduling) to generate an efficient schedule. For software pipelining, loops targeted for pipelining are identified at the Pcode level and marked for pipelining. These loops are scheduled using software pipelining and all other code is scheduled using the global scheduler. Graph coloring based register allocation is utilized for all target architectures [19]. The register allocator employs execution profile information if it is available to make more intelligent decisions. For each target architecture, a set of specially tailored peephole optimizations are performed. These peephole optimizations are designed to remove inefficiencies during Lcode to Mcode conversion, take advantage of specialized opcodes available in the architecture, and to remove inefficient code inserted by the register allocator [13].

A detailed machine description database, *Mdes*, for the target architecture is also available to all Lcode compilation modules [20]. The Mdes contains a large set of information to assist with optimization, scheduling, register allocation, and code generation. Information such as the number and type of available function units, size and width of register files, instruction latencies, instruction input/output constraints, addressing modes, and pipeline constraints is provided by the Mdes. The Mdes is queried by the optimization phases to make intelligent decisions regarding the applicability of transformations. The scheduler and register allocator rely more heavily on the Mdes to generate efficient as well as correct code.

Seven architectures are actively supported by the IMPACT compiler. These include the AMD 29K [13], MIPS R3000 [21], SPARC [22], HP PA-RISC, and Intel X86. The other two supported architectures, IMPACT and HP Playdoh [23], are experimental ILP architectures. These architectures provide a framework for compiler and architecture research. The IMPACT architecture is parameterized superscalar processor with an extended version of the HP PA

instruction set. Varying levels of support for speculative execution and predicated execution are available in the IMPACT architecture.

#### 2.2 Superblocks

#### 2.2.1 Superblock Formation

A superblock is a block of instructions in which control may only enter from the top but may leave at one or more exit points. When execution reaches a superblock, it is likely that all basic blocks in that superblock are executed. Superblocks allow the compiler to effectively optimize and schedule across basic block boundaries by removing the constraints due to side entrances within a sequence of basic blocks.

Superblocks are formed in two steps. Traces within a program (sets of basic blocks which tend to execute in sequence [8]) are first identified using execution profile information [24]. Tail duplication is then performed to eliminate any side entrances to the trace [25]. The basic blocks in a superblock need not be consecutive in the code. However, our implementation restructures the code so that all blocks in a superblock appear in consecutive order to the optimizer and scheduler.

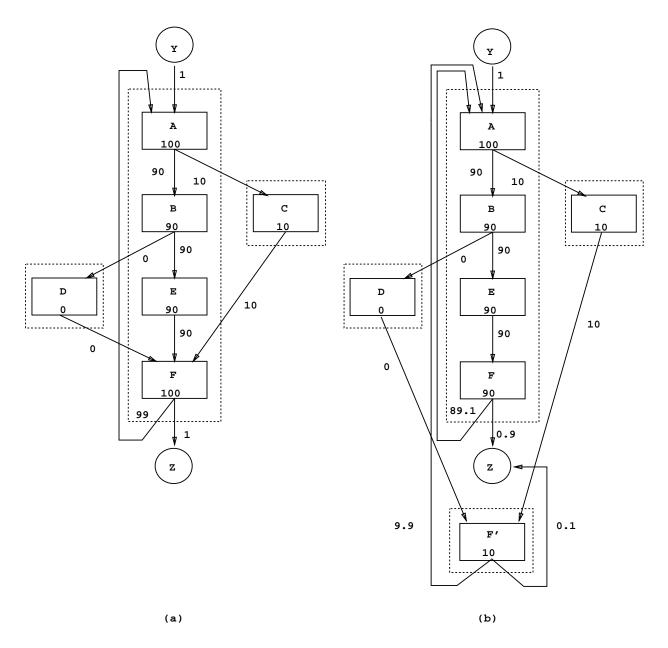

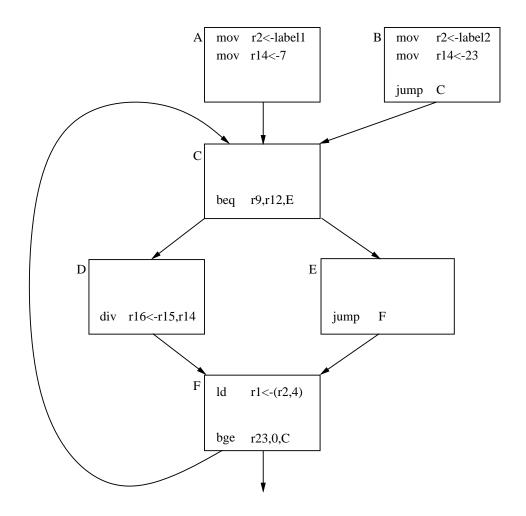

Formation of superblocks is best illustrated with an example. Figure 2.2(a) shows a weighted flow graph which represents a loop code segment. The nodes correspond to basic blocks and arcs correspond to possible control transfers. The *count* of each basic block indicates the execution frequency of that basic block. In Figure 2.2(a), the *count* of  $\{A, B, C, D, E, F\}$  is  $\{100, 90, 10, 0, 90, 100\}$ , respectively. The *count* of each control transfer indicates the frequency of invoking these control transfers. In Figure 2.2(a), the *count* of  $\{A \to B, A \to C, B \to D, B \to E, C \to F, D \to F, E \to F, F \to A\}$  is  $\{90, 10, 0, 90, 10, 0, 90, 99\}$ , respectively. Clearly, the most

Figure 2.2 An example of superblock formation.

frequently executed path in this example is the basic block sequence A, B, E, F > 0. There are three traces: A, B, E, F > 0, A and A are three traces: A, B, E, F > 0, A and A are three traces: A, B, E, F > 0, A and A are three traces: A, B, E, F > 0, A and A are three traces: A, B, E, F > 0, A and A are three traces in order to ensure that the program control can only enter at the top basic block. In Figure 2.2(a), we see that there are two control paths that enter the A, B, E, F > 0 trace at basic block A are three traces a

#### 2.2.2 Superblock Enlarging Optimizations

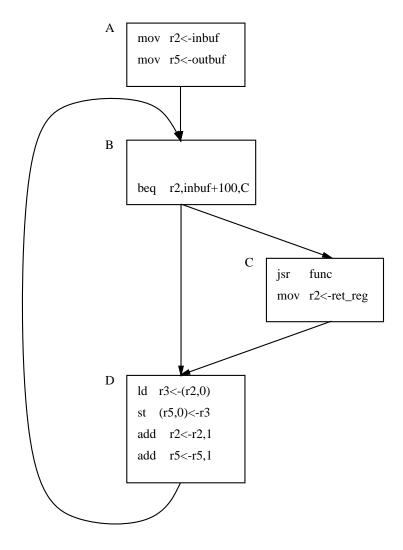

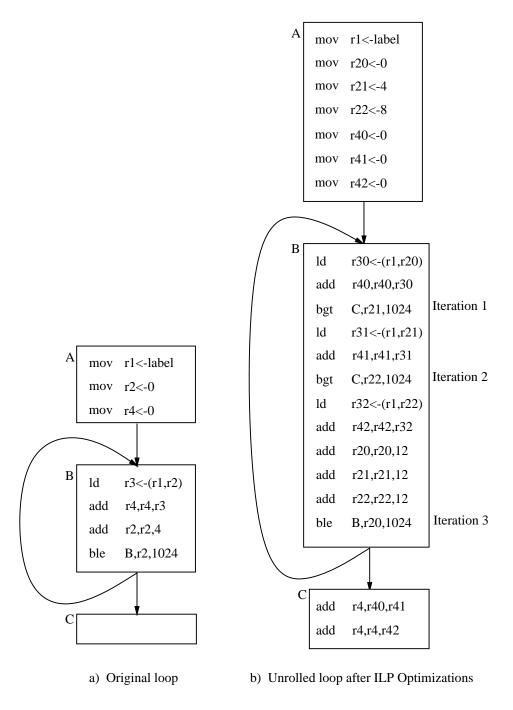

The first category of superblock ILP optimizations is superblock enlarging optimizations. The purpose of these optimizations is to increase the size of the most frequently executed superblocks so that the superblock scheduler can manipulate a larger number of instructions. It is more likely the scheduler will find independent instructions to schedule at every cycle in a superblock when there are more instructions to choose from. An important feature of superblock enlarging optimizations is that only the most frequently executed parts of a program are enlarged. This selective enlarging strategy keeps the overall code expansion under control [25]. Three superblock enlarging optimizations are described as follows.

Branch Target Expansion. Branch target expansion expands the target superblock of a likely taken control transfer which ends a superblock. The target superblock is copied and appended to the end of the original superblock.

Loop Peeling. Superblock loop peeling modifies a superblock loop (a superblock which ends with a likely control transfer to itself) which tends to iterate only a few times for each loop execution. The loop body is replaced by straight-line code consisting of the first several iterations of the loop.<sup>1</sup> The original loop body is moved to the end of the function to handle executions which require additional iterations. After loop peeling, the most frequently executed preceding and succeeding superblocks can be expanded into the peeled loop body to create a single large superblock.

**Loop Unrolling.** Superblock loop unrolling replicates the body of a superblock loop which tends to iterate many times. To unroll a superblock loop N times, N-1 copies of the superblock are appended to the original superblock. The control transfers in the first N-1 loop bodies are adjusted or removed if possible to account for the unrolling.

#### 2.2.3 Superblock Dependence-Removing Optimizations

The second category of superblock ILP optimizations is superblock dependence removing optimizations. These optimizations eliminate data dependences between instructions within frequently executed superblocks, which increases the ILP available to the code scheduler. As a side effect, some of these optimizations increase the number of executed instructions. However, by applying these optimizations only to frequently executed superblocks, the code expansion incurred is regulated. Five superblock dependence removing optimizations are described as follows.

Register Renaming. Register renaming removes anti, output, and control dependences between instruction pairs within a superblock [26].

<sup>&</sup>lt;sup>1</sup>Using the profile information, the loop is peeled its expected number of iterations.

Operation Migration. Operation migration moves an instruction from a superblock where its result is not used to a less frequently executed superblock. By migrating an instruction, all of the data dependences associated with that instruction are eliminated from the original superblock.

Induction Variable Expansion. Induction variable expansion eliminates redefinitions of induction variables within an unrolled superblock loop. Each definition of the induction variable is given a new induction variable, thereby eliminating all anti, output, and flow dependences among the induction variable definitions. However an additional instruction is inserted into the loop preheader to initialize each newly created induction variable. Patch code is inserted if the variable is used outside the superblock.

Accumulator Variable Expansion. Accumulator variable expansion is similar to induction variable expansion. Anti, output, and flow dependences between instructions which accumulate a total are eliminated by replacing each definition of accumulator variable with a new accumulator variable. Unlike induction variable expansion, though, the increment or decrement value is not required to be constant within the superblock loop. Again, initialization instructions for these new accumulator variables must be inserted into the superblock preheader. Also, the new accumulator variables are summed at all superblock exit points to recover the value of the original accumulator variable.

Operation Combining. Operation combining eliminates the flow dependence between a pair of instructions each of which has a constant source operand [27]. The flow dependence is removed by modifying the flow dependent instruction's constant source operand and replacing the flow dependent source operand with an appropriate variable.

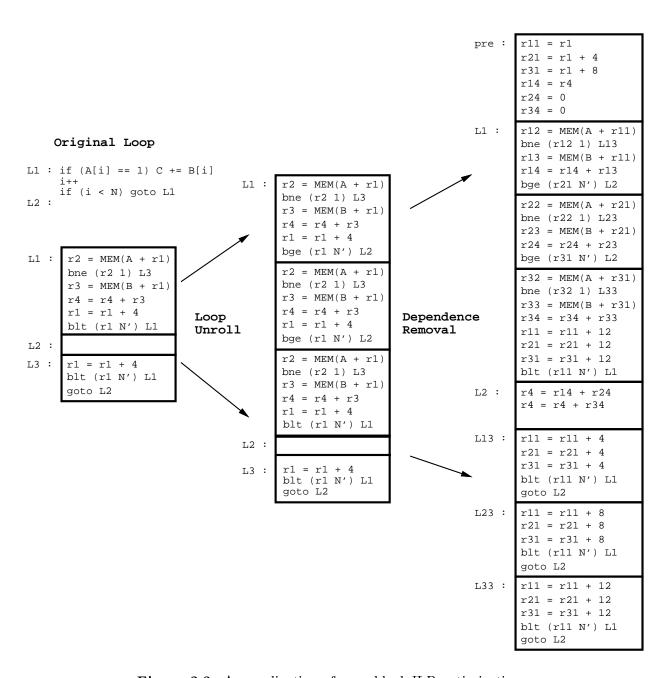

Figure 2.3 An application of superblock ILP optimizations.

Example. An example to illustrate loop unrolling, register renaming, induction variable expansion, and accumulator variable expansion is shown in Figure 2.3. This example assumes that the condition of the if statement is more often true than false. Note that only the frequently executed path is replicated during loop unrolling. Also, there are still dependences across replicated loop bodies due to the increment of loop counter i (r1) and the accumulation into the variable C (r4). Furthermore, the reuse of temporary registers r2 and r3 introduces anti and output dependences across replicated loop bodies. The application of superblock dependence removing optimizations eliminates all these dependences. After all superblock ILP optimizations are applied, the execution of the unrolled loop bodies may be completely overlapped by the superblock scheduler.

#### CHAPTER 3

#### COMPILER-CONTROLLED SPECULATION

One of the critical requirements for all compiler transformations is not to introduce program errors. Scheduling errors can occur as a result of illegal re-ordering of operations that change the final result of the program. Obeying data dependences during scheduling will prevent illegal re-ordering. However, global scheduling introduces the possibility of another potential program error - premature program termination. This could occur as a result of speculating a divide above a conditional branch. If the conditional branch was either explicitly or implicitly preventing a zero divisor from reaching the divide, the program could terminate. All compiler-controlled speculation models are required to prevent program termination. The models differ in their approaches to detect the exception, report the exception and in some cases actually recover from the exception. The next section provides a detailed explanation of the requirements of compiletime speculation models if they are to accurately report exceptions and recover from exceptions. Section 3.2 classifies existing speculation models by their approach to handling exceptions or preventing these exceptions occurring. Section 3.3 introduces examples of speculation models that fall into each category. Finally, Section 3.4 introduces the IMPACT global scheduler and the heuristics used to permit efficient speculation.

| <u>I Instruction</u> | I Instruction       | I Instruction       |

|----------------------|---------------------|---------------------|

| 1 beq r5,0,L1        | 2 ld r7,mem(r5) (S) | 2 ld r7,mem(r5) (S) |

| 2 ld r7,mem(r5)      | 1 beq r5,0,L1       | 3 add r6,r6,r7 (S)  |

| 3 add r6,r6,r7       | 3 add r6,r6,r7      | 1 beq r5,0,L1       |

| (a)                  | (b)                 | (c)                 |

Figure 3.1 Example code segment, (a) un-scheduled code, (b) one speculated instruction, (c) two speculated instructions.

#### 3.1 Accurate Reporting and Recovery from Exceptions

Figure 3.1 illustrates the problems that compiler-controlled speculation models must address to accurately report and recover exceptions. In Figure 3.1(a), instruction I<sub>1</sub> guards against an invalid memory access by I<sub>2</sub>. Under normal situations, the address for I<sub>2</sub> is valid. Thus the branch is usually not taken. Instruction I<sub>3</sub> uses the contents of memory to perform a computation. Assuming that the branch has a one cycle latency, the load has a 2 cycle latency and the add has a 1 cycle latency, the shortest latency possible for these three instructions is 4 cycles. Assume that the compiler has renamed the destination registers of I<sub>2</sub> and I<sub>3</sub> so that these instructions cannot corrupt the source operands of instructions on the taken path of the branch instruction. Since the branch is usually not taken, it is feasible to speculate I<sub>2</sub> above I<sub>1</sub> producing the schedule shown in Figure 3.1(b) (an instruction denoted by (S) is speculated). This new schedule has a 3 cycles latency and would be a more desirable schedule, if it were legal.

For the schedule in Figure 3.1(b) to be legal, it must not alter the program behavior regardless of the direction the branch takes at run time. If the contents of r5 in  $I_2$  is zero, the load will cause an invalid memory access exception. If the exception is permitted to occur, an error that  $I_1$  was designed to prevent will be falsely reported. One solution to this problem is

to delay reporting the exception until the direction of the branch is taken (delayed exception).

This requires that the knowledge of the exception must be maintained for later use.

A slightly different problem occurs if the exception caused by  $I_2$  was not an invalid memory access but instead was a page fault. If we delay the exception until after the branch direction is known, we must be able to determine that  $I_2$  caused the exception. Once we know that the branch is not taken, we must re-execute  $I_2$  and permit the exception to occur. This allows the exception to be reported accurately.

The problem becomes even more complicated if the scheduler decided to also move  $I_3$  above  $I_1$  as shown in Figure 3.1(c). If  $I_3$  is permitted to update r6, after an exception by  $I_2$ , it will be corrupted. If we re-execute  $I_3$  after the exception from  $I_2$  is resolved in hopes of correcting the error, r6 will still be corrupted. Therefore, we have reached an unrecoverable state.

This example has shown the four problems that must be solved in order for the compiler to accurately report and recover from exceptions resulting speculation of potentially excepting instructions (SPEIs). They include detecting a delayed exception, determining the instruction that caused the exception, protecting source operands until the exception is resolved and recovering from the exception. While the typical exception is viewed as one that caused program termination, this does not need to be the case such as a page fault.

## 3.2 Classification of Compiler-Controlled Speculation Models

In order to gain greater scheduling freedom, instructions must be allowed to speculate above conditional branches found within a trace or superblock. In some cases, speculation of these instructions can introduce a run-time errors that can cause unexpected program termination. Compiler-controlled speculation models can be classified by what the scheduler will do if the

- (1) **Avoid Errors** do not permit the instruction to speculate if it could cause a run-time error [7].

- (2) **Ignore Errors** assumes that the likelihood of the instruction causing an errors is small. Therefore, a non-excepting form of the instruction will be used instead of the excepting form. As a result, if the speculated instruction does cause an error, the error will be lost. This model requires non-excepting forms of each potentially excepting instruction that is speculated [7].

- (3) **Resolve Errors** speculates instructions that could cause a run-time error but uses a combination of compiler and processor extensions extensions to permit corruption of the processor state until it is known whether the instruction should except. Each model also provides a mechanism for recovery in the event that the speculated instruction does except and program execution should resume.

Figure 3.2 Classifications of compiler-controlled speculation models.

an instruction that should be speculated could cause program termination. Figure 3.2, shows three categories that speculation models fall into if this circumstance occurs.

#### 3.2.1 Avoid Errors Models

This scheduling model assumes that incorrect program execution must always be detected. Therefore, the compiler can only speculate instructions that it can guarantee will never cause an exception. In most processors, this prevents speculation of all instructions that reference memory due to potential illegal address references, as well as integer divide and remainder instructions due to potential divide-by-zero errors. Additionally floating point instructions typically are not speculated since they can cause numerous error conditions including underflow and overflow. Using these constraints, this category can be very restrictive to scheduling freedom.

#### 3.2.2 Ignore Errors Models

These models require a non-excepting form of every potentially excepting instruction that can be speculated. Thus, if a potentially excepting instruction should be speculated, it will

be replaced by its non-excepting form. The objective of this category is to permit aggressive speculation. The obvious disadvantage is that real program errors could go undetected or cause subsequent errors later in the program. For example, if we speculate a divide above a branch, this model will replace the divide by a non-trapping form of the divide. If the branch branch was implicitly preventing a divide-by-zero, speculating above the branch increases the risk of the divide-by-zero. If we would have always branched around the divide, then the divide-byzero would never have occurred and hiding the exception using the non-trapping divide causes no harm. However, if there is a programming error, it is possible that the divide-by-zero could happen and we are preventing this error from ever being reported. This could result in some illegal value being propagated to instructions that subsequently were intended to use the result of the divide. This could cause program termination at some later point that could make it difficult to isolate the real problem. The IEEE 754 floating-point standard actually supports this model. The standard requires that floating-point exceptions are sticky. However, while the existence of a trap-handler for these exceptions is recommended, it is not required. The following list provides some examples of architectures that fall into this category in limited circumstances.

- (1) Multiflow non-trapping floating point instructions [28]

- (2) Cydra 5 non-trapping floating point instructions, ability to disable exceptions for memory and arithmetic operations [29].

- (3) HP Precision Architecture non-trapping floating point instructions, non-trapping dereferenced null pointer [30].

- (4) Sun SPARC V8 and V9 non-trapping floating point instructions and non-trapping load instructions [31].

#### 3.2.3 Resolve Errors Models

Just like the prevent errors category, this category assumes that the scheduled program should produce the exact same results as the unscheduled program. However, its ultimate goal is to attain performance results comparable to the ignore errors category. To accomplish this, the speculation model defines compiler and processor extensions that are used to delay reporting an exception until it is determined that the exception should be reported, keep track of the instruction that caused the exception, protect source operands until the exception is resolved and permit recovery from the exception. Thus, potentially excepting instructions may be speculated freely at compile-time as long as the requirements for the recovery mechanism are followed.

### 3.3 Existing Compiler-Controlled Speculation Techniques

#### 3.3.1 Avoid Error Models

Restricted speculation (formally called restricted code percolation) [7] assumes that correct program execution is always required. Using this model, the compiler can only speculate instructions that will never cause an exception. As such, this model ignores even trivial cases where the context in which the instruction is used, can sometimes indicate if the instruction will cause an exception. Chapter 5 proposes a new speculation model that meets the requirements of this category but uses information that can be gathered intra-procedurally and inter-procedurally to identify potentially excepting instructions that will never cause exceptions.

#### 3.3.2 Ignore Error Models

General speculation (formally called general code percolation) falls under this category. This aggressive model assumes a non-excepting form for every potentially instruction. This model is used as a measure of the maximum performance that speculation models can attain in the absence of register constraints and cache constraints.

#### 3.3.3 Resolve Error Models

This section introduces two speculation models that accurately report exceptions and permit recovery. These speculation models also support aggressive compile-time speculation.

#### 3.3.3.1 Instruction Boosting

Instruction boosting has been proposed for handling exceptions with compiler-controlled speculative execution [32] [33]. The four problems associated with exception detection and recovery are handled with a combination of hardware support (shadow register files) and compiler generated recovery blocks. Detecting delayed exceptions is handled by recording an exception condition raised by a speculative instruction in the appropriate shadow register file. At the excepting instruction's commit point, the contents of the shadow register file are examined to determine if an exception condition exists. The excepting instruction is identified by sequentially re-executing all speculative instructions which are committed by the same branch instruction. The exception condition is therefore regenerated in a sequential processor state. Operands of speculative instructions are preserved by ensuring that speculative instructions do not update the architectural register file until they are committed. Therefore, a speculative instruction may always be re-executed by retrieving its operands from the architectural register register file until they are committed.

ter file. Finally, recovery is handled with traditional exception recovery techniques since the exception is regenerated in a sequential processor state.

Although boosting provides good support for accurate detection and handling of exceptions for SPEIs, it does so with excessive hardware overhead. The scheme requires multiple copies of register files to implement the shadow registers. The fact that exception recovery requires recovery code blocks also increases code size by about two times, which adds significantly to the pressure on the memory system [33].

#### 3.3.3.2 Sentinel Scheduling

An alternative scheme to enable exception detection and recovery with compiler-controlled speculative execution is sentinel scheduling [34] [35]. Sentinel scheduling is a compiler based technique that requires few changes to the processor architecture. The four problems associated with exception detection and recovery are handled using exception tags added to each architectural register and compiler scheduling and register allocation support. Delayed exceptions are detected by marking exception conditions in the destination register of excepting speculative instructions. The PC of the speculative instruction is also placed in the destination register. Subsequent speculative instructions which use the result of an excepting speculative instruction propagate the PC and exception tag to their destination. A subsequent non-speculative indirect use of the excepting speculative instruction's destination register signals any exception conditions that are present. The excepting instruction is identified by the PC contained in the corresponding register whose exception tag is set.

Source operands for speculative instructions are preserved by ensuring the scheduler and register allocator do not allow any instruction to overwrite a speculative instruction's source

|    |        |             | Current | Speculation | Home  |

|----|--------|-------------|---------|-------------|-------|

| I  | Instru | ction       | Block   | Distance    | Block |

| 1  | add    | v3,v2,v4    | 0       | 0           | 0     |

| 2  | add    | v1,v2,4     | 0       | 0           | 0     |

| 3  | beq    | v1,0,L1     | 0       | 0           | 0     |

|    |        |             |         |             |       |

| 4  | load   | v5,mem(v1)  | 1       | 0           | 1     |

| 5  | store  | mem(v5), v2 | 1       | 0           | 1     |

| 6  | div    | v6,v4,v7    | 1       | 0           | 1     |

| 7  | add    | v8,v0,v6    | 1       | 0           | 1     |

| 8  | bne    | v8,v2,L2    | 1       | 0           | 1     |

|    |        |             |         |             |       |

| 9  | load   | v9,mem(v8)  | 2       | 0           | 2     |

| 10 | add    | v9,v9,4     | 2       | 0           | 2     |

| 11 | store  | mem(v9),v2  | 2       | 0           | 2     |

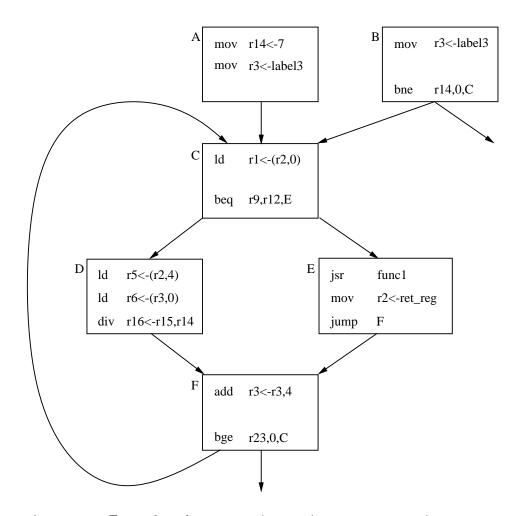

Figure 3.3 Original code segment.

operands before a non-speculative instruction checks the exception condition of the speculative instruction. Finally, recovery is performed by setting the PC to the excepting instruction's PC and re-executing all speculative instructions until the check instruction is reached.

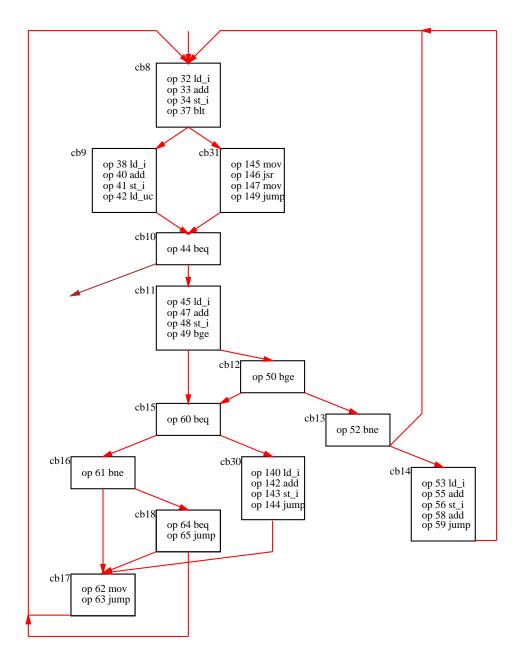

An example code segment to illustrate speculative execution with sentinel scheduling is shown in Figure 3.3. The example consists of three basic blocks in which the compiler expects control flow to be sequential through the blocks. Furthermore, load and div instructions are assumed to be potentially excepting. The code segment after scheduling is shown in Figure 3.4. Speculative instructions are denoted by (S). With sentinel scheduling, the scheduler ensures that there is a non-speculative instruction to check the exception tag of each PEI in the PEI's home block. For example, I<sub>8</sub> checks if an exception occurred for I<sub>6</sub>. In order to protect the source operands, the lifetimes of all source operands for speculative instructions are extended to the non-speculative checking instruction. For example, the lifetimes of v4 and v7 (source operands of I<sub>6</sub>) are extended to I<sub>8</sub>. Also, the scheduler must not schedule any instructions

<sup>&</sup>lt;sup>1</sup>An exception condition for I<sub>6</sub> will mark an exception in v6. I<sub>7</sub> will propagate the exception to its destination, v8, since it is also a speculative instruction. Finally, the use of v8 by I<sub>8</sub> will detect the exception condition.

| -        | <b>.</b> | .•          |            | Current | Speculation | Home  |

|----------|----------|-------------|------------|---------|-------------|-------|

| <u> </u> | Instru   | ction       |            | Block   | Distance    | Block |

| 6        | div      | v6,v4,v7    | <b>(S)</b> | 0       | 1           | 1     |

| 1        | add      | v3,v2,v4    |            | 0       | 0           | 0     |

| 7        | add      | v8,v0,v6    | <b>(S)</b> | 0       | 1           | 1     |

| 2        | add      | v1,v2,4     |            | 0       | 0           | 0     |

| 9        | load     | v9,mem(v8)  | (S)        | 0       | 2           | 2     |

| 4        | load     | v5,mem(v1)  | <b>(S)</b> | 0       | 1           | 1     |

| 10       | add      | v10,v9,4    | <b>(S)</b> | 0       | 2           | 2     |

| 3        | beq      | v1,0,L1     |            | 0       | 0           | 0     |

| 5        | store    | mem(v5),v2  |            | 1       | 0           | 1     |

| 8        | bne      | v8,v2,L2    |            | 1       | 0           | 1     |

| 11       | store    | mem(v10),v2 |            | 2       | 0           | 2     |

| 12       | mov      | v9,v10      |            | 2       | 0           | 2     |

Figure 3.4 Code segment after sentinel scheduling, before register allocation.

which overwrite a speculative instruction's source operands. Therefore, the destination of  $I_{10}$  must be renamed to v10 to prevent v9 from being overwritten. The code segment after register allocation is shown in Figure 3.5. In this example, a total of 10 physical registers are required to ensure exception detection and recovery are possible for all speculative instructions.

# 3.4 Scheduling in the IMPACT Compiler

The instruction scheduler used in the IMPACT compiler performs both local and global instruction scheduling. Local scheduling is performed on basic blocks and permits some limited reordering of instructions as well as filling of branch delay slots [36]. While the benefits of this level of scheduling may be adequate for single-issue microprocessors, it has been shown to be inadequate when using non-numeric benchmarks for wide-issue processors [1, 2, 7]. This occurs because there are typically few instructions in basic blocks and only a small number of independent computation chains. In order to gain greater optimization and scheduling freedom,

| _ |    | <b>.</b> . | .•         |            | Current | Speculation | Home  |

|---|----|------------|------------|------------|---------|-------------|-------|

|   | L  | Instruc    | tion       |            | Block   | Distance    | Block |

| 6 | 5  | div        | r9,r2,r6   | <b>(S)</b> | 0       | 1           | 1     |

| 1 | 1  | add        | r5,r4,r2   |            | 0       | 0           | 0     |

| 7 | 7  | add        | r7,r0,r9   | <b>(S)</b> | 0       | 1           | 1     |

| 2 | 2  | add        | r3,r4,4    |            | 0       | 0           | 0     |

| 9 | )  | load       | r8,mem(r7) | (S)        | 0       | 2           | 2     |

| 4 | 1  | load       | r1,mem(r3) | <b>(S)</b> | 0       | 1           | 1     |

| 1 | 10 | add        | r9,r8,4    | <b>(S)</b> | 0       | 2           | 2     |

| 3 | 3  | beq        | r3,0,L1    |            | 0       | 0           | 0     |

|   |    |            |            |            |         |             |       |

| 5 | 5  | store      | mem(r1),r4 |            | 1       | 0           | 1     |

| 8 | 3  | bne        | r7,r4,L2   |            | 1       | 0           | 1     |

|   |    |            |            |            |         |             |       |

| 1 | 11 | store      | mem(r9),r4 |            | 2       | 0           | 2     |

| 1 | 12 | mov        | r8,r9      |            | 2       | 0           | 2     |

Figure 3.5 Code segment after sentinel scheduling and register allocation.

superblocks were developed to permit optimization and scheduling of multiple basic blocks with similar execution paths together [4]. Section 3.4.2 will describe the scheduling heuristics used in the impact scheduler. Section 3.4.3 will provide experimental results showing the benefits of the IMPACT instruction scheduler.

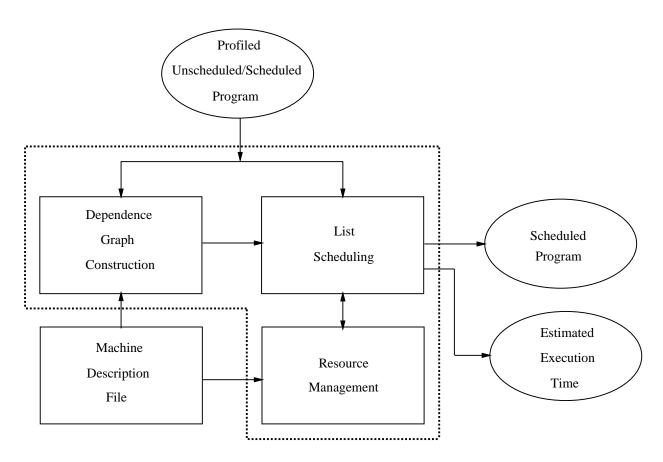

#### 3.4.1 Overview of the IMPACT Scheduler

Acyclic scheduling is accomplished by performing two passes over each basic block or superblock. The first pass, pre-pass scheduling, is performed prior to register allocation. As such, the scheduler has the greatest scheduling freedom since no artificial data dependences resulting from processor register constraints have been created. The second pass, post-pass scheduling, is performed after register allocation. This pass is used to resolve any scheduling changes that may occur resulting from the insertion of spill code, as well as caller and callee save code required to allocate the virtual registers to the physical registers. This pass is also used to fill branch delay slots [36].

Figure 3.6 Organization of the IMPACT Instruction Scheduler.