# ARCHITECTURAL AND SOFTWARE SUPPORT FOR EXECUTING NUMERICAL APPLICATIONS ON HIGH PERFORMANCE COMPUTERS

#### BY

#### SADUN ANIK

B.S., Middle East Technical University, 1986 M.S., University of Illinois at Urbana-Champaign, 1990

#### THESIS

Submitted in partial fulfillment of the requirements for the degree of Doctor of Philosophy in Electrical Engineering in the Graduate College of the University of Illinois at Urbana-Champaign, 1993

Urbana, Illinois

#### ABSTRACT

Numerical applications require large amounts of computing power. Although shared memory multiprocessors provide a cost-effective platform for parallel execution of numerical programs, parallel processing has not delivered the expected performance on these machines. There are two crucial steps in parallel execution of numerical applications:

(1) effective parallelization of an application and (2) efficient execution of the parallel program on a multiprocessor. This thesis addresses the second step within the scope of automatically parallelized FORTRAN programs.

In this thesis, the mismatch between the needs of parallelized FORTRAN programs and the support for parallel execution in shared memory multiprocessors is identified as a cause of poor performance. The thesis addresses this problem from two angles, architectural and software support for parallel execution and compiler transformation to enhance program characteristics. Architectural features and synchronization and scheduling algorithms are studied to increase the efficiency of support for parallel execution. It is shown that architectures supporting atomic fetch&add primitives and synchronization busses can execute parallel programs more effectively. New algorithms for lock access and parallel task scheduling are proposed.

The thesis also explores compiler transformations which can modify parallel program characteristics to increase the parallel execution efficiency of less sophisticated architectures. It is shown that by using blocking transformations on nested parallel loops, program characteristics can be modified to decrease the need for scheduling and synchronization operations. This results in an increase in the efficiency of parallel execution, especially for multiprocessors with simplistic support for interprocessor synchronization.

#### ACKNOWLEDGEMENTS

First, I would like to thank my advisor, Professor Wen-mei Hwu, for his time, guidance and patience. I consider myself very lucky to have worked with him. My respect for him goes beyond the teacher-student relationship. I will always remember him.

I would like to thank my parents for their love and support. Without them, graduate school would have been an unbearable journey. They were always there when I needed them and I will always feel their unconditional love.

I am grateful to all my friends for the good times. Tom Conte, has been a true friend for all these years we spent together. I am thankful to Steve Turner. If it weren't for him, I would not know the joy of skiing in the Rockies. I also thank Bob Janssens for being a true friend, patient and understanding.

Finally I would like to thank Marianne Holma for being my friend through the final years of graduate school. I would like to express my appreciation for everything she did for me and everything she was to me.

## TABLE OF CONTENTS

|    |                                                                                                                                                                                                                                                                                        | Page                                               |

|----|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------|

| 1. | INTRODUCTION  1.1 Shared Memory Multiprocessors and Parallel Processing 1.2 Performance of Parallel Programs  1.3 Synchronization Needs of Parallel FORTRAN Programs  1.3.1 Synchronization needs  1.3.2 Locks and hardware synchronization primitives  1.4 Dynamic and Static Methods | 1<br>3<br>5<br>8<br>10<br>17<br>21                 |

| 2. | INSTRUMENTATION AND SIMULATION METHODS                                                                                                                                                                                                                                                 | 23<br>24<br>27                                     |

| 3. | SYNCHRONIZATION SUPPORT FOR PARALLEL LOOP EXECUTION  3.1 Analysis of Iteration Scheduling Overhead                                                                                                                                                                                     | 31<br>32<br>35<br>37<br>38<br>39<br>41<br>43<br>49 |

| 4. | AN EFFICIENT TASK SCHEDULING ALGORITHM                                                                                                                                                                                                                                                 | 51<br>54<br>62<br>65                               |

| 5. | COMPILER TRANSFORMATIONS FOR LOOP BLOCKING  | 67  |

|----|---------------------------------------------|-----|

|    | 5.1 Blocking Transformations                | 70  |

|    | 5.1.1 Partitioning an iteration space       | 72  |

|    | 5.1.2 Legality of a blocking transformation | 74  |

|    | 5.2 Loop Bounds Generation                  | 76  |

|    | 5.3 Experimental Results                    | 81  |

|    | 5.4 Concluding Remarks                      | 91  |

| 6. | CONCLUSIONS                                 | 93  |

|    | REFERENCES                                  | 98  |

|    | VITA                                        | 102 |

# LIST OF TABLES

| Γable             |                                                            | $Pag\epsilon$ |

|-------------------|------------------------------------------------------------|---------------|

| 1.1: Granularity  | and parallelism in parallel benchmarks                     | 21            |

| 2.1: Timing assu  | imptions without contention                                | 29            |

| 2.2: Assumption   | ns for memory traffic                                      | 30            |

| 3.1: The use of a | architectural support and lock algorithms in experiments . | 47            |

| 4.1: Execution r  | models for nested parallel loops                           | 56            |

## LIST OF FIGURES

| Figure |                                                                      | Page |

|--------|----------------------------------------------------------------------|------|

| 1.1:   | A DOALL loop                                                         | 9    |

| 1.2:   | A DOACROSS loop                                                      | 10   |

| 1.3:   | Producer algorithm for task scheduling                               | 12   |

| 1.4:   | Consumer algorithm for task scheduling                               | 12   |

| 1.5:   | Self-scheduling algorithm for loop iterations                        | 14   |

| 1.6:   | Barrier synchronization algorithm                                    | 15   |

| 1.7:   | Algorithm for Advance/Await operations                               | 16   |

| 1.8:   | Queuing lock algorithm for lock accesses                             | 19   |

| 1.9:   | Test&test&set algorithm for lock accesses                            | 20   |

| 2.1:   | Multiprocessor trace example                                         | 26   |

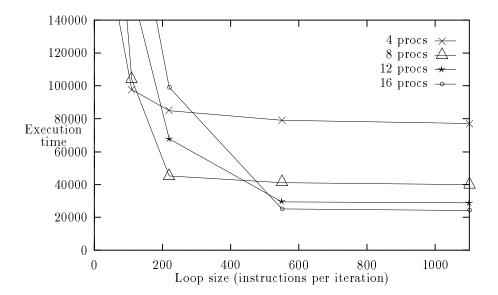

| 3.1:   | Execution time vs. granularity for test&set primitive                | 36   |

| 3.2:   | Execution time vs. number of iterations for test&set primitive       | 37   |

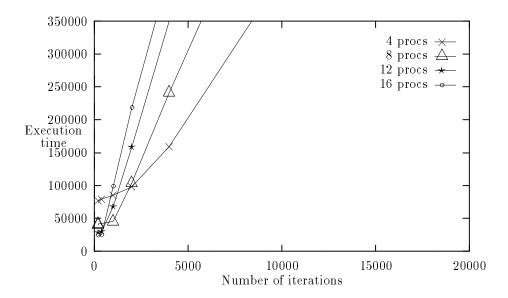

| 3.3:   | Iteration scheduling overhead vs. number of processors               | 39   |

| 3.4:   | Speedup and scheduling overhead for BDNA with 16 processors          | 44   |

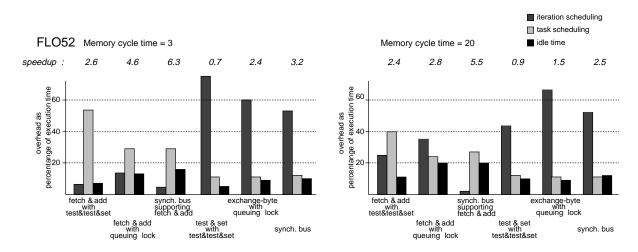

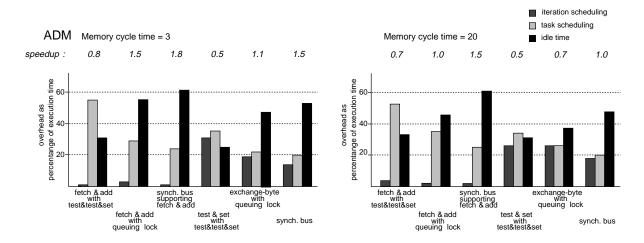

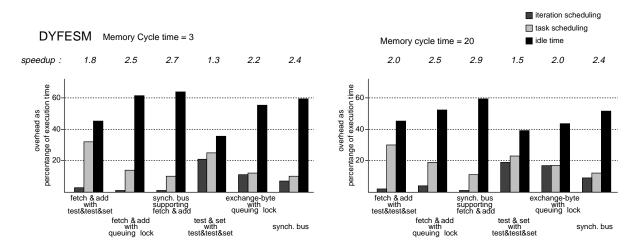

| 3.5:   | Speedup and scheduling overhead for FLO52 with 16 processors         | 45   |

| 3.6:   | Speedup and scheduling overhead for ADM with 16 processors           | 45   |

| 3.7:   | Speedup and scheduling overhead for DYFESM with 16 processors        | 46   |

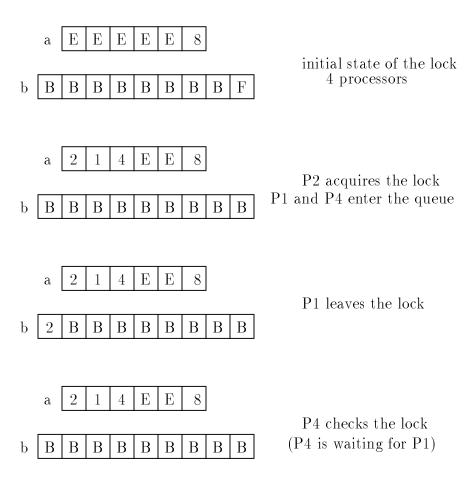

| 4.1:   | Nonblocking queuing lock algorithm with $fetch\&add$ primitive       | 58   |

| 4.2:   | Operation of nonblocking queuing lock                                | 59   |

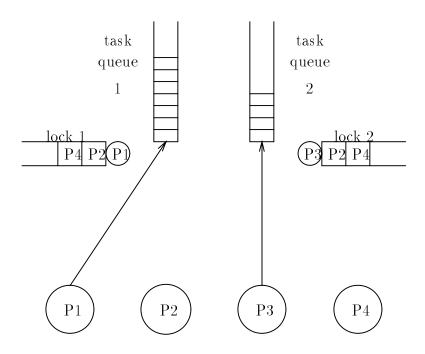

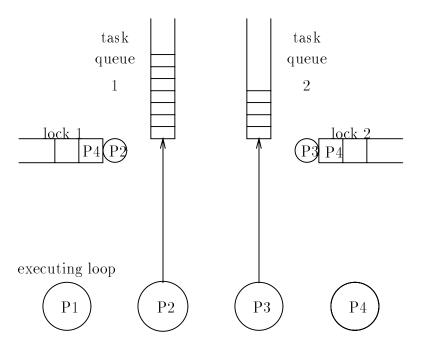

| 4.3:   | Snapshot in task distribution (a)                                    | 60   |

| 4.4:   | Snapshot in task distribution (b)                                    | 61   |

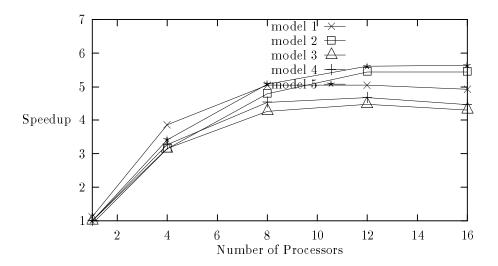

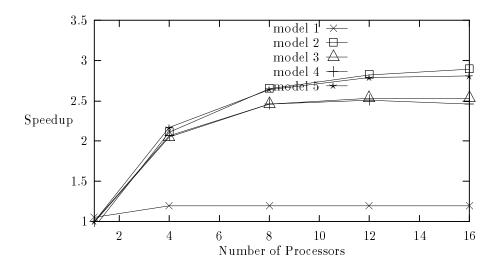

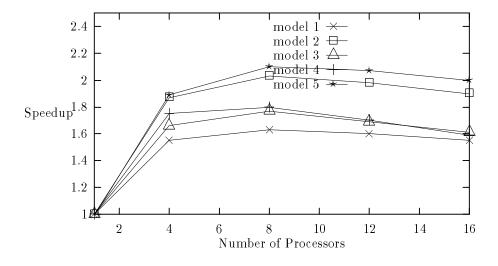

| 4.5:   | Speedup of FLO52 program for different execution models              | 63   |

| 4.6:   | Speedup of DYFESM program for different execution models             | 64   |

| 4.7:   | Speedup of ADM program for different execution models                | 64   |

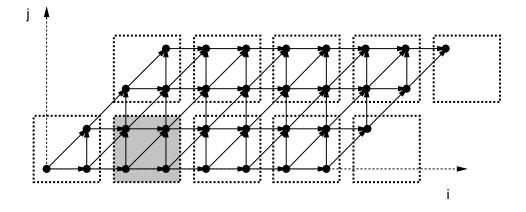

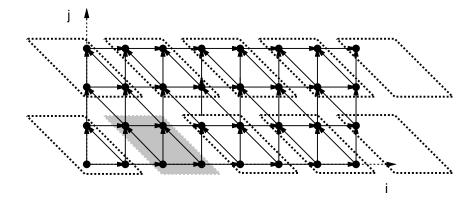

| 5.1:   | Iteration space and dependences of a loop-nest                       | 69   |

| 5.2:   | Same loop-nest after skewing and blocking                            | 69   |

| 5.3:   | Same loop-nest with nonrectangular blocking                          | 70   |

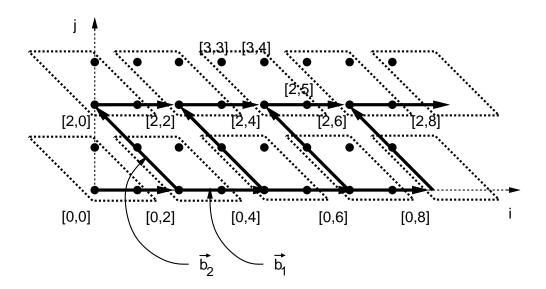

| 5.4:   | The illustration of blocking vectors for the loop-nest in Figure 5.3 | 72   |

| 5.5:  | A two-level nested DOALL loop                                          | 82 |

|-------|------------------------------------------------------------------------|----|

| 5.6:  | Nested DOALL loop after blocking transformation                        | 82 |

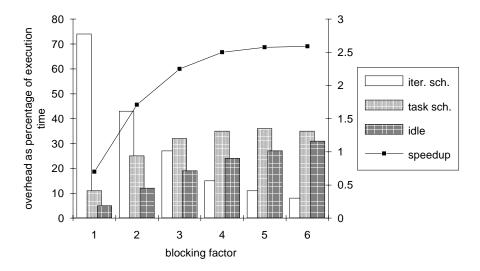

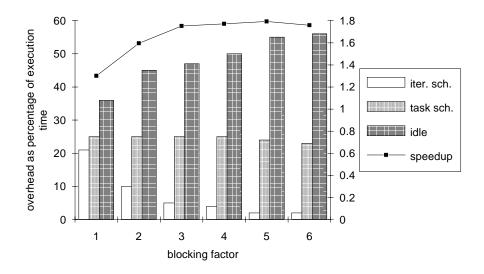

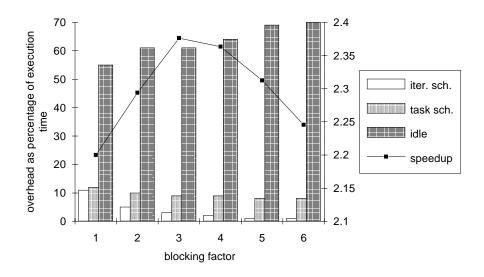

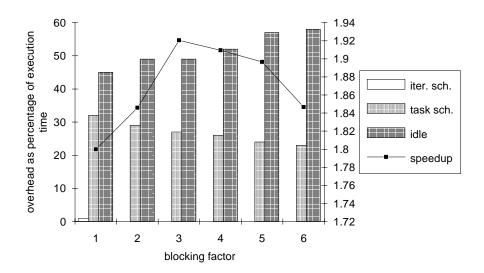

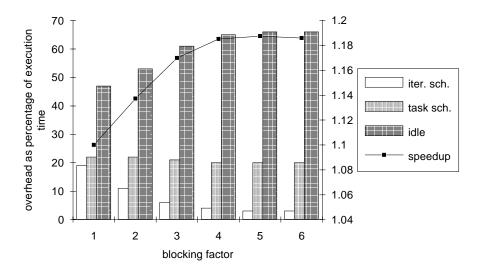

| 5.7:  | Performance of FLO52 for 16 processors and test@set primitive          | 83 |

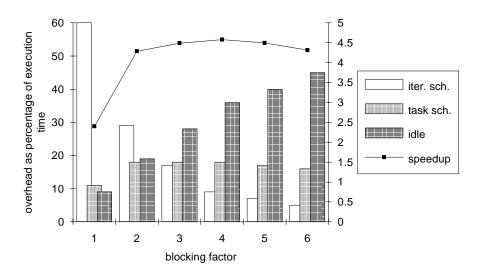

| 5.8:  | Performance of FLO52 for 16 processors and exchange-byte primitive     | 84 |

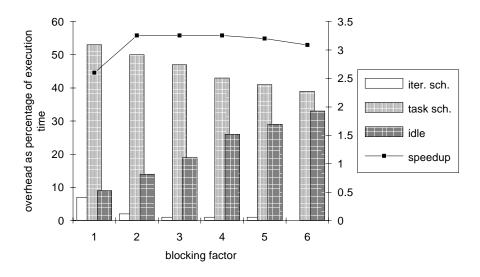

| 5.9:  | Performance of FLO52 for 16 processors and $fetch@add$ primitive       | 84 |

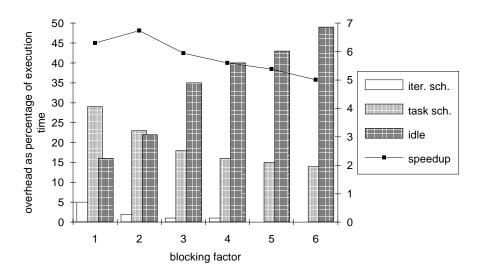

| 5.10: | Performance of FLO52 for 16 processors and synchronization bus         | 85 |

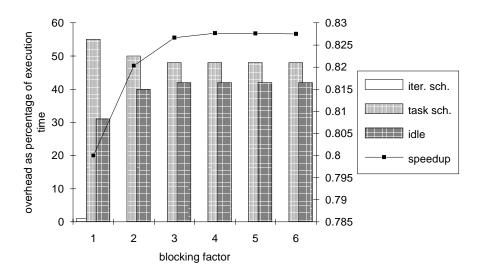

| 5.11: | Performance of DYFESM for 16 processors and test&set primitive         | 87 |

| 5.12: | Performance of DYFESM for 16 processors and exchange-byte primitive    | 87 |

| 5.13: | Performance of DYFESM for 16 processors and $fetch \& add$ primitive . | 88 |

| 5.14: | Performance of DYFESM for 16 processors and synchronization bus .      | 88 |

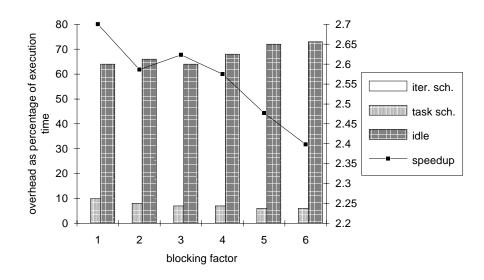

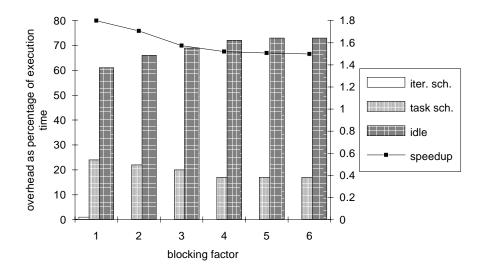

| 5.15: | Performance of ADM for 16 processors and test&set primitive            | 89 |

| 5.16: | Performance of ADM for 16 processors and exchange-byte primitive .     | 89 |

| 5.17: | Performance of ADM for 16 processors and $fetch \& add$ primitive      | 90 |

| 5.18: | Performance of ADM for 16 processors and synchronization bus           | 90 |

#### 1. INTRODUCTION

Bus-based shared memory multiprocessors have provided a cost-effective platform for parallel processing for more than a decade. However, utilization of these platforms for efficient parallel processing has not been easy. Large scientific applications written in FORTRAN have been the early candidates for parallel execution on shared memory multiprocessors. Scientific programs have relatively simple control structures. The data structures used in these programs have regular structure and predictable access patterns. However, achieving significant speedups with parallel execution of these programs has been an elusive goal. Most of the performance improvements for these programs resulted from tedious hand parallelization and tuning of the program. As this thesis establishes, the inefficiencies in parallel program execution result from a mismatch between the available compiler technology for parallelizing and restructuring programs, and the architectural and run-time support for parallel program execution in shared memory multiprocessors.

This thesis has two purposes. The first is to identify the performance bottlenecks in compiling and running a parallel scientific application. The second is to develop run-time and compile-time methods to increase the efficiency in parallel program execution. The organization of this thesis is follows. This chapter provides the background information on the procedures for compilation and parallel execution of FORTRAN programs. The issues in executing a parallel FORTRAN program on a shared memory multiprocessor are discussed. The need for run-time support for parallel execution is treated in a systematic manner. Existing algorithms for the synchronization and scheduling problems are presented at the level of architectural primitives, synchronization algorithms such as lock/unlock operations, and scheduling algorithms.

Chapter 2 describes the simulation tools developed for studying the performance issues in parallel program execution. A new technique is used to simulate the performance of several architecture/algorithm combinations. The developed tool combines trace-driven simulation of individual processors in a multiprocessor with the emulation of interprocessor communication to obtain accurate timing information.

Chapter 3 presents a discussion of issues in parallel program execution and experimental evaluation of the interaction between architectural support and algorithms used by the run-time system. Two important program characteristics are identified as having direct influence on program performance. The task granularity of a program (the amount of computation within a parallel task) affects the performance of the task scheduling algorithm. For a program in which task granularity is small, the performance of the program

can be limited by the rate at which tasks are distributed to available processors. The loop granularity of a parallel loop (the amount of computation within a sequential iteration of a loop) affects the performance of the iteration scheduling algorithm.

Chapter 4 presents a new task scheduling algorithm to increase the efficiency of scheduling a parallel task. It is shown that the proposed algorithm can increase the utilization of processors in a shared memory multiprocessor. A nonblocking queuing lock algorithm is also introduced in this chapter which satisfies the functional requirements of the proposed scheduling algorithm.

Chapter 5 addresses the issue of loop granularity and the use of compiler transformations to increase the size of sequential threads of execution. This chapter provides a formal treatment of loop blocking transformations and describes a prototype implementation within the IMPACT compiler.

Finally, Chapter 6 includes the concluding remarks.

#### 1.1 Shared Memory Multiprocessors and Parallel Processing

In executing a parallel program, scheduling computation to processors and synchronizing the processors introduce an overhead. The way this overhead affects the performance of a parallel program depends on both the program characteristics and the run-time system/architecture combination. As the units of computation become larger, the scheduling operations are needed less frequently, hence the effect of scheduling overhead decreases. The application programs used as benchmarks are parallelized scientific

FORTRAN programs taken from the Perfect Club benchmark set [1]. In a previous study of synchronization behavior of parallel programs, Davis and Hennessy used the combination of a shared memory architecture and large-grain parallel applications programmed with message passing paradigm, and concluded that synchronization does not introduce significant overhead [2]. The characteristics of parallel FORTRAN programs are very different from those programs using message passing paradigm. In these programs the basic form of parallelism is the parallel loop structure [3]. The parallel FORTRAN dialect used in this work is Cedar FORTRAN (CF) which has two basic parallel loop structures, DOALL and DOACROSS [4]. There is no dependence between iterations of a DOALL loop; therefore, the iterations can be executed in arbitrary order. A DOACROSS loop can have a dependence relation between iterations. The execution order of iterations of a DOACROSS loop has to preserve the dependencies.

The run-time system performs four basic duties in the execution of parallel loops:

- 1. Task scheduling. When a processor executes a DOALL/DOACROSS statement in a CF program, the parallel loop corresponding to that statement is ready to be executed. Starting the execution of this loop in parallel requires the notification of all of the available processors in the system through a task scheduling algorithm.

- 2. Iteration scheduling. All of the iterations of a parallel loop are distributed to the processors in a balanced way by an *iteration scheduling* algorithm.

- Advance/Await operations. The data dependencies across iterations in a DOACROSS loop are enforced by Advance/Await operations.

4. Barrier synchronization. When all of the iterations of a parallel loop are executed, the processors participating in the execution synchronize at a barrier.

In the existing systems, the run-time system is integrated with the application by the compiler in the form of libraries [5],[6],[7].

## 1.2 Performance of Parallel Programs

Automatically parallelized numerical programs represent an important class of parallel applications in high performance multiprocessors. These programs are used to solve problems in many engineering and science disciplines such as Civil Engineering, Mechanical Engineering, Electrical Engineering, Chemistry, Physics, and Life Sciences. As parallel architectures became available, parallelizing FORTRAN compilers have been developed for commercial and experimental multiprocessor systems to support these applications [4],[5],[6],[7],[8]. However the sustained performance of parallel systems for real-world applications fall short of the promise of these systems.

Synchronization overhead has been recognized as an important source of performance degradation in the execution of parallel programs. Many hardware and software techniques have been proposed to reduce the synchronization cost in multiprocessor systems [9],[10],[11],[12],[13],[14],[15]. Instead of proposing new synchronization techniques, this thesis addresses two simple questions: (1) How much does architecture support for synchronization affect the performance of automatically parallelized numerical programs? (2) What can be done to improve the performance of parallel programs?

To answer these questions, we start with analyzing the needs for synchronization in parallelized FORTRAN programs. Due to the mechanical nature of parallelizing compilers, parallelism is expressed in only a few structured forms. This parallel programming style allows us to systematically cover all of the synchronization needs in automatically parallelized programs. Synchronization issues arise in task scheduling, iteration scheduling, barriers and data dependence handling. A set of algorithms is presented which use lock()/unlock() and increment() operations. We then identify how several hardware synchronization primitives can be used to implement these generic synchronization operations. The synchronization primitives considered are test&set, fetch&add, exchange-byte, and lock/unlock operations. Since these primitives differ in functionality, the algorithms for synchronization in parallel programs are implemented with varying efficiency.

Beckmann and Polychronopoulos studied the effects of the barrier synchronization and iteration scheduling overhead on parallel loops in the presence of a synchronization bus [16]. Polychronopoulos also demonstrated that run-time overhead can limit the performance gain in executing parallel loops [17]. Arenstorf and Jordan modeled the execution overhead for several barrier synchronization algorithms [18]. The developed models provide an insight to the problem but to be able to choose the right combination of algorithms and architectural support, quantification of parameters is necessary.

The analysis of iteration scheduling overhead illustrates the need for quantification.

Using the self-scheduling algorithm, iterations of a parallel loop are scheduled to the processors one at a time. Furthermore, self-scheduling is a sequential algorithm in which

only one processor can schedule an iteration at a given time. Consider the execution of a loop with N iterations on P processors. For simplicity, it is assumed that all iterations of a loop are identical and each takes  $t_{it}$  time to execute. Furthermore let  $t_{sch}$  be the time it takes to schedule an iteration. In the case in which

$$t_{it} < (P-1) \times t_{sch}$$

the time it takes for a processor to execute a loop iteration is shorter than the the time needed by the remaining P-1 processors to schedule their iterations. In this situation, the processor completing execution of an iteration has to wait for the other processors to complete iteration scheduling operations in order to schedule a new iteration. When iteration scheduling becomes the bottleneck, the execution time is

$$t_{total} = N \times t_{sch} + t_{it}$$

.

For the case in which

$$t_{it} > (P-1) \times t_{sch}$$

sequential iteration scheduling operations do not form the critical path of execution.

Then the execution time can be written as

$$t_{total} = ((t_{sch} + t_{it}) \times \lceil N/P \rceil).$$

The important difference between the two cases is that in the first case increasing the number of processors does not decrease the execution time, and in the latter case the execution time is inversely proportional to the number of processors. A more detailed analysis of iteration scheduling overhead is presented in Section 3.1.

Of the two parameters,  $t_{it}$  depends on the granularity of loops in the application and  $t_{sch}$  is determined by the underlying architecture and synchronization primitives. Two variations of self-scheduling, chunk-scheduling and guided self-scheduling [19], increase the effective granularity by scheduling multiple iterations at a time. Their effectiveness relies on the assumption that  $N \gg P$ .

#### 1.3 Synchronization Needs of Parallel FORTRAN Programs

The application programs used in this study are selected from the Perfect Club benchmark set [1]. The Perfect Club is a collection of numerical programs for benchmarking supercomputers. The programs were written in FORTRAN. For the experimental work, the programs were parallelized by the KAP/Cedar source-to-source parallelizer [20],[4] which generates a parallel FORTRAN dialect, Cedar FORTRAN. This process exploits parallelism at the loop level, which has been shown by Chen, Su, and Yew to capture most of the available parallelism for Perfect Club benchmark set programs [3]. They measured the instruction-level parallelism by trace-based data flow analysis and concluded that parallel loop structures sufficiently exploit this parallelism. However this assumes that all memory and control dependences can be resolved in the parallelization process. In practice, compile-time analysis of dependences may not be successful due to indirect array indexing requiring run-time dependence resolution. Also, limited interprocedural data-flow analysis can result in dependence equations with unknown variables resulting in conservative dependence analysis.

```

DOALL 30 J=1,J1

X(II1+J) = X(II1+J) * SC1

Y(II1+J) = Y(II1+J) * SC1

Z(II1+J) = Z(II1+J) * SC1

30 CONTINUE

```

Figure 1.1: A DOALL loop

Cedar FORTRAN has two major constructs to express loop-level parallelism: DOALL loops and DOACROSS loops. A DOALL loop is a parallel DO loop in which there is no dependence between the iterations. The iterations can be executed in parallel in arbitrary order. Figure 1.1 shows an example of a DOALL loop.

In a DOACROSS loop [21], there is a dependence relation across the iterations. A DOACROSS loop has the restriction that iteration i can depend on iterations j only where j < i. Because of this property, a simple iteration scheduling algorithm can guarantee deadlock free allocation of DOACROSS loop iterations to processors. In Cedar FORTRAN, dependences between loop iterations are enforced by Advance/Await synchronization statements [5]. An example of a DOACROSS loop is shown in Figure 1.2. The first argument of Advance and Await statements is the identifier for the synchronization variable to be used. The second argument of an Await statement is the data dependence distance in terms of iterations. In this example, when iteration i is executing this Await statement, it is waiting for iteration i-3 to execute its Advance statement. The third argument of Await is used to enforce sequential consistency in Cedar architecture [4]. The third argument implies that upon the completion of synchronization, the

value of X(I-3) should be read from shared memory. Similarly, the second argument of Advance statement implies that writing the value X(I) to shared memory should be completed before Advance statement is executed.

```

DOACROSS 40 I=4,IL

:

AWAIT(1, 3, X(I-3))

X(I) = Y(I) + X(I-3)

ADVANCE (1, X(I))

:

30 CONTINUE

```

Figure 1.2: A DOACROSS loop

#### 1.3.1 Synchronization needs

In executing parallel FORTRAN programs, the need for synchronization arises in four contexts: task scheduling, iteration scheduling, barrier synchronization, and Advance/Await. In this section, we discuss the nature of these synchronization needs.

Task scheduling is used to start the execution of a parallel loop on multiple processors. All processors to participate in the execution of a parallel loop, or task, must be informed that the loop is available for execution. In this study, all experiments assume a task scheduling algorithm that uses a centralized task queue to assign tasks to processors. In Chapter 4, alternatives to this approach are considered. The processor which executes a DOALL or DOACROSS statement places the loop descriptor into the task queue. All idle processors acquire the loop descriptor from the task queue and start executing the

loop iterations. The accesses to the task queue by the processors are mutually exclusive.

A lock is used to enforce mutual exclusion.

Use of a centralized task queue serializes the task scheduling. A number of distributed task scheduling algorithms have been proposed in the past, Anderson, Lazowska, and Levy [22] compared the performance of several distributed algorithms in the context of thread managers. Most distributed task scheduling algorithms rely on a large supply of parallel tasks to maintain load balance. Also, they usually assume that each task needs to be executed by only one processor. These are valid assumptions for thread managers because there are usually a large number of tasks (threads) in the applications considered by this study and each task represents a piece of sequential code. These assumptions, however, are not valid for the current generation of automatically parallelized FORTRAN programs in which parallelism is typically exploited at only one or two loop nest levels. Since all parallel iterations of a single loop nest level form a task, there is typically only a very small number of tasks in the task queue. Also, multiple processors have to acquire the same task so that they can work on different iterations of the parallel loop. This increases the complexity of the task scheduling algorithm considerably [23]. This lack of task-level parallelism makes it difficult to effectively use distributed task queues.

Figures 1.3 and 1.4 show the task scheduling algorithms for the processor which executes a parallel DO statement and for the idle processors, respectively. The removal of the loop descriptor from the task queue is performed by the first processor entering the barrier associated with the loop.

```

put_task() {

new_loop->number_of_processors = 0 ;

new_loop->number_of_iterations = number of iterations in loop;

new_loop->barrier_counter = 0 ;

new_loop->iteration_counter = 0 ;

lock(task_queue) ;

insert_task_queue(new_loop) ;

task_queue_status = NOT_EMPTY ;

unlock(task_queue) ;

}

```

Figure 1.3: Producer algorithm for task scheduling

Figure 1.4: Consumer algorithm for task scheduling

The implementation of the lock(), unlock(), and increment() functions with different primitives is presented in the next section. By definition, the lock() and unlock() operations are atomic. Whenever underlined in an algorithm, the increment() operation is also assumed to be atomic and can be implemented with a sequence of lock, read-increment-write, and unlock operations. However, it is shown in Chapter 3 that the frequent use of atomic increment in parallel FORTRAN programs makes it necessary to implement atomic increment with efficient hardware support.

During the execution of a parallel loop, each iteration is assigned to a processor, which is called iteration scheduling. The self-scheduling algorithm [24] is used to implement iteration scheduling. In this method, the self-scheduling code is embedded within the loop body. Each time a processor is ready to execute a loop iteration, it executes the embedded scheduling code to acquire a unique iteration number. The self-scheduling algorithm shown in Figure 1.5 is an example of the code executed at the beginning of each loop iteration. The algorithm performs an atomic increment operation on a shared counter. Unless the multiprocessor supports an atomic fetch&add operation, a lock is required to enforce mutual exclusion in accessing the shared counter.

Two alternative dynamic iteration scheduling algorithms, chunk scheduling and guided self-scheduling (GSS), have been proposed to avoid the potential bottleneck of scheduling the iterations one at a time [19]. When the number of iterations in a parallel loop is much larger than the number of processors, such algorithms reduce the iteration scheduling overhead by assigning multiple iterations to each processor per iteration scheduling operation. This increases the effective granularity of parallel loops. The issues of granularity and scheduling overhead are discussed in Section 3.1. Both of these algorithms are proposed for DOALL loops. In the presence of dependences across iterations, i.e. DOACROSS loops, scheduling more than one iteration at a time may sequentialize the execution of a parallel loop. Therefore, algorithms such as chunk scheduling and GSS are applicable only to DOALL loops.

```

schedule_iteration() {

last_iteration = increment(current_loop->iteration_counter);

if (last_iteration >= current_loop->number_of_iterations) {

barrier synchronization;

}

else {

execute (last_iteration + 1) th iteration of loop;

}

}

```

Figure 1.5: Self-scheduling algorithm for loop iterations

After all iterations of a loop have been executed, processors synchronize at a barrier. A nonblocking linear barrier algorithm which is implemented with a shared counter (see Figure 1.6) can be used for high performance barrier synchronization. After all iterations of a parallel loop have been executed, each processor reads and increments the barrier counter associated with the loop. The last processor to increment the counter completes the execution of the barrier. As in the case of iteration self-scheduling, unless the multiprocessor system supports an atomic fetch@add operation, the mutually exclusive accesses to the shared counter are enforced by a lock.

The barrier algorithm shown in Figure 1.6 specifies that the first processor to enter the barrier removes the completed loop from the task queue. Using this barrier synchronization algorithm, the processors entering the barrier do not wait for the barrier exit signal. Therefore, a processor entering the barrier can immediately start executing another parallel loop whose descriptor is in the task queue. In contrast to the compile time scheduling of "fuzzy barrier" [14], this algorithm allows dynamic scheduling of loops

```

barrier_synchronization() {

if (current_loop->barrier_counter == 0) {

lock(task_queue) ;

if (current_loop == read_task_queue_head()) {

delete_task_queue_head() ;

if (task_queue_empty() == TRUE) task_queue_status = EMPTY ;

}

unlock(task_queue) ;

}

if (increment(current_loop->barrier_counter) == current_loop->number_of_processors - 1) {

resume executing program from the end of this loop ;

}

else read_task() ;

}

```

Figure 1.6: Barrier synchronization algorithm

to the processors in a barrier. The linear barrier is a sequential algorithm, and for the case in which this algorithm proves to be a sequential bottleneck, a parallel algorithm (e.g., Butterfly barrier [15]) can be used. The experimental data presented in Chapter 3 illustrate that barrier synchronization execution is not a significant source of overhead. The last processor to enter the barrier executes the *continuation* of the parallel loop — the code in the sequential FORTRAN program that is executed after all iterations of the current loop are completed. By using a semaphore, the processor which executed the corresponding DOALL/DOACROSS statement can be made to wait for the barrier exit to execute the continuation of the loop.

The combination of task scheduling, iteration self-scheduling and nonblocking barrier synchronization algorithms presented in this section allows deadlock-free execution of

```

initialization(synch_pt) {

for (i = 1 ; i < number_of_iterations ; i++) V[synch_pt][i] = 0 ;

}

advance(synch_pt) {

V[synch_pt][iteration_number] = 1 ;

}

await(synch_pt, dependence_distance) {

if(iteration_number <= dependence_distance) return() ;

else while (V[synch_pt][iteration_number - dependence_distance] == 0) ;

}</pre>

```

Figure 1.7: Algorithm for Advance/Await operations

nested parallel loops with the restriction that DOACROSS loops appear only at the deepest nesting level [24].

The last type of synchronization, Advance/Await, can be implemented by using a bit vector for each synchronization point. In executing a DOACROSS loop, iteration i, waiting for iteration j to reach synchronization point synch\_pt, busy waits on location V[synch\_pt][j]. Upon reaching point synch\_pt, iteration j sets location V[synch\_pt][j]. This implementation, as shown in Figure 1.7, uses regular memory read and write operations, thus does not require atomic synchronization primitives. This implementation assumes a sequentially consistent memory system. In the case of weak

ordering memory systems, an Await statement can be executed only after the previous memory write operations complete execution. For a multiprocessor with software-controlled cache coherency protocol, Cedar FORTRAN Advance/Await statements include the list of variables whose values should be written to/read from shared memory before/after their execution. The implementation details of these statements under weak ordering memory system models or software-controlled cache coherency protocols are beyond the scope of this thesis.

In the HEP multiprocessor system, an alternative approach for enforcing data dependences across iterations was taken [25]. The use of full/empty bits that are associated with every data item provides a very efficient data synchronization mechanism in the execution of DOACROSS loops.

#### 1.3.2 Locks and hardware synchronization primitives

In executing numeric parallel programs, locks are frequently used in synchronization and scheduling operations. In the task scheduling algorithm (See Figures 1.3 and 1.4), the use of a lock enforces mutual exclusion in accessing the task queue. Locks are also used to ensure correct modification of shared counters when there is no atomic fetch@add primitive in the architecture. Such shared counters are used by both iteration scheduling (See Figure 1.5) and barrier synchronization (See Figure 1.6).

There are several algorithms that implement locks in cache coherent multiprocessors using hardware synchronization primitives [12],[13]. Virtually all existing multiprocessor

architectures provide some type of hardware support for atomic synchronization operations. In theory, any synchronization primitive can be used to satisfy the synchronization needs of a parallel program. In practice, however, different primitives may result in very different performance levels. For example, a queuing lock algorithm [12],[13] can be implemented efficiently with an exchange-byte or a fetch&add primitive, whereas a test&set implementation may be less efficient. This section outlines the lock algorithms that are chosen for each hardware synchronization primitive considered in the experiments.

Exchange-byte. The exchange-byte version of the queuing lock algorithm is shown in Figure 1.8. In this implementation, the exchange-byte primitive is used to construct a logical queue of processors that contend for a lock. The variable  $my_id$  is set at the start of the program so that its value for the *i*th processor is  $2 \times i$ , where processors are numbered from 0 to P-1. During the execution, the value of  $my_id$  alternates between  $2 \times i$  and  $2 \times i + 1$ . This eliminates the race condition between two processors competing for a lock which has just been released by one of them. The variable queue\_tail holds the ID of the last processor which tried to acquire this lock. A processor which tries to acquire the lock receives the ID of its preceding processor via queue\_tail. It then writes its own ID into the variable queue\_tail. This algorithm constructs a queue of processors waiting for a lock where each processor waits specifically for its predecessor to release the lock. By mapping the elements of synchronization vector flags[] to disjoint cache lines, the memory accesses in the while loop of this algorithm can be confined to individual

```

initialization() {

flags[2P] = FREE;

flags[0...2P-1] = BUSY;

queue_tail = 2P;

}

lock() {

my_id = my_id XOR 1;

queue_last = exchange-byte(my_id, queue_tail);

while(flags[queue_last] == BUSY);

flags[queue_last] = BUSY;

}

unlock() {

flags[my_id] = FREE;

}

```

Figure 1.8: Queuing lock algorithm for lock accesses

caches of processors. When a processor releases the lock, only the cache line read by its successor has to be invalidated.

Test&set. Because of its limited functionality, test & set cannot be used to construct processor queues in a single atomic operation. Therefore, in this study, whenever the architecture offers only test & set, a plain test & test & set algorithm (see Figure 1.9) is used to implement all lock operations.<sup>1</sup>

Fetch&add. Due to the emphasis on atomic increment operations in iteration scheduling and barrier synchronization, supporting a fetch&add primitive in hardware can significantly decrease the need for lock accesses in these algorithms. When the fetch&add

<sup>&</sup>lt;sup>1</sup>However, it should be pointed out that in an environment where critical sections of algorithms involve many instructions and memory accesses, a *test&set* implementation of a queuing lock may enhance performance.

```

lock() {

while(lock == BUSY || test&set(lock) == BUSY) ;

}

unlock() {

lock = CLEAR ;

}

```

Figure 1.9: Test&test&set algorithm for lock accesses

primitive is supported by a system, a fetch&add implementation of the test&test&set algorithm can be used to support the lock accesses in task scheduling as well as a queuing lock algorithm. The performance implications of supporting the fetch&add primitive will be presented in Sections 3.1 and 3.3.

Synchronization bus. In the Alliant FX/8 multiprocessor, a separate synchronization bus and a Concurrency Control Unit are provided [5] which can improve parallel program performance by reducing the latency of both fetch & add operations and lock accesses. Such a bus provides the processors with a coherent set of shared counters and lock variables that can be accessed and updated in a single cycle. In this study, the case in which a synchronization bus is used to implement synchronization operations is also considered.

The cost performance trade-offs in synchronization support can be determined only by evaluating the performance implications of different schemes for real parallel applications. The needs for synchronization and scheduling support depend on the application characteristics such as granularity of loop iterations and structure of parallelism in the

Table 1.1: Granularity and parallelism in parallel benchmarks

| program | average number | average number of          |

|---------|----------------|----------------------------|

| name    | of iterations  | instructions per iteration |

| BDNA    | 450            | 515                        |

| FLO52   | 58             | 39                         |

| ADM     | 11             | 48                         |

| DYFESM  | 14             | 112                        |

application. These issues are addressed by the experiments reported in Sections 3.2 and 3.3.

#### 1.4 Dynamic and Static Methods

In general the performance improvements from parallel program execution change with both the application program characteristics and with the system support for parallel execution. In automatically parallelized FORTRAN programs, the amount of parallelism and its granularity are limited by the parallelization technology of the compiler. The existing technology limits the scope of parallelization to leaf functions and a few levels of innermost loops. The most significant effect of this is the granularity of parallelism. Table 1.1 shows the available parallelism and granularity for the innermost parallel loops in several automatically parallelized Perfect Club programs. In the presence of nested parallel loops, it is observed that the number of iterations of outer parallel loops did not differ from that of the innermost parallel loops. Both the limited parallelism and the rather small number of instructions in parallel loops suggest that a combination of both

architectural support and good synchronization and scheduling algorithms are needed for efficient execution of these programs.

#### 2. INSTRUMENTATION AND SIMULATION METHODS

Simulation-based performance evaluation of parallel systems presents unique challenges. In this thesis the execution of a parallel program on a shared memory multiprocessor is simulated using a hybrid method. The execution of a program has two parts. The first is the program execution local to a processor. For this part, the well-studied techniques for single-processor systems such as trace-driven simulation can be used. The second part comprises the sections of a program in which two or more processors interact through resources such as shared memory, memory bus, and synchronization bus. Such interaction can be both explicit, through the use of synchronization operations, and implicit, cache misses, etc.

In this thesis an integrated simulation/emulation model is used to model the execution of a parallel program on a shared memory multiprocessor. The behavior of the parallel program that is local to a processor is not dependent on the number of processors in the system. Therefore, this behavior can be captured into a trace collected from the execution of the program on a single processor. On the other hand, the interaction

among multiple processors on a system is dependent on the number of processors in the system and the particulars of the underlying architecture. It is not possible to reliably capture the processor interaction through software instrumentation. Instrumentation of a parallel program slows down the execution significantly; hence, the generated timing information is distorted. In general, processor interaction relies on asynchronous events, and the execution time of algorithms is a nonlinear function of the number of processors executing them and the existing system load. Therefore, it is not possible to compensate for the distortion in the timing information in a collected trace by using postprocessing techniques.

On the other hand, the timing information concerning interprocessor communication can be captured by emulating the execution of the program segments which require interprocessor interaction. Emulating interprocessor communication both increases the accuracy of collected information and also makes it possible to evaluate new architectural features to enhance interprocessor communication efficiency.

### 2.1 Experimental Method

Trace-driven simulation is used in the experiments to evaluate the performance implications of architecture support for synchronization. In the simulation model, a parallel FORTRAN program consists of a collection of sequential program segments called task pieces. To execute task pieces in parallel, several types of events arise: execution of DOALL and DOACROSS statements, execution of parallel loop iterations, barriers

synchronization, and execution of Advance/Await statements. Each trace used in the simulations is a record of events that take place during the execution of a parallel program and detailed information about instructions executed between pairs of events.

Figure 2.1 shows the trace for a DOALL loop with three iterations. The lines in the trace starting with I denote the task pieces. Each line corresponds to the execution of a sequential portion of the application and contain the number of lines of code executed, and the number of read and write accesses to shared data. The line F indicates execution of a DOALL statement and the line J the end of the DOALL loop. The B-E pairs identify the beginning and end of iterations of the parallel loop respectively. The plain trace in the figure shows that after the execution of 10 sequential lines of the application, a DOALL statement is executed. The loop has three iterations, each executing 24 lines. After the execution of the parallel loop, 4 more lines are executed corresponding to the last I line of the trace.

It can be seen from this example that whenever iterations of a parallel loop execute the same number of instructions, there is redundancy in the trace concerning this loop. The execution of the loop can be summarized by providing the execution characteristics of a single iteration and providing the total number of iterations. The summarized trace is shown in Figure 2.1 for which the F line is replaced by M and the number of iterations. A parallel loop where the loop body does not contain any control flow instructions can be identified at the time of instrumentation as a candidate for summarized tracing. The

| Plain                                                                   | Summarized                                   | Descriptions                                                                                                                                                                                                                                                                                                                           |

|-------------------------------------------------------------------------|----------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Plain  I 10 2 3 F B I 24 14 6 E B I 24 14 6 E B I 24 14 6 E B I 24 14 6 | I 10 2 3<br>M 3<br>I 24 14 6<br>J<br>I 4 0 4 | $Descriptions$ F: Start of parallel loop (Fork) J: End of parallel loop (Join) B: Beginning of an iteration E: End of an iteration M $p_1$ : Similar to F (summarized) $p_1$ : Number of iterations I $p_1p_2p_3$ : Block of instructions $p_1$ : # of source code lines $p_2$ : # of shared data reads $p_2$ : # of shared data reads |

| J<br>I 4 0 4                                                            |                                              |                                                                                                                                                                                                                                                                                                                                        |

Figure 2.1: Multiprocessor trace example

compression of the trace from such loops results in the overall compression of the trace in excess of 1:100, hence making off-line storing of the execution trace possible.

In this study, traces are collected by instrumenting the source code of parallelized applications. In a trace, each event is identified by its type and arguments, e.g., the synchronization point and the iteration number for an Await event. Each task piece is annotated with the number of dynamic instructions executed in the task piece and the dynamic count of shared memory accesses. These numbers are collected with the help of pixie, an instruction-level instrumentation tool for the MIPS architecture [26]. Using a RISC processor model similar to the MIPS R2000, in which instruction execution times are defined by the architecture, the time to execute instructions in the CPU and local cache can be calculated directly from the dynamic instruction count. On the other hand,

the time to service the cache misses and the atomic accesses to the shared memory depends on the activities of other processors in the system. Therefore, a multiprocessor simulator is used to calculate the program execution time of the task pieces and an architectural level emulator is used to dynamically calculate the execution time of events. To assess the performance implications of synchronization primitives, a library of scheduling and synchronization routines as described in Section 1.3 is included in the simulator.

#### 2.2 Architectural Model

In the simulation model, the processor memory interconnect is a split transaction or decoupled access bus, in which a memory access requested by a processor occupies the bus only when its request and response are transmitted between the processor and the memory modules. The bus is made available to other transactions while the memory modules process an access. When the memory modules have long access latency, the split transaction bus in addition to memory interleaving allows the multiple accesses to be overlapped. In the experiments, we assume that shared memory is 8-way interleaved. Two memory module cycle times are used: 3 and 20 processor cycles. The 3-cycle memory module cycle time is chosen to represent the situation in which slow processors are used in low-cost multiprocessor systems. The 20-cycle latency represents the case in which fast processors are used in high performance multiprocessor systems.

In the experiments, the atomic operations test & set, exchange-byte and fetch & add are performed in the memory modules rather than through the cache coherence protocol.

Whenever a memory location is accessed by one of these synchronization primitives, the location is invalidated from the caches. The read-modify-write operation specified by the primitive is then carried out by the controller of the memory module that contains the accessed location. Note that this memory location may be brought into cache later by normal memory accesses made to that location due to spin waiting. This combination of atomic operation implementation in memory modules, the cache coherence protocol, and the split transaction bus is similar to that of the Encore Multimax 300 series multiprocessors [6]. Section 3.2 presents the characteristics of the application programs that lead to the choice of performing the read-modify-write in memory modules rather than through the cache coherence protocol.

Without any memory or bus contention, a synchronization primitive takes one cycle to invalidate local cache, one cycle to transmit request via the memory bus, two memory module cycles to perform the read-modify-write operation, and one cycle to transmit response via the memory bus. This translates into 9 and 43 cycles for the two memory module latencies, respectively. A memory access that misses from cache takes one cycle to detect the miss, one cycle to transmit a cache refill request via the bus, one memory module cycle time to access the first word in the missing block, and four clock cycles to transmit the four words back to cache via the memory bus. This amounts to 9 and 26 cycles for the assumed memory module latencies. Note that the latency for executing synchronization primitives and refilling caches increases considerably in the presence of

Table 2.1: Timing assumptions without contention

| primitive                         | latency   |

|-----------------------------------|-----------|

| test&set                          | 3 + 2 * M |

| exchange-byte                     | 3 + 2 * M |

| fetch&add                         | 3 + 2 * M |

| cache miss                        | 6+M       |

| lock/unlock (synchronization bus) | 1         |

| fetch&add (synchronization bus)   | 1         |

bus and memory contention. This effect is accounted for in the simulations on a cycleby-cycle basis.

To evaluate the effectiveness of a synchronization bus, a single-cycle access synchronization bus model is used. The synchronization bus provides single-cycle lock/unlock operations on shared lock variables and single cycle fetch&add operations on shared counters. In the presence of conflicts, i.e., multiple requests in the same cycle, requests are served in round-robin fashion. A summary of the timing assumptions for synchronization primitives is shown in Table 2.1.

In all the simulations, an invalidation-based write-back cache coherence scheme is used. The shared memory traffic contributed by the application is modeled based on the measured instruction count and frequency of shared data accesses. Table 2.2 lists the assumptions used to simulate the memory traffic for the task pieces. It is assumed that 20% of the instructions executed are memory references. In addition, it is measured that 6-8% of all instructions (approximately 35% of all memory references) are to shared data. It is assumed that references to shared data cause the majority of cache misses

Table 2.2: Assumptions for memory traffic

| parameter                      | value |

|--------------------------------|-------|

| memory/instruction ratio       | 0.20  |

| shared data cache miss rate    | 0.80  |

| nonshared data cache miss rate | 0.05  |

(80% shared data cache miss rate and 5% nonshared data cache miss rate). When the experiments are repeated by lowering the shared cache miss rate to 40%, the speedup figures reported in Chapter 3 change by less than 2%.

#### 3. SYNCHRONIZATION SUPPORT FOR PARALLEL LOOP EXECUTION

This chapter presents an analysis and experimental evaluation of synchronization overhead on shared memory multiprocessors. Section 3.1 provides the analysis of iteration scheduling overhead and its effect on program execution time. This section also provides experimental data on architecture specific parameters in the formulations. The presented data provide a comparison of basic synchronization and scheduling operations across architectures supporting different synchronization mechanisms.

Section 3.2 describes the important characteristics of the benchmark programs used in the experiments and the behavior of lock algorithms used for mutual exclusion in scheduling algorithms.

Section 3.3 provides an experimental evaluation of the relation between architectural support for synchronization and parallel program performance. The results presented identify the contribution of iteration and task scheduling algorithms as well the available

parallelism to the overall program performance. The presented data explore two systems with different memory access latencies.

Finally Section 3.4 includes the concluding remarks for this section.

### 3.1 Analysis of Iteration Scheduling Overhead

In the execution of a parallel loop, the effect of iteration scheduling overhead on performance depends on the number of processors, the total number of iterations, and the size of each iteration. This section first presents the expressions for speedup in executing parallel loops in which the loop iterations are large (coarse granularity) and where the loops iterations are small (fine granularity). These expressions provide insight into how iteration scheduling overhead influences loop execution time and will be used to analyze the simulation results later in this section. A more general treatment of program granularity and run-time overhead can be found in [27].

Consider a DOALL loop with N iterations where each iteration takes  $t_l$  time to execute without parallel processing overhead. For a given synchronization primitive and lock algorithm, let  $t_{sch}$  be the time it takes for a processor to schedule an iteration. This section will look at the impact of scheduling overhead for two cases. For the first case it is assumed that when a processor is scheduling an iteration, it is the only processor doing so.

For a given P and  $t_{sch}$ , the necessary condition for this case is

$$t_l > (P-1) \times t_{sch}$$

and the time to execute the loop with P processors can be written as

$$t_P = ((t_{sch} + t_l) \times \lceil N/P \rceil) + t_{oh},$$

where  $t_{oh}$  is the total task scheduling and barrier synchronization overhead per processor. Since the task scheduling and barrier synchronization overhead depend only on the number of processors,  $t_{oh}$  is constant for a given P.

The execution time of the sequential version of this loop,  $t_{seq}$ , is  $t_l \times N$ . We define speedup for P processors as the ratio of  $t_{seq}$  to  $t_P$ . The speedup for a DOALL loop is

$$speedup = \frac{t_{seq}}{t_P}$$

$$= \frac{t_l N}{((t_{sch} + t_l) \times \lceil N/P \rceil) + t_{oh}}$$

$$\approx \frac{P}{\frac{t_{sch} + t_l}{t_l} + \frac{P \times t_{oh}}{N \times t_l}};$$

for  $N \gg P$ ,

$$speedup \approx P \times \frac{t_l}{t_{sch} + t_l};$$

using  $t_l > (P-1) \times t_{sch}$ ,

$$speedup > P \times \frac{t_l}{\frac{t_l}{P-1} + t_l}$$

$$> P \times \frac{P-1}{P}$$

$$> P-1.$$

Therefore, when  $t_l > (P-1) \times t_{sch}$ , the speedup increases linearly with the number of processors; hence the execution time depends only on P and the total amount of work in the loop,  $N \times t_l$ .

Now consider the case in which a processor completing the execution of an iteration always has to wait to schedule the next iteration because at least one other processor is scheduling an iteration at that time. The necessary condition for this case is

$$t_l < (P-1) \times t_{sch},$$

and the iteration scheduling overhead forms the critical path in determining the loop execution time. When iteration scheduling becomes the bottleneck, execution time is

$$t_P = N \times t_{sch} + t_l;$$

for  $N \gg P$ ,

$$t_P \approx N \times t_{sch}$$

.

When the iteration scheduling algorithm is implemented with lock operations, scheduling an iteration involves transferring the ownership of the lock from one processor to the next, and reading and incrementing the shared counter. Hence,

$$t_{sch} = t_{lock-transfer} + t_{update}$$

.

The remainder of this section first look at how loop execution time varies with loop granularity. Then the iteration scheduling overhead  $(t_{sch})$  is quantified for different hardware synchronization primitives by simulating execution of a parallel loop with very fine granularity.

# 3.1.1 Granularity effects

The analysis above shows the existence of two different types of behavior of execution time for a parallel loop. Given a multiprocessor system, the parameters P and  $t_{sch}$  do not change from one loop to another. Keeping these parameters constant, the granularity of a loop,  $t_l$ , determines whether or not scheduling overhead is significant in overall execution time.

The architectural support for synchronization primitives influences the execution time of parallel loop in two ways. On the one hand, different values of  $t_{sch}$  for different primitives result in different execution times when the loop iterations are small (i.e., fine granularity loops). On the other hand,  $t_{sch}$  determines whether a loop is of fine or coarse granularity. In this section the simulation results on the variation of loop execution times across different implementations of the iteration scheduling algorithm are presented. Since  $t_{sch}$  determines the execution time of fine-granularity loops, it is important to quantify how  $t_{sch}$  changes with synchronization primitives and the number of processors in the system.

Figure 3.1 shows the simulation results for execution time vs. the size of an iteration in a DOALL loop with the *test&set* primitive implementing *test&test&set* algorithm for lock accesses. Similar curves were obtained for other synchronization primitives and for a synchronization bus supporting atomic lock operations. The loop sizes are in terms of the number of instructions, and the execution time in terms of CPU cycles. In these

Figure 3.1: Execution time vs. granularity for test&set primitive

simulations, the total number of executed instructions in the loop is kept constant while the number of instructions in an iteration is changed.

Figure 3.1 shows that for 16 processors and using testEset primitive, there is a sharp increase in execution time when the iteration size is less than 550 instructions. The memory module cycle time is assumed to be 3 processor cycles. Similar plots for other primitives indicate that the critical iteration sizes are around 300 for exchange-byte and 200 for a synchronization bus. Using the fetchEadd primitive, the critical iteration size is around 100 instructions. As will be shown in Section 3.2, in the application programs used in these experiments, the iteration sizes of the parallel loops vary from 10 to 1000 instructions. This shows that the choice of synchronization primitives will influence the performance of some loops.

Figure 3.2: Execution time vs. number of iterations for test&set primitive

## 3.1.2 Scheduling overhead for fine-grain loops

For fine-grain loops, the loop execution time  $T_P$  is approximately  $N \times t_{sch}$ . The change of execution time with respect to the granularity of a set of synthetic loops is shown in Figure 3.2 for the test & set primitive implementing the test & test & set algorithm. Each of the synthetic loops has a total of 220000 executed instructions. Therefore, the region in which iteration size < 50 instructions corresponds to N > 4400 in these figures. The common observation from these figures is that when loop iterations are sufficiently small (N is sufficiently large), the execution time increases linearly with N. Also, when extrapolated,  $T_P$  vs. N lines go through the origin which validates the linear model

$$T_P = N \times t_{sch}$$

for execution time.

Figure 3.3 shows how scheduling overhead per iteration,  $t_{sch}$ , changes for the different synchronization primitives as the number of processors increases. Using the test & set primitive, the scheduling overhead increases with the number of processors. For the exchange-byte and fetch & add primitives and the synchronization bus, the scheduling overhead scales well. Furthermore,  $t_{sch}$  shows wide variation across primitives. For the 16-processor case, the average number of cycles to schedule a loop iteration is 98, 31, 17 and 7 for test& set, exchange-byte, synchronization bus, and fetch& add primitives, respectively.

The synchronization bus model used in these simulations has single-cycle access time for free locks and single-cycle lock transfer time. Therefore, the synchronization bus data show the highest performance achievable by hardware support for lock accesses alone. In Section 3.3, the performance figures are given for a synchronization bus which also supports single-cycle fetch&add operation. Such a synchronization bus is capable of scheduling a loop iteration every clock cycle. Therefore, its overall performance can be expected to be better than that of all of the primitives analyzed in this section.

#### 3.2 Synchronization Characteristics of Applications

In this section some synchronization characteristics of the application programs used in these experiments are reported. These characteristics help to focus the experiments and to analyze the experimental results. Section 3.2.1 presents the granularity of the

Figure 3.3: Iteration scheduling overhead vs. number of processors

parallel loops in these application programs. Section 3.2.2 discusses the lock access locality in the applications.

# 3.2.1 Parallelism characteristics of application programs

Experimental investigation of parallel processing requires realistic parallel programs. To support the experiments, a set of programs from the Perfect Club benchmark set are parallelized. The program KAP [20] was used as the primary parallelization tool. Using statement-level profiling (tcov), the frequently executed parts of the program were identified. If the parallelization of these parts was not satisfactory, the causes were investigated. In some cases, the unsatisfactory parallelization results were simply due to KAP's limitations in manipulating loop structures, e.g., too many instructions in loop

body or too many levels of nesting. In these cases, the important loops were parallelized manually.

Among all of the programs thus parallelized, four show a relatively high degree of parallelism, i.e., at least 60% of the computation was done in the parallel loops. These four programs are ADM, BDNA, DYFESM, and FLO52. The program ADM is a three-dimensional code which simulates pollutant concentration and deposition patterns in a lakeshore environment by solving a complete system of hydrodynamic equations. The BDNA code performs molecular dynamic simulations of biomolecules in water. The DYFESM code is a two-dimensional, dynamic, finite-element code for the analysis of symmetric anisotropic structures. The FLO52 code analyses the transonic inviscid flow past an airfoil by solving unsteady Euler equations.

To perform experiments with these four programs, instrumentation code is inserted in the programs and their traces are collected. An in-depth treatment of automatic parallelization and the available parallelism in the Perfect Club programs can be found in [28],[29].

Table 1.1 on page 22 shows the available parallelism and granularity for the innermost parallel loops in the four automatically parallelized programs. In three of the four programs, FLO52, ADM, and DYFESM, the parallelism was exploited in the form of nested DOALL loops. For the BDNA program, the parallel loops were not nested, and two-thirds of the dynamic parallel loops were DOACROSS loops with dependence distances of one iteration.

For nested parallel loops, the number of iterations of outer loops does not differ from that of innermost parallel loops. Therefore, the number of iterations of parallel loops cannot be increased with techniques such as parallelizing outer loops or loop interchange. The small number of loop iterations suggests that chunk scheduling and guided self-scheduling cannot be used to improve performance significantly beyond self-scheduling. The small number of instructions in each iteration suggests that architectural support is needed to execute these programs efficiently.

### 3.2.2 Locality of lock accesses in synchronization algorithms

In these simulations, all four programs exhibited very low locality for lock accesses. When a processor acquires a lock, it is considered a *lock hit* if the processor is also the one that last released the lock. Otherwise, the lock acquisition results in a *lock miss*. The measured lock hit rate for the four programs with four or more processors was less than 0.2%. Such a low lock access locality can be explained by the dynamic behavior of scheduling and synchronization algorithms.

For each parallel loop, every processor acquires the task queue lock and barrier lock only once. This results in a round-robin style of accesses to these locks. For each parallel loop, the loop counter lock used in the loop self-scheduling algorithm is accessed multiple times by each processor. However, a lock hit can occur only when the processor which most recently acquired an iteration finishes the execution of that iteration before the

completion of all of the previously scheduled iterations. Due to low variation in the size of iterations of a parallel loop, this scenario is unlikely.

In the experiments, because of the low lock hit rate, the atomic memory operations are implemented in shared memory. An implementation of atomic operations via the cache coherence protocol would result in excessive invalidation traffic and would also increase the latency of atomic operations. On the other hand, algorithms such as test&test&set require spinning on memory locations which are modified by atomic operations. Therefore, all memory locations are cached with an invalidation-based write-back cache coherence scheme. This simple scheme effectively uses cache to eliminate excessive memory traffic due to spinning while it efficiently executes atomic synchronization primitive in memory modules. For example, while waiting for a busy lock, the test loop of a test&test&set algorithm brings the data corresponding to the lock value into the cache. As long as the processor owning the lock does not release it, the test loops of other processors are confined to their local caches. When the lock is released by its owner with a write operation to the lock data structure, the copies of the lock data structure in the other processors caches are invalidated. In the next test cycle of the test&test&set algorithm, the memory accesses to the lock location result in a cache miss for each waiting processor. After fetching the new value of the freed lock location from memory, the test cycle terminates and the test&set operation is executed. The caching of lock data structure reduces the memory traffic during the test cycle.

# 3.3 Experimental Results

In this section the performance implications of synchronization primitives on four application programs are presented. The performance results are obtained by simulating a 16-processor system assuming centralized task scheduling, iteration self-scheduling, and linear nonblocking barrier synchronization. The system timing assumptions are the same as those summarized in Section 2.1. To calculate the speedup, the execution time for the sequential version of a program without any parallel processing overhead is used as the basis.

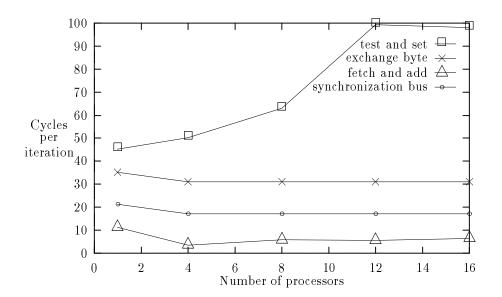

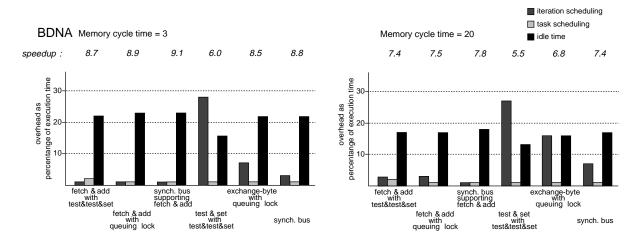

Figures 3.4–3.7 present the speedup obtained in the execution of these program together with three categories of parallel processing overhead: iteration scheduling, task scheduling, and idle time. Each figure shows the results for one benchmark in two graphs, one for 3-cycle memory modules and the other for 20-cycle memory modules. The horizontal axis lists the combinations of architectural support and lock algorithms used in the experiments; these combinations are described in Table 3.1. The combination of exchange-byte primitive with test&test&set algorithm is not included because this case has the same performance as the test&set with test&test&set combination.

The task scheduling overhead corresponds to the time the processors spent to acquire tasks from the task queue. The iteration scheduling overhead refers to the time the processors spent in the self-scheduling code to acquire iterations. The processor idle time is defined as the time spent by processors waiting for a task to be put into the empty task queue. According to this definition, a processor is idle only if the task queue is empty

Figure 3.4: Speedup and scheduling overhead for BDNA with 16 processors

when the processor completes its previously assigned task. This provides a measure of available parallelism in the parallelized programs.

Note that the three overhead numbers in Figures 3.4–3.7 for each combination do not add up to 100%. The major part of the difference is the time that is actually spent in the execution of the application code. In addition, there are three more categories of overhead that are measured but not shown because they are usually too small to report. They are due to task queue insertion, barrier synchronization, and Advance/Await synchronization. The time it takes for processors to insert tasks into the task queue is less than 2% of the execution time for all experiments. For all four benchmarks, the barrier synchronization overhead is also measured to be less than 2% of the execution time. Of the four benchmarks, we encounter a significant number of DOACROSS loops only in the BDNA program. The overhead for Advance and Await synchronization is about 11% of the execution time for 3-cycle memory modules and 18% for 20-cycle memory modules.

Figure 3.5: Speedup and scheduling overhead for FLO52 with 16 processors

Figure 3.6: Speedup and scheduling overhead for ADM with 16 processors

Figure 3.7: Speedup and scheduling overhead for DYFESM with 16 processors

In Figures 3.4-3.7, the three experiments on the left side of each graph correspond to the cases in which some form of fetch@add primitive is supported in hardware. For all four applications, when the fetch@add operation is not supported, the iteration scheduling overhead increased significantly. This increase in overhead has a direct impact on the performance of the applications. Furthermore, the performance of the fetch@add primitive with queuing lock algorithm (column 2) was at least as good as the performance of a synchronization bus supporting single-cycle atomic lock accesses(column 6). This is true even when the memory module cycle time is 20 processor cycles, which implies a minimal latency of 43 cycles to execute fetch@add. Therefore, implementing the fetch@add primitive in memory modules is as effective as providing a synchronization bus that supports one cycle lock/unlock operations.

For the BDNA program, task scheduling overhead is not significant for all experiments. As shown in Table 1.1, loops in BDNA have a large number of iterations and relatively large granularity, which results in infrequent invocation of the task scheduling

Table 3.1: The use of architectural support and lock algorithms in experiments

| architectural support<br>and lock algorithm | use in scheduling<br>and synchronization                                                                                                                                                                                                       |

|---------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| fetch&add with test&test&set                | Iteration scheduling and barrier synchronization algorithms use fetch&add for shared counter increments. Test&test&set algorithm based on fetch&add is used to access the task queue lock.                                                     |

| fetch&add with queuing lock                 | Iteration scheduling and barrier synchronization algorithms use fetch&add for shared counter increments. Queuing lock based on fetch&add is used to access the task queue lock.                                                                |

| synch. bus supporting<br>fetch&add          | Iteration scheduling and barrier synchronization algorithms use single-cycle fetch&add on synchronization bus for shared counter increments. Synchronization bus provides single-cycle lock operations to access the task queue lock.          |

| exchange-byte with queuing lock             | Queuing lock algorithm is used to access the locks associated with shared counters in iteration scheduling and barrier synchronization. It is also used to access the task queue lock.                                                         |

| test&set with test&test&set                 | Test&test&set algorithm is used to access the locks associated with the shared counters in iteration scheduling and barrier synchronization algorithms. It is also used to access the task queue lock.                                         |

| synch. bus                                  | Synchronization bus provides the single-cycle lock/unlock operations to access the locks associated with the shared counters in iteration scheduling and barrier synchronization algorithms. They are also used to access the task queue lock. |

algorithm. On the other hand, the remaining three programs have much less computation per parallel loop, and this is reflected in the significant task scheduling overhead in their performance. Even with a synchronization bus that implements single cycle lock/unlock and single cycle fetch&add (column 3), the task scheduling overhead is still significant (see Figures 3.5–3.7). Note also that in FLO52, the relative percentage of time spent in task scheduling is higher with fetch&add support. This increased importance of task scheduling overhead is due to a reduction in time spent in the iteration scheduling rather than an increase in time spent in task scheduling.