### SYSTEMATIC COMPUTER ARCHITECTURE PROTOTYPING

### BY

## THOMAS MARTIN CONTE

B.E.E., University of Delaware, 1986M.S., University of Illinois, 1988

### THESIS

Submitted in partial fulfillment of the requirements for the degree of Doctor of Philosophy in Electrical Engineering in the Graduate College of the University of Illinois at Urbana-Champaign, 1992

Urbana, Illinois

#### SYSTEMATIC COMPUTER ARCHITECTURE PROTOTYPING

Thomas Martin Conte, Ph.D.

Department of Electrical and Computer Engineering

University of Illinois at Urbana-Champaign, 1992

Wen-Mei W. Hwu, Advisor

The current design process for workstation systems is over-taxed due to the size and diversity of realistic workload models. This thesis advocates a method to improve the design process by synthesizing prototype architectures from workloads. Focus is placed on the processor and memory systems, although the overall philosophy is applicable to other workstation components as well. Prototyping of memory systems is performed using methods to evaluate multiple designs with one pass over the address trace. Statistical sampling of address traces is adapted from traditional cache simulation to improve the performance and trace-size range of the techniques. These methods are extended to account for performance penalties due to multiprogramming. Prototyping of superscalar processors is performed using new statistical sampling techniques in conjunction with two simulation algorithms. The resource usage in an unlimited-resource simulation is used to select processor resource needs, but is only applicable to fixed operation latencies. A more general solution based on simulated annealing is developed and demonstrated as a prototyping method. The interaction between prototypes is investigated via simulation of three common schemes for coupling the processor to the memory system: blocking on a cache miss, limited-blocking, and non-blocking. It is concluded that sufficient design options exist to justify the separate design of the processor and the memory.

# DEDICATION

$Dedicated\ in\ fond\ memory\ to\ my\ grandfathers:\ Amato\ Conte\ and\ Joseph\ Giovanni.$

#### ACKNOWLEDGEMENTS

I would like to thank my parents and sisters who have supported me with precious love and advice. My advisor, Professor Wen-mei W. Hwu, deserves special thanks for his guidance, insight and patience. I also thank the members of my committee who helped to shape both this work and this Ph.D. student. They are Professors W. Kent Fuchs, David J. Kuck, and Janak H. Patel. Thanks are also due to Professors Yale N. Patt and Edward S. Davidson of the University of Michigan who have supplied me with advice and encouragement.

Thanks go to my friends, of whom only a partial list is: Michael Chan, Chani, Gary Delp, Paul Domagala, Michael Golden, Marianne Holma, Bill Mangione-Smith, Jon Nadler, Isadora Parrini, Guru Parulkar, Brian Rogers, William Hsu, Eric Thayer, Robert Tomilson and Steve Turner. I would like to thank Sadun Anik and Scott Mahlke for many interesting discussions. I have had the pleasure of working in a research group composed of very bright people. Thanks to: Roger Bringmann, Pohua Chang, William Chen, Aloke Gupta, Grant Haab, Rick Hank, John Holm, Sabrina Hwu, Scott Mahlke, Nancy Warter and Tokuzo Kiyohara. Thanks also to Mrs. Thompson who helped me find the key.

# TABLE OF CONTENTS

|    |     |                                                         | Page          |

|----|-----|---------------------------------------------------------|---------------|

| 1. | INT | RODUCTION                                               | 1             |

| 1. | 1.1 | The Current Architectural Design Process                | $\frac{1}{2}$ |

|    | 1.2 | Systematic Computer Architecture Prototyping            | 3             |

|    |     | 1.2.1 The aims of computer architecture prototyping     | 3             |

|    |     | 1.2.2 The method of computer architecture prototyping   | 4             |

|    |     | 1.2.3 Further uses of computer architecture prototyping | 6             |

|    | 1.3 | Relation to Previous Work                               | 7             |

|    | 1.4 | Organization of Thesis                                  | 9             |

| 2. | BEN | CHMARKS AND INSTRUMENTATION METHODS                     | 11            |

|    | 2.1 | Collection of Traces of Benchmark Behavior              | 15            |

|    |     | 2.1.1 Address trace collection                          | 15            |

|    |     | 2.1.2 Instruction trace collection                      | 17            |

|    |     | 2.1.3 In-process trace generation                       | 19            |

|    |     | 2.1.4 Library code                                      | 20            |

| 3. | MEI | IORY SYSTEM PROTOTYPING                                 | 22            |

|    | 3.1 | Single-Pass Cache Simulation                            | 23            |

|    |     | 3.1.1 Recurrences and conflicts                         | 25            |

|    |     | 3.1.2 Reference streams and cache dimensions            | 27            |

|    |     | 3.1.3 Least-recently used (LRU) stack operation         | 28            |

|    |     | 3.1.4 Recurrence/conflict-based single-pass simulation  | 31            |

|    | 3.2 | Statistical Sampling of Address Traces                  | 35            |

|    |     | 3.2.1 Definition of sampling                            | 35            |

|    |     | 3.2.2 State repair techniques                           | 36            |

|    | 3.3 | Susceptibility of Programs to Context Switching         | 51            |

|    |     | 3.3.1 Types of context switching                        | 53            |

|    |     | 3.3.2 The components of multiprogramming conflicts      | 54            |

|    |     | 3.3.3   | Multiprogramming extensions to LRU stack operation                | on |       |   | <br>55  |

|----|-----|---------|-------------------------------------------------------------------|----|-------|---|---------|

|    | 3.4 | Empiri  | cal Results of Program Susceptibility                             | •  |       |   | <br>60  |

|    |     | 3.4.1   | The validity of the single-pass method                            |    |       |   | <br>61  |

|    |     | 3.4.2   | Involuntary context switching susceptibility                      |    |       |   | <br>63  |

|    |     | 3.4.3   | Voluntary context switching susceptibility                        |    |       |   | <br>66  |

|    |     | 3.4.4   | Dimensional conflict effects                                      | •  |       |   | <br>69  |

|    |     | 3.4.5   | Measurement of fraction of cache flush $(f_{CS})$                 | •  |       |   | <br>72  |

|    | 3.5 | Examp   | les of Memory System Prototyping                                  |    |       |   | <br>76  |

|    |     | 3.5.1   | Data cache prototypes                                             |    |       |   | <br>76  |

|    |     | 3.5.2   | Prototypes for multiprogramming environments                      |    |       |   | <br>81  |

|    | 3.6 | Summa   | ary of Memory System Prototyping                                  | •  |       |   | <br>84  |

| 4. | PRO | OCESSO  | R PROTOTYPING                                                     |    |       |   | <br>86  |

|    | 4.1 | Process | sor Design Considerations                                         |    |       |   | <br>87  |

|    |     | 4.1.1   | Classes of processors                                             | •  |       |   | <br>91  |

|    |     | 4.1.2   | Branch handling                                                   |    |       |   | 96      |

|    |     | 4.1.3   | Performance metrics                                               |    |       |   | <br>99  |

|    | 4.2 | Process | sor Simulation Algorithms                                         |    |       |   | 100     |

|    |     | 4.2.1   | Queue-based simulation algorithm                                  |    |       |   | <br>101 |

|    |     | 4.2.2   | Event-driven simulation algorithm                                 |    |       |   | 105     |

|    |     | 4.2.3   | Statistical sampling of instruction traces                        |    |       |   | 108     |

|    | 4.3 | A Prot  | otyping Approach to FOCO-Class Processor Design                   |    |       |   | 115     |

|    |     | 4.3.1   | Resource requirements                                             |    |       |   | <br>116 |

|    |     | 4.3.2   | Near-optimal processor configurations                             | •  |       |   | <br>127 |

|    | 4.4 | Summa   | ary of Processor Prototyping                                      |    |       |   | <br>133 |

| 5. | PRO |         | R/MEMORY INTERACTION                                              |    |       |   | 135     |

|    | 5.1 | Process | sor and Memory System Interfaces                                  |    |       |   | <br>135 |

|    |     | 5.1.1   | Blocking and limited-blocking cache designs                       |    |       |   | <br>137 |

|    |     | 5.1.2   | Non-blocking cache designs                                        |    |       |   | <br>138 |

|    |     | 5.1.3   | Performance metrics                                               | •  |       |   | <br>141 |

|    | 5.2 | Empiri  | cal Evidence of Processor/Memory Interaction                      | •  |       |   | <br>141 |

|    |     | 5.2.1   | Performance of $blocking$ scheme                                  |    |       |   | <br>143 |

|    |     | 5.2.2   | Performance of $\mathit{limited}\text{-}\mathit{blocking}$ scheme |    |       |   | <br>145 |

|    |     | 5.2.3   | Performance of $non-blocking$                                     |    |       |   | <br>152 |

|    | 5.3 | Summa   | ary of Processor/Memory Interaction                               | •  |       |   | <br>159 |

| 6. | CON | NCLUSI  | ONS                                                               |    | <br>• |   | <br>162 |

|    | RE. | FEREN   | CES                                                               |    |       | • | <br>166 |

|    | VIT | ^A      |                                                                   |    |       | _ | <br>171 |

# LIST OF TABLES

| Table |                                                                                             | Page |

|-------|---------------------------------------------------------------------------------------------|------|

| 2.1.  | Benchmark usage in International Symposium on Computer Architecture,                        |      |

| 2.1.  | 1984-1990                                                                                   | 13   |

| 2.2:  | The SPEC89 benchmark suite                                                                  | 14   |

| 2.3:  | Dynamic system call usage                                                                   | 20   |

| 3.1:  | Involuntary context switching susceptibility $(\Delta \rho)$ for caches $(31, -, \infty)$ . | 65   |

| 3.2:  | Voluntary context switching susceptibility vs. block size                                   | 69   |

| 3.3:  | Prototype data cache dimensions for criterion $\hat{\rho} = 0.10.$                          | 78   |

| 3.4:  | Prototype data cache dimensions for criterion $\hat{\rho} = 0.05$                           | 79   |

|       | Prototype data cache dimensions for criterion $\hat{\rho} = 0.01.$                          | 80   |

| 3.6:  | ,                                                                                           |      |

|       | ming parameters: $q = 0.0001$ and $f_{CS} = 1.0.$                                           | 82   |

| 3.7:  | Prototype data cache dimensions for criterion $\hat{\rho} = 0.05$ , multiprogram-           |      |

|       | ming parameters: $q = 0.0001$ and $f_{CS} = 1.0$                                            | 83   |

| 4.1:  | Function types                                                                              | 90   |

| 4.2:  | Canonical latency set                                                                       | 93   |

| 4.3:  | Processor classifications                                                                   | 95   |

| 4.4:  | Percentage of correctly predicted branches for the benchmarks                               | 98   |

|       | Processor performance metrics                                                               | 100  |

| 4.6:  | Operations on queues                                                                        | 101  |

| 4.7:  | RE(IPC) for gcc, doduc, and espresso, for $L_S = 10,000$ and $L_S = 20,000$ ,               |      |

|       | issue rates two, four and eight instructions per cycle                                      | 112  |

| 4.8:  | Function unit resource usage density functions (percentage) for doduc,                      |      |

|       | issue rate eight instructions per cycle, canonical latencies                                | 118  |

| 4.9:  | Function unit resource usage density functions (percentage) for gcc, issue                  |      |

|       | rate eight instructions per cycle, canonical latencies                                      | 118  |

| 4.10  | : IPC for function unit number selection criteria of $z=0.80,0.95,0.99$ and                 |      |

|       | unlimited resources $(z = 1.0)$                                                             | 120  |

| 4 11  | : Scheduling window size for selection criteria of $z = 0.80, 0.95$ , and 0.99.             | 122  |

| 4.12: | Processor resource requirements, issue rate of two instructions/cycle, $z = 0.80$                                                                                                                   |

|-------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 4.13: | Processor resource requirements, issue rate of two instructions/cycle,                                                                                                                              |

| 4.14: | z = 0.95 Processor resource requirements, issue rate of two instructions/cycle,                                                                                                                     |

| 4.15: | z = 0.99.                                                                                                                                                                                           |

| 4.16: | Processor resource requirements, issue rate of four instructions/cycle, $z=0.95.\ldots$                                                                                                             |

| 4.17: | Processor resource requirements, issue rate of four instructions/cycle, $z = 0.99.$                                                                                                                 |

| 4.18: | Processor resource requirements, issue rate of eight instructions/cycle, $z = 0.80$                                                                                                                 |

| 4.19: | Processor resource requirements, issue rate of eight instructions/cycle, $z = 0.95$                                                                                                                 |

| 4.20: | Processor resource requirements, issue rate of eight instructions/cycle, $z = 0.99$                                                                                                                 |

| 4.21: | Final prototype for processor for gcc, issue rate eight instructions per cycle (IPC = $2.21$ )                                                                                                      |

| 4.22: | Final prototype for processor for xlisp, issue rate eight instructions per cycle (IPC = $1.32$ )                                                                                                    |

| 5.1:  | IPC* (and percentage of perfect IPC) for blocking scheme, issue rates of two, four and eight instructions per cycle, data cache prototypes $\hat{\rho} = 0.05$ and $0.10$ , $T_{MISS} = 10$         |

| 5.2:  | IPC* (and percentage of perfect IPC) for blocking scheme, issue rates of two, four and eight instructions per cycle, data cache prototypes $\hat{\rho} = 0.05$ and $0.10$ , $T_{MISS} = 20$         |

| 5.3:  | IPC* (and percentage of perfect IPC) for limited-blocking scheme, issue rates of two, four and eight instructions per cycle, data cache prototypes $\hat{\rho} = 0.05$ and $0.10$ , $T_{MISS} = 10$ |

| 5.4:  | IPC* (and percentage of perfect IPC) for limited-blocking scheme, issue rates of two, four and eight instructions per cycle, data cache prototypes                                                  |

| 5.5:  | $\hat{\rho} = 0.05$ and $0.10$ , $T_{MISS} = 20$                                                                                                                                                    |

| 5.6:  | per cycle                                                                                                                                                                                           |

|       | per cycle                                                                                                                                                                                           |

| 5.7:  | IPC* (and percentage of perfect IPC) for non-blocking scheme, issue rates                     |     |

|-------|-----------------------------------------------------------------------------------------------|-----|

|       | of two, four and eight instructions per cycle, data cache prototypes $\hat{\rho} =$           |     |

|       | $0.05 \text{ and } 0.10, T_{MISS} = 10$                                                       | 153 |

| 5.8:  | IPC* (and percentage of perfect IPC) for non-blocking scheme, issue rates                     |     |

|       | of two, four and eight instructions per cycle, data cache prototypes $\hat{\rho} =$           |     |

|       | 0.05 and 0.10, $T_{MISS} = 20$                                                                | 153 |

| 5.9:  | Difference between prototype designs of perfect cache and non-blocking                        |     |

|       | scheme, $z = 0.99$ , $T_{MISS} = 10$ , $\hat{\rho} = 0.05$ , issue rate of eight instructions |     |

|       | per cycle                                                                                     | 155 |

| 5.10: | Difference between prototype designs of perfect cache and non-blocking                        |     |

|       | scheme, $z = 0.99$ , $T_{MISS} = 20$ , $\hat{\rho} = 0.05$ , issue rate of eight instructions |     |

|       | per cycle                                                                                     | 156 |

| 5.11: | Difference between prototype designs of perfect cache and non-blocking                        |     |

|       | scheme, $z = 0.99$ , $T_{MISS} = 10$ , $\hat{\rho} = 0.10$ , issue rate of eight instructions |     |

| - 10  | per cycle                                                                                     | 156 |

| 5.12: | Difference between prototype designs of perfect cache and non-blocking                        |     |

|       | scheme, $z = 0.99$ , $T_{MISS} = 20$ , $\hat{\rho} = 0.10$ , issue rate of eight instructions | 4   |

|       | per cycle                                                                                     | 157 |

# LIST OF FIGURES

| Figure |                                                                                   | Page |

|--------|-----------------------------------------------------------------------------------|------|

| 2.1:   | A typical memory hierarchy showing address usage                                  | 16   |

| 3.1:   | An example trace of addresses                                                     | 25   |

| 3.2:   | An example two-block direct-mapped cache behavior                                 | 26   |

| 3.3:   | An example of LRU stack operation                                                 | 28   |

| 3.4:   | The least-recently used management policy for a stack, $S_B(k)$ (adapted          |      |

|        | from Mattson et al.)                                                              | 30   |

| 3.5:   | The recurrence/conflict single-pass cache simulation algorithm                    | 32   |

| 3.6:   | Extension of the recurrence/conflict single-pass algorithm to sampling            |      |

|        | using fill-flush state repair                                                     | 38   |

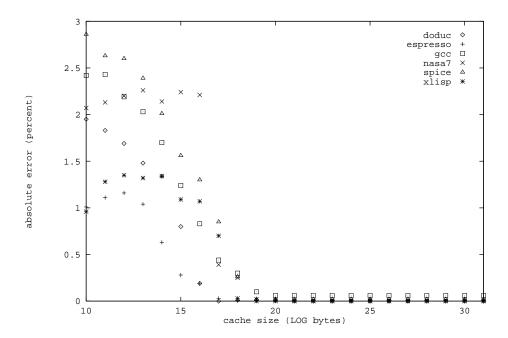

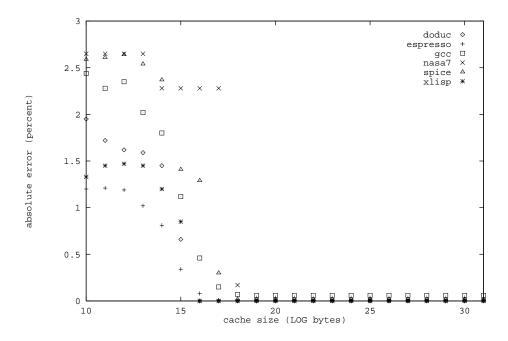

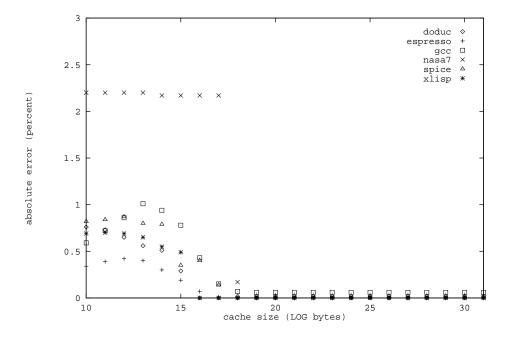

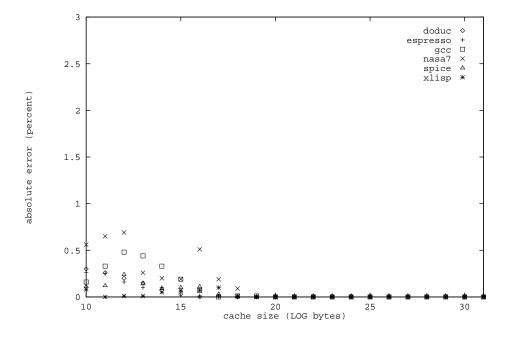

| 3.7:   | Absolute error for fill-flush, direct-mapped caches, $L_S = 50,000$               | 39   |

| 3.8:   | Absolute error for fill-flush, fully associative caches, $L_S = 50,000.$          | 39   |

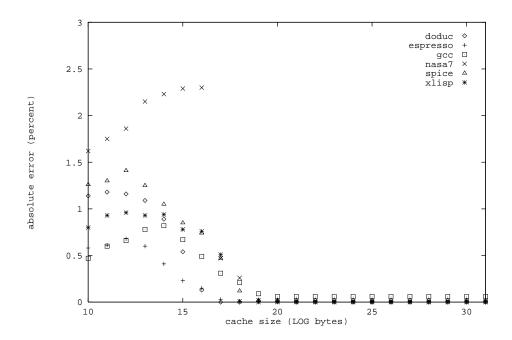

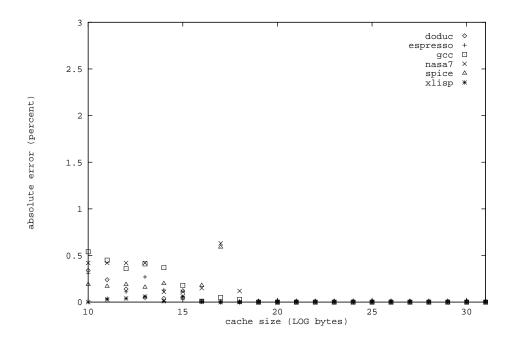

| 3.9:   | Absolute error for fill-flush, direct-mapped caches, $L_S=100,000.$               | 40   |

| 3.10   | : Absolute error for fill-flush, fully associative caches, $L_S=100,000$          | 40   |

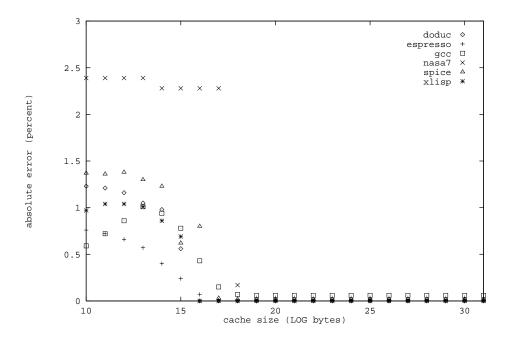

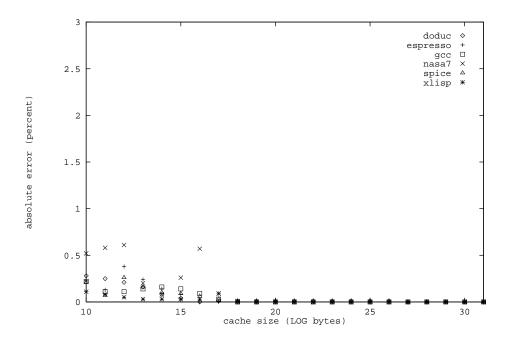

| 3.11   | : Absolute error for fill-flush, direct-mapped caches, $L_S=200,000.$             | 41   |

| 3.12   | : Absolute error for fill-flush, fully associative caches, $L_S=200,000$          | 41   |

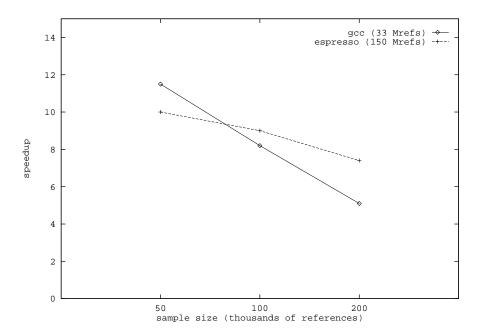

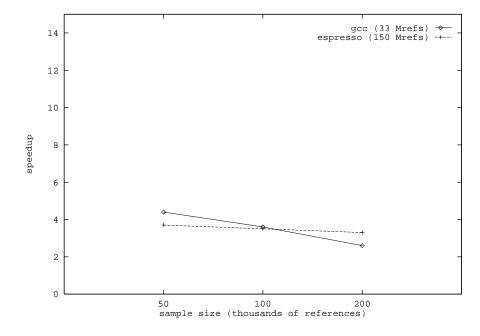

| 3.13   | : Speedup of fill-flush approach over no sampling for benchmarks gcc and          |      |

|        | espresso                                                                          | 43   |

| 3.14   | : A no-state-loss approach to extending a single-pass cache simulation al-        |      |

|        | gorithm for sampling                                                              | 46   |

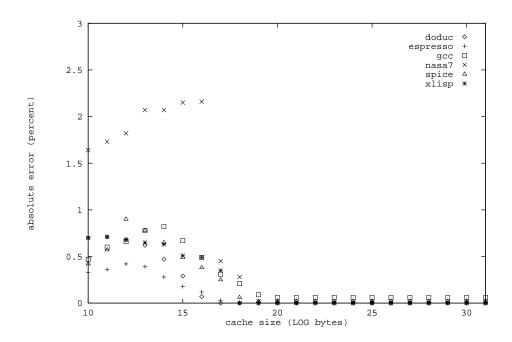

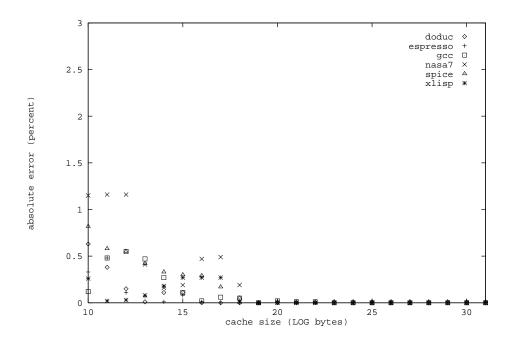

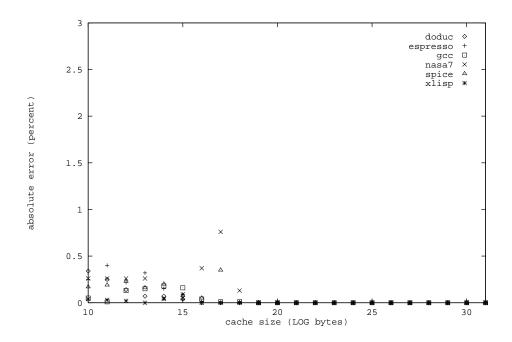

| 3.15   | : Absolute error for no-state-repair, direct-mapped caches, $L_S = 50,000$ .      | 46   |

| 3.16   | : Absolute error for no-state-repair, fully associative caches, $L_S = 50,000$ .  | 47   |

|        | : Absolute error for no-state-repair, direct-mapped caches, $L_S = 100,000$ .     | 47   |

| 3.18   | : Absolute error for no-state-repair, fully associative caches, $L_S = 100,000$ . | 48   |

|        | : Absolute error for no-state-repair, direct-mapped caches, $L_S = 200,000$ .     | 48   |

|        | : Absolute error for no-state-repair, fully associative caches, $L_S = 200,000$ . | 49   |

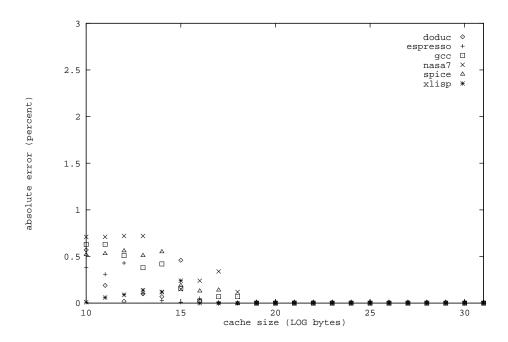

| 3.21   | : Speedup of no-state-loss approach over no sampling for benchmarks gcc           |      |

|        | and espresso                                                                      | 49   |

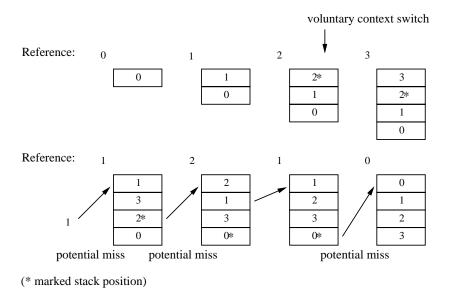

| 3.22: | An example for voluntary context switch of the modified LRU stack op-                     |

|-------|-------------------------------------------------------------------------------------------|

| 0.00  | eration.                                                                                  |

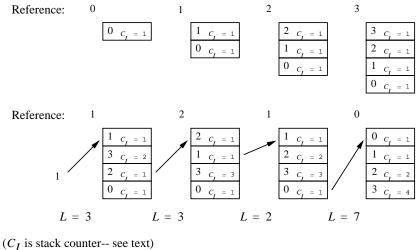

|       | An LRU stack method modified for context switching                                        |

| 3.24: | An example for involuntary context switching of the modified LRU stack                    |

| 225   | operation.                                                                                |

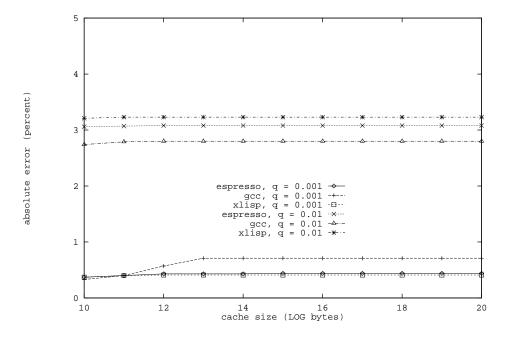

| 3.25: | Absolute error of the miss ratio for random-interval simulation vs. single-               |

| 2 2 2 | pass method, $q = 0.01$ and $q = 0.001$                                                   |

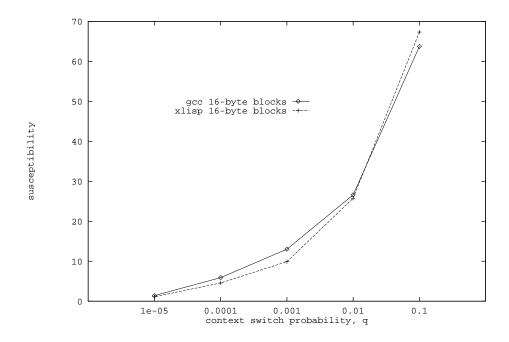

|       | $\Delta \rho$ (involuntary) of gcc and xlisp vs. q for block size 16 bytes                |

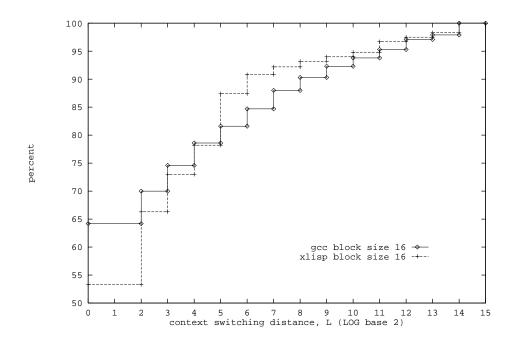

|       | Cumulative distribution of $n_L$ vs. $L$ for block size 16 bytes                          |

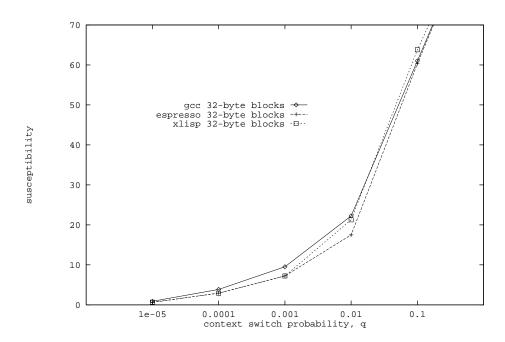

|       | $\Delta \rho$ (involuntary) of gcc, espresso and xlisp vs. q for block size 32 bytes.     |

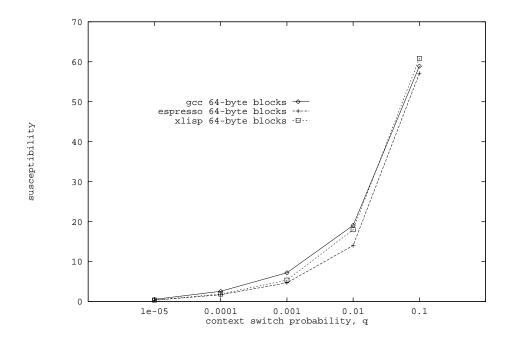

|       | $\Delta \rho$ (involuntary) of gcc, espresso and xlisp vs. q for block size 64 bytes.     |

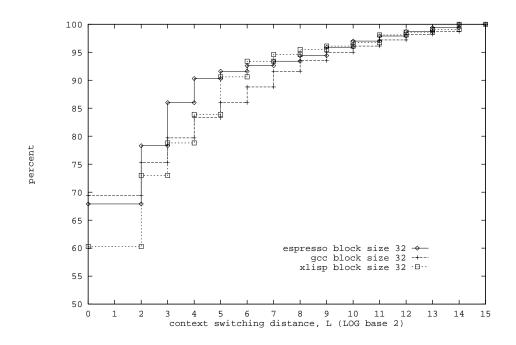

|       | Cumulative distribution of $n_L$ vs. $L$ for block size 32 bytes                          |

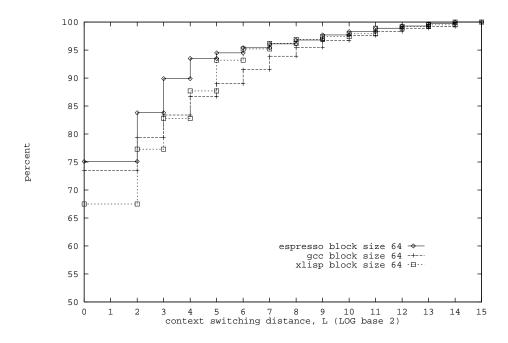

|       | Cumulative distribution of $n_L$ vs. $L$ for block size 64 bytes                          |

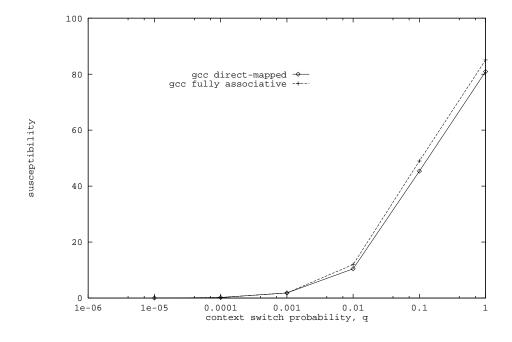

|       | $\Delta \rho$ (involuntary) of gcc for caches $(10, 4, -)$                                |

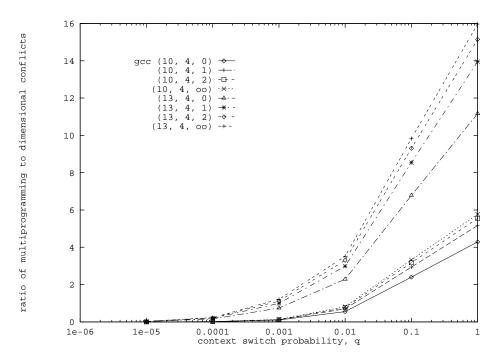

|       | M/D vs. q for gcc, caches $(10, 4, -)$ and $(13, 4, -)$                                   |

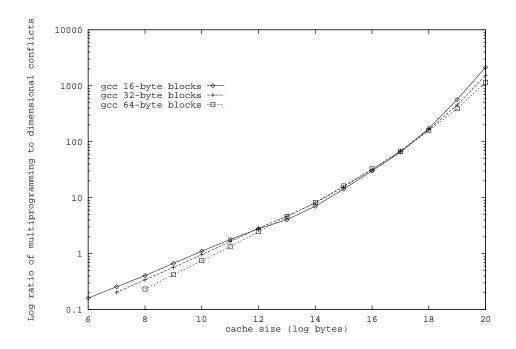

|       | $\log(M/D)$ vs. cache size, for various block sizes $(q = 0.02)$                          |

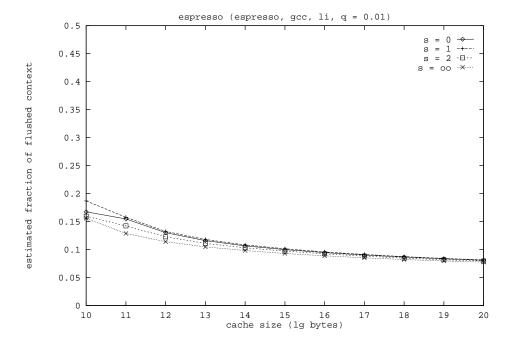

|       | $f_{CS}$ vs. cache size for espresso, $q = 0.01$                                          |

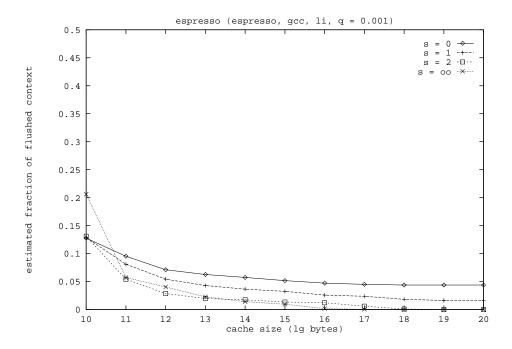

| 3.36: | $f_{CS}$ vs. cache size for espresso, $q = 0.001$                                         |

| 4.1:  | Two example instruction sequences                                                         |

| 4.2:  | An example of anti- and output dependencies                                               |

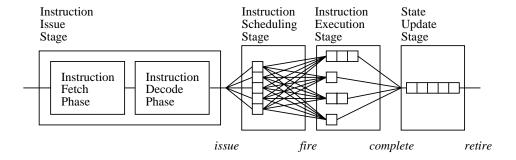

| 4.3:  | Class of processors considered in this thesis                                             |

| 4.4:  | Queue-based FOCO-class processor simulation algorithm                                     |

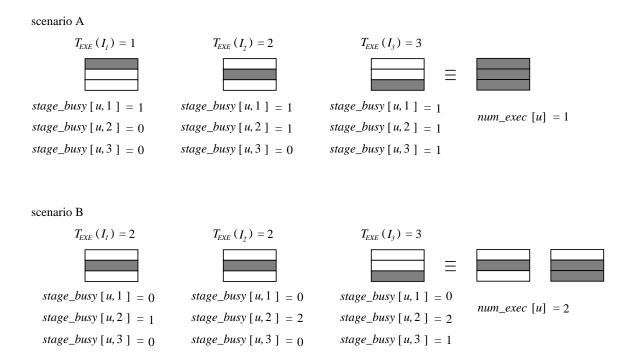

| 4.5:  | Two scenarios to explain the use of $stage\_busy$ in the queue-based simu-                |

|       | lation algorithm.                                                                         |

| 4.6:  | The event-driven FOCO-class processor simulation algorithm                                |

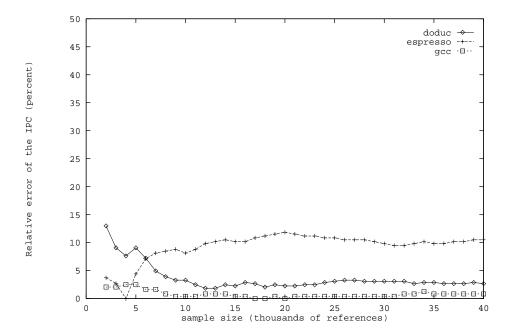

| 4.7:  | RE(IPC) versus sample size for gcc, doduc, and espresso, issue rate eight                 |

|       | instructions per cycle                                                                    |

| 4.8:  | Full-trace vs. sampled resource usage density functions for espresso, $L_S =$             |

|       | 20,000, issue rate eight instructions per cycle                                           |

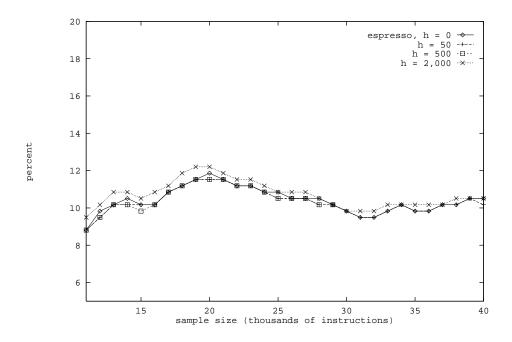

| 4.9:  | Effect of state repair on RE(IPC) for espresso, $h = 0, 50, 500,$ and 2000.               |

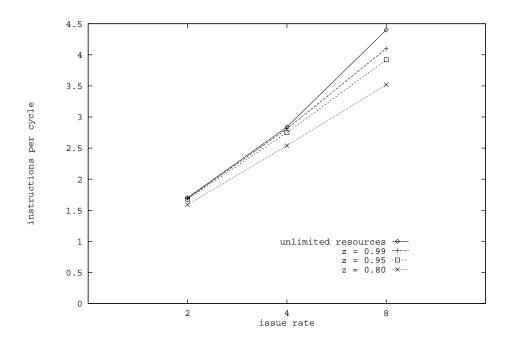

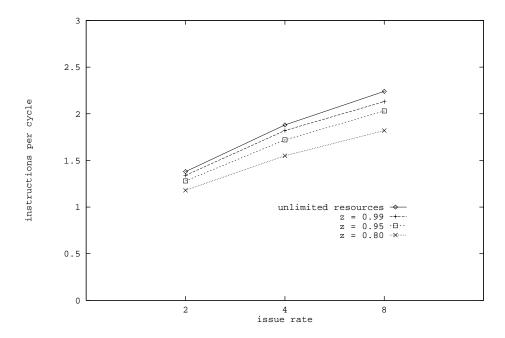

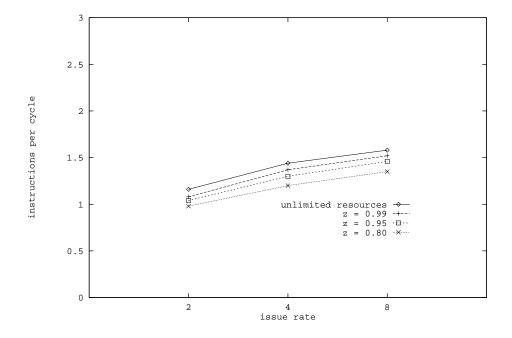

| 4.10: | IPC for function unit number selection criteria of $z=0.80,0.95$ and 0.99                 |

|       | (geometric mean) for all issue rates, canonical latencies                                 |

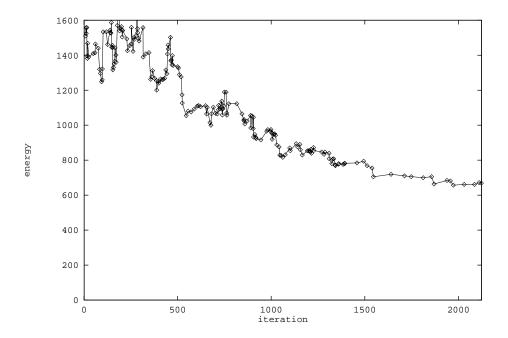

| 4.11: | Evolution of energy for gcc benchmark during execution of simulated                       |

|       | annealing algorithm.                                                                      |

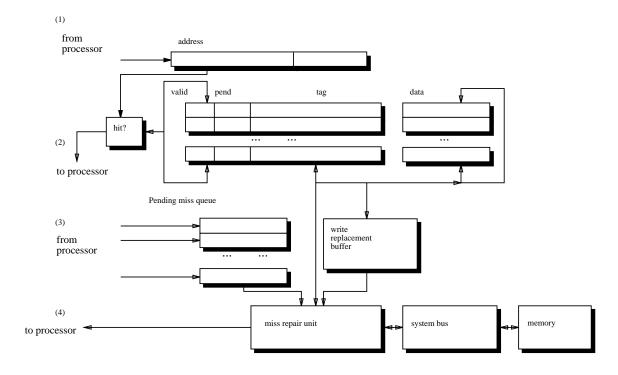

| 5.1:  | Schematic of the design of a non-blocking cache                                           |

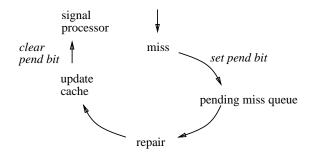

| 5.2:  | State model for a pending miss request                                                    |

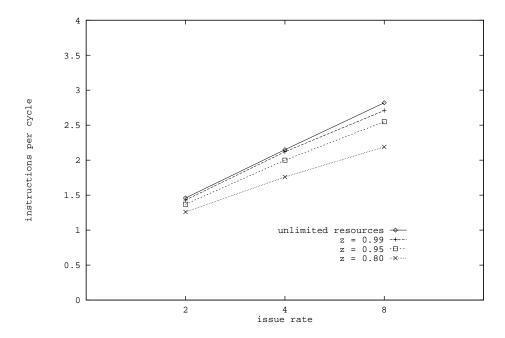

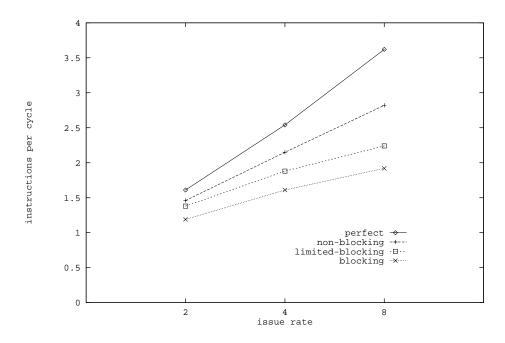

| 5.3:  | Geometric mean of IPC for prototypes $z = 0.99, 0.95, \text{ and } 0.80 \text{ compared}$ |

|       | to unlimited-resource IPC for limited-blocking scheme, $\hat{\rho} = 0.05, T_{MISS} =$    |

|       | 10                                                                                        |

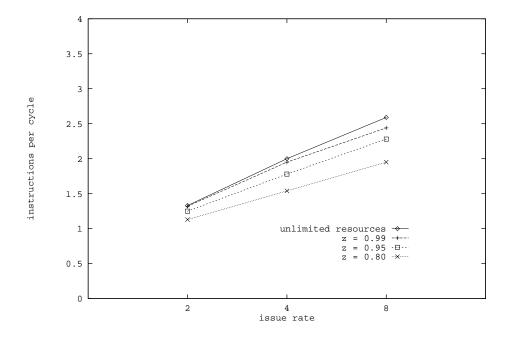

| 5.4:  | Geometric mean of IPC for prototypes $z = 0.99, 0.95, \text{ and } 0.80 \text{ compared}$ |

|       | to unlimited-resource IPC for limited-blocking scheme, $\hat{\rho} = 0.05$ , $T_{MISS} =$ |

|       | 20                                                                                        |

|       |                                                                                           |

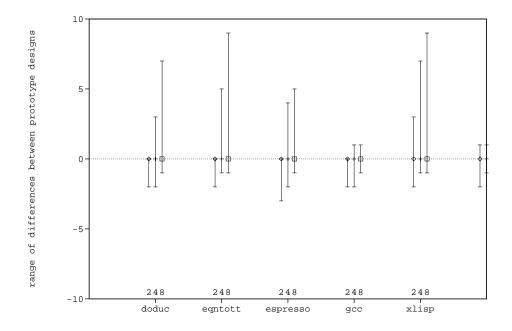

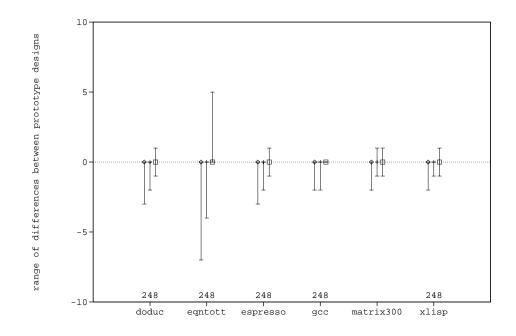

| 5.5:  | Range of differences between prototypes for $limited$ -blocking scheme, $z =$              |     |

|-------|--------------------------------------------------------------------------------------------|-----|

|       | $0.99, T_{MISS} = 10, \hat{\rho} = 0.05$ , issue rates of two, four and eight instructions |     |

|       | per cycle                                                                                  | 151 |

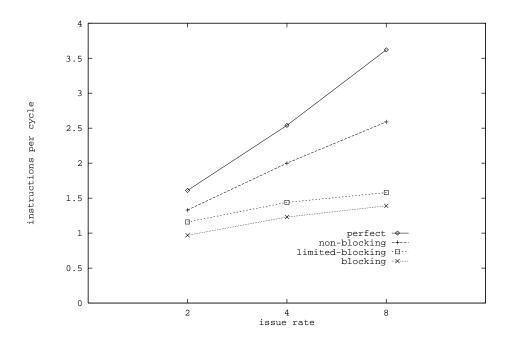

| 5.6:  | Geometric mean of IPC for prototypes $z = 0.99, 0.95, \text{ and } 0.80 \text{ compared}$  |     |

|       | to unlimited-resource IPC for non-blocking scheme, $\hat{\rho} = 0.05$ , $T_{MISS} = 10$ . | 154 |

| 5.7:  | Geometric mean of IPC for prototypes $z = 0.99, 0.95, \text{ and } 0.80 \text{ compared}$  |     |

|       | to unlimited-resource IPC for non-blocking scheme, $\hat{\rho} = 0.05$ , $T_{MISS} = 20$ . | 155 |

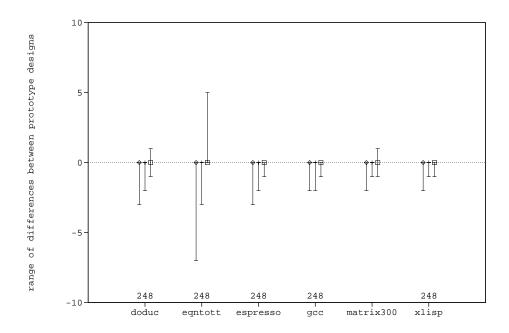

| 5.8:  | Range of differences between prototypes for non-blocking scheme, $z =$                     |     |

|       | $0.99, T_{MISS} = 10, \hat{\rho} = 0.10,$ and issue rates of two, four and eight in-       |     |

|       | structions per cycle                                                                       | 157 |

| 5.9:  | Range of differences between prototypes for non-blocking scheme, $z =$                     |     |

|       | $0.99, T_{MISS} = 20, \hat{\rho} = 0.10,$ issue rates of two, four and eight instructions  |     |

|       | per cycle                                                                                  | 158 |

| 5.10: | The geometric mean of IPC* and IPC for <i>perfect</i> case for issue rates two,            |     |

|       | four and eight instructions per cycle, $T_{MISS} = 10$                                     | 160 |

| 5.11: | The geometric mean of IPC* and IPC for <i>perfect</i> case for issue rates two,            |     |

|       | four and eight instructions per cycle, $T_{MISS} = 20$                                     | 161 |

|       |                                                                                            |     |

#### 1. INTRODUCTION

It is difficult to design successful workstation architectures since these systems are general-purpose and used for a large number of very diverse tasks. Performance of a workstation can be decomposed into that of its components, such as the network, graphics hardware, I/O, processor and memory subsystems. Successful design of these components requires careful consideration of the workload of workstation users. This workload is large and diverse. Current methods for designing these components are iterative processes that are not well-suited to large, diverse workloads. This thesis addresses this problem by developing a systematic method to synthesize prototype architectures of workstation components from large workloads. The thesis focuses on the processor and the memory components, although the overall approach can be applied to the evaluation of other workstation components as well. Special simulation techniques are developed for the task that are fast yet can tackle the very large design space of potential prototypes. New methods are developed to select prototypes from this design space based on cost and performance criteria. The assumption that the processor and memory system components

can be designed independently is checked empirically for three contemporary methods to interface the processor and memory system components together.

### 1.1 The Current Architectural Design Process

Current engineering design methods rely heavily on an iterative approach that begins with the selection of an initial architecture prototype. After the initial prototype is decided upon, it is used as the starting point to a process that evaluates the performance of the prototype and alters its design iteratively until an acceptable level of cost and performance is reached [1]. After the architectural design process is completed, computer-aided design tools are used to realize the architecture. The inputs to the architectural design process are test workloads, often industry-standard benchmarks or end-user supplied applications.

In an effort to better model the workloads of real users, the workloads used for design have grown in size and sophistication, and a general trend toward even larger and more-realistic workloads continues [2],[3]. At the same time, this increase in size places new burdens on the architectural design process, lengthening the process considerably. The simplistic solution to this problem is to limit the size of the workloads used, but this defeats the purpose of using a large workload and results in a poor match between architectural features and end-user needs.

### 1.2 Systematic Computer Architecture Prototyping

It is clear that there are considerable problems with the current architectural design process. What is needed is a systematic approach that can take workload elements such as industry-standard benchmarks or end-user supplied applications and derive architecture prototypes from them. The advantages of such a computer architecture prototyping technique would be:

- The architectural design process would begin with a prototype that is already influenced by diverse workloads,

- Since the architectural design process is iterative, improving the quality of the initial guess also improves the rate of convergence of the overall design process, reducing the number of iterations and enlarging the usable workload size.

This thesis presents a systematic approach to computer architecture prototyping with emphasis on cache-based memory systems and superscalar processor components of workstation systems.

### 1.2.1 The aims of computer architecture prototyping

The aims of computer architecture prototyping are:

- The selection of prototype designs from large workloads.

- The use of a large design space of possible designs.

- The ability to use realistic, large workloads.

These aims are also the challenges of computer architecture prototyping. In order to use a large design space, a general representation of workload behavior must be selected. Since architecture defines the interface between the programmer and the hardware, it is difficult to measure this interaction independent of architectural features. The approach taken in this thesis is to define an interface that includes many viable architectures.

A large design space may require simulation of each point in the design space. Simulation time of each design point is proportional to the length of the workloads used as inputs. Since improving the architectural design process involves reducing overall simulation time, the goals of using a large design space and the ability to use realistic, large workloads are at odds with each other. This thesis attacks the problem by proposing new simulation algorithms that simulate large design spaces very efficiently. To reduce the simulation time further, system cost models are introduced in the case of processor prototyping to reduce the design space to cost-effective designs.

### 1.2.2 The method of computer architecture prototyping

The method of computer architecture prototyping developed in this thesis begins by decomposing the workload into workload elements or benchmarks. The behavior of a benchmark is measured by executing the benchmark on an existing system and recording a trace: a record of the requests made by the benchmark of memory locations or instructions to execute. The trace is recorded with the aid of the compiler. (The format of the trace is discussed in Chapter 2.) The traces of a benchmark are used to

obtain performance of the memory system or the processor. This can be done while the benchmark runs or by using a previously generated and recorded trace.

The trace is used as input to simulations of the memory system. Simulation techniques are used that are capable of evaluating multiple cache memory designs with one scan through the trace. These single-pass techniques were first proposed by Mattson et al. [4]. The techniques are extended to include the effects of multiprogramming (context switching). The result of a single-pass simulation is the performance of a large space of possible cache memory designs. Examples are given of selecting prototypes from this space based on cache performance criteria.

Two simulation techniques are proposed to design prototypes of the processor, each with its own advantages and disadvantages. Two approaches to prototyping using the simulations are also proposed. In the first approach, the benchmark is simulated with an unlimited amount of resources. Criteria are developed to determine actual resource needs based on the usage of resources in the unlimited-resource case. These criteria are evaluated to determine their validity. In the second processor prototyping approach, the problem is formulated as an optimization problem where the parameters are the number, latency and cost of the function units. A design technique based on *simulated annealing* is proposed and demonstrated as a method to find near-optimal prototypes.

In order to evaluate large design spaces, the speed of simulation is crucial. Many benchmarks are too large to simulate in reasonable time. To address this problem, the trace of a benchmark is first reduced in size by use of statistical sampling techniques. Sampling was first proposed by Laha et al. as a method to improve traditional cache memory simulation [5]. This thesis proposes new sampling techniques for the processor and singe-pass memory system simulation.

### 1.2.3 Further uses of computer architecture prototyping

Computer architecture prototyping can be used for two classes of problems that are separate from its application to the architectural design process. One such use is to characterize benchmarks and the other use is to aid in purchasing decisions.

Benchmarks are not only used to design new systems, they are also used to evaluate the performance of existing systems. The trouble with relying on benchmarks to evaluate existing systems is that the characteristics of the benchmarks themselves are unknown. For example, consider two workstations that are identical in every respect except one workstation has a high-performance memory system and the other has a low-performance memory system. A benchmark that requires only a small amount of memory will not be able to distinguish between these two systems. If the purchaser who is trying to interpret the benchmark results has in-house applications that require large amounts of memory, the purchaser should not use this particular benchmark to decide which system to buy.

Computer architecture prototyping can help the above situation by determining the memory system needs for each benchmark and every in-house application. In these situations, the architecture prototypes are also guides to benchmark characteristics. Purchasers should only trust benchmark results from those with characteristics that match

the characteristics of the end users' in-house applications. The idea of using prototypes for benchmark characterization was suggested by Conte and Hwu [6].

The characterization of in-house applications can be used for purchasing decisions in another way. After characterizing in-house applications, the buyers can match the characteristics to those of existing systems in the marketplace. The buyers can then be assured that the purchased system will have an architecture that matches the needs of their in-house applications.

This thesis emphasizes the challenges of generating prototypes and does not consider benchmark characterization or purchasing in further detail. For further discussion, see [6].

#### 1.3 Relation to Previous Work

Methods for hierarchical performance evaluation, first proposed by Kumar and Davidson in [7], are similar to computer architecture prototyping. The aims of hierarchical performance evaluation is to use a hierarchy of performance models with a cost function to select cost-effective designs. The top levels of the hierarchy are occupied by methods that are time-efficient yet have low performance estimating accuracy. These are used to narrow the design space. This narrower design space is then searched using less time-efficient, higher accuracy methods.

Where hierarchical methods seek to replace the design process, computer architecture prototyping is a method to improve the first step. Each approach has its own advantages.

The advantages of generating prototypes are the two additional uses for prototypes, characterizing the benchmarks and aiding in purchasing decisions.

Linear performance models sum the effects of classes of operations to arrive at an estimate of the total run time of a benchmark on a system [8],[9],[10]. For example, the sum of the dynamic count of floating-point operations times the time for a floating-point operation would produce the portion of a program's run time that was due to floating-point multiplication. In general, the performance is recreated as a sum of the benchmark's frequency of use of an operation times the system's latency for executing the operation. The limitations of linear performance models are that they do not account for non-linear effects due to parallelism or for saved state between operations (such as in cache-based memory systems). Modern workstation designs exploit available parallelism and preserve state between operations to achieve high performance. Because of this, linear performance models are inappropriate for the prototyping of workstation designs.

Single-pass cache simulation is a method to evaluate multiple cache designs using one pass over the address trace [4]. Single-pass techniques are ideally suited for the purposes of prototyping and are a topic of this thesis. Statistical sampling has been proposed as a method to speed up traditional cache simulation of very long address traces [5],[11]. Statistical sampling is adapted in this thesis for both single-pass memory system simulation and processor simulation.

The effects of multiprogramming on cache memory performance can invalidate design decisions made using uniprocessor cache simulations [12]. Multiprogramming effects have

been studied by many researchers [13] –[19]. However, no previous study has extended single-pass techniques to model multiprogramming effects. This thesis presents new single-pass techniques that take multiprogramming effects into account.

### 1.4 Organization of Thesis

This thesis is organized as follows. Chapter 2 presents a discussion of the workloads used and the design and collection of traces of the behavior of these workloads. Chapter 3 discusses the prototyping of cache-based memory systems with emphasis on single-pass simulation techniques. A new simulation technique that simulates multiprogramming effects is presented in this chapter. The application of statistical sampling is investigated as a method to improve the performance and trace-size range of memory simulation.

Chapter 4 discusses the architecture and prototyping of superscalar processors. This chapter introduces two simulation techniques for superscalar processor designs. Statistical sampling is applied to these techniques as in Chapter 3. These techniques are combined with cost functions and near-optimal search methods to select superscalar processor prototypes.

The interaction between the processor and the memory system is the topic of Chapter 5. The primary interaction is between the processor and the cache. When a cache miss occurs, the processor can take one of three strategies: block completely, perform limited blocking, or queue the miss requests using a non-blocking cache design. The three

methods are discussed and evaluated along with their respective impacts on prototype selection.

Conclusions and further discussions of this research and its contributions are presented in the final chapter of the thesis, Chapter 6.

#### 2. BENCHMARKS AND INSTRUMENTATION METHODS

The workloads used to design computer architectures take many forms. They are typically composed of benchmarks, test workloads used to evaluate computer performance. The benchmarks are believed to be either representative of the intended workload of the system or capable of providing insight into the range of performance variation of the system. Investigation of the usage of benchmarks used by papers presented at the International Symposia on Computer Architecture, years 1984-1990, reveals seven common categories of benchmarks:

Application benchmarks are runs of programs that are widely used to perform some critical function for a user. Example application benchmarks are sessions from database systems or runs of numerical packages performing functions such as matrix multiply or Gaussian elimination.

**Kernel benchmarks** are code fragments extracted from real programs, where the code fragment is believed to be responsible for most of the execution time of the program.

Many of these benchmarks have the same advantages as the synthetic benchmarks (see below): small code size and long execution time. Kernel benchmarks appear to be heavily used in computer architecture studies [20].

Partial benchmarks are partial traces of programs. One drawback of their use is that independent reproduction of results is difficult since the portion of the benchmark traced is often unknown.

Recursive algorithm benchmarks are programs implementing recursive algorithms such as the solutions to the Hanoi towers problem and the Nine-Queens problem.

These benchmarks are not applications, they do not perform often-used functions.

Synthetic benchmarks are small programs especially constructed for benchmarking purposes. They do not perform any useful computation. The intent of synthetic benchmarks is to use a small program to approximate the average characteristics of real programs. At one time, the popularity of synthetic benchmarks was on the rise; however, they have experienced declining use in recent years.

OS utility benchmarks are taken from commonly used utilities such as the Unix sort or tar.

Unspecified benchmarks is a catch-all category for unspecified workload descriptions.

Some uniprocessor papers used traces collected from systems in which the use of the system was either not reported in the paper or unknown.

Table 2.1: Benchmark usage in *International Symposium on Computer Architecture*, 1984-1990.

|               |      |      |      | Year |      |      |      |            |

|---------------|------|------|------|------|------|------|------|------------|

| Category      | 1984 | 1985 | 1986 | 1987 | 1988 | 1989 | 1990 | Percentage |

| Applications  | 2    | 2    | 2    | 5    | 4    | 3    | 5    | 16%        |

| Kernel        | 3    | 2    | 6    | 4    | 5    | 3    | 4    | 19%        |

| Local         | 1    | 1    | 4    | 0    | 2    | 3    | 7    | 13%        |

| Partial       | 0    | 0    | 2    | 0    | 2    | 2    | 1    | 5%         |

| Recursive     | 3    | 5    | 6    | 5    | 3    | 6    | 4    | 22%        |

| Synthetic     | 1    | 0    | 3    | 5    | 1    | 0    | 0    | 7%         |

| OS Utility    | 1    | 2    | 1    | 4    | 2    | 4    | 5    | 13%        |

| ${ m Unspec}$ | 2    | 2    | 1    | 0    | 1    | 1    | 0    | 5%         |

**Local benchmarks** are programs that are site-specific or in-house applications that are not widely available (in contrast to application benchmarks that are widely used and available).

Use of unspecified and partial benchmarks occurs relatively infrequently in the papers that were surveyed. Table 2.1 presents the count of papers using benchmarks from each category (note that in some instances one paper used benchmarks from several categories). A complete list of the papers and their categorization are presented in [20].

In 1989, the System Performance Evaluation Cooperative released version 1 of a benchmark suite designed to evaluate the performance of workstations [3]. This benchmark suite is now commonly referred to as SPEC89. Table 2.2 lists benchmarks that are members of the SPEC89 suite (compiled with aid of [3]). The table also assigns one of the above categories to each benchmark.

Table 2.2: The SPEC89 benchmark suite.

|                  | La                     | I B                                        |

|------------------|------------------------|--------------------------------------------|

| Benchmark        | 9                      | Description                                |

| doduc            | application            | Monte Carlo simulation of the time         |

|                  |                        | evolution of a thermohydraulical           |

|                  |                        | modelization for a nuclear reactor.        |

| eqntott          | application            | Generates truth table from logic           |

|                  |                        | equations.                                 |

| espresso         | application            | Performs PLA optimization.                 |

| fpppp            | application            | Simulates two electron integral            |

|                  |                        | derivative (quantum chemistry).            |

| gcc              | OS utility             | GNU C compiler, version 1.35.              |

| matrix 300       | kernel                 | Performs $300 \times 300$ matrix multiply. |

| nasa7            | kernel, synthetic      | Seven kernels: a matrix multi-             |

|                  |                        | ply, an FFT, a Cholesky decom-             |

|                  |                        | position, a tradiagonal matrix so-         |

|                  |                        | lution, a Gaussian elimination, a          |

|                  |                        | boundary value problem, and a              |

|                  |                        | three-matrix pentadiagonals inver-         |

|                  |                        | sion (developed by NASA Ames).             |

| ${ m spice 2g6}$ | application            | Performs analog circuit simulation         |

|                  |                        | (with greycode digital circuit as          |

|                  |                        | input).                                    |

| tomcatv          | kernel                 | Generation of finite mesh.                 |

| xlisp            | application, recursive | Lisp interpreter (the application)         |

|                  |                        | executing the Nine-Queens problem          |

|                  |                        | (the recursive benchmark).                 |

The SPEC89 benchmark suite covers six of the eight categories of benchmarks presented above (the remaining two categories, unspecified and partial, have negative connotations). The suite is used in this thesis as a workload to test the computer architecture prototyping methods that are developed herein. Its use does not constitute a claim that the suite is representative of the workloads of actual workstations. However, since the benchmark suite is being used to evaluate the performance of existing workstations, it is the logical choice for the design of future workstations [6]. Since SPEC89 has this role in future designs, computer architecture prototypes derived from SPEC89 benchmarks serve as important tests of the prototyping techniques.

The following sections discuss measurement of the behavior of benchmarks such as members of the SPEC89 benchmark suite in some detail.

#### 2.1 Collection of Traces of Benchmark Behavior

A benchmark as it executes makes requests of the system and alters its behavior accordingly. The requests can be in the form of instructions to execute, references to memory locations, requests to the kernel for system functions, etc. The term *trace* is used here to refer to a log of these requests.

### 2.1.1 Address trace collection

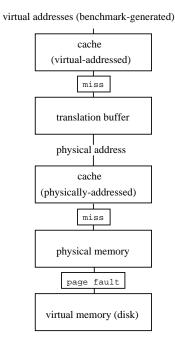

Figure 2.1 shows a memory hierarchy with one cache indexed by virtual addresses, one cache indexed by physical addresses, the physical memory and the virtual memory

of the system. Only the address usage is shown in the figure, the data path has been omitted. An address trace can be taken at any point along this hierarchy. Address

Figure 2.1: A typical memory hierarchy showing address usage.

traces taken lower in the hierarchy are specific to the behavior of the combination of the program and the hardware. For example, in the figure the physical cache in the picture receives only references that miss in the virtual cache and are translated to physical addresses; therefore, its address trace is a function of the design of the virtual cache. It is also a function of the multiprogramming level of the system, since the virtual-to-physical page mapping depends on the ensemble of the address requests of all jobs running in the system. However, pages are only mapped to physical locations at power-of-two boundaries. If the trace is composed of the virtual addresses, the simulation of a first-level physical cache with size less

than the page size is also valid. For the remainder of the hierarchy, a prototype cache for a given level can be used to *filter* the trace for use in simulating the next-level cache. For these reasons, the *virtual address trace*, a trace of the virtual addresses referenced during the execution of the program, is used in this thesis.

The compiler can aid in tracing the virtual address trace by generating extra instructions surrounding all load/store operations. These added instructions record the addresses of the load or store them in a trace buffer. During program execution, the trace buffer is periodically flushed to a trace consumer (e.g., a simulator) or written to a file. This technique is an application of software instrumentation and has been used by Larus for AE, Stunkel and Fuchs for TRAPEDS, and Golden for Spike, among others [21]–[23]. This thesis uses Spike for software instrumentation of virtual address traces.

#### 2.1.2 Instruction trace collection

Capturing traces of instructions poses a difficult problem for a system created to prototype hardware. Instruction encodings are idiosyncratic and vary widely from vendor to vendor. In the case of some RISC architectures, the instruction set reflects the latencies of the underlying hardware (e.g., the number of branch and load delay slots) [24]. This further complication causes the traces recorded using some instruction sets to be hardware specific.

This thesis uses the GNU C retargetable, optimizing compiler (version 1.40) with optimizations enabled to translate benchmark source into executables [25]. The intermediate

code of a retargetable compiler is designed to be translated into many different instruction sets. The instruction-set architecture of the processor in this thesis is assumed to be this intermediate-code language. This approach has been used previously in [26]. The processor simulation methods rely only on the type of each instruction and the identities of the operands. For this reason, other instruction formats can be used with the trace without modification. The use of intermediate-code removes machine-specific operand restrictions or instruction-format restrictions. Delay slots and other hardware-specific features are not encoded. The resulting trace is free of anomalies that might complicate the interpretation of the results.

The traces of the intermediate code are collected by creating templates of the intermediate instructions for each basic block at compile time. Also at compile time, additional code is added to mark the entrance of each basic block and record its *id* in the trace buffer. At run time, the contents of the trace buffer are interpreted and the *id*s of basic blocks are used in conjunction with the database of intermediate-instruction templates to generate a trace of the intermediate instructions. This instruction trace appears to the trace consumer as though the benchmark had executed on a machine with the intermediate code as its instruction set. Further discussions of this technique are presented in [22] and [23].

## 2.1.3 In-process trace generation

Traces are traditionally written to a secondary storage device and then used for simulation. Two of the SPEC89 benchmarks, gcc and espresso, have data address traces of slightly more than 33 million and 150 million references, respectively. Each of the references is a 32-bit quantity, resulting in sizes of 132–600 megabytes of storage. The gcc and espresso benchmarks have the two smallest data address traces of the benchmarks in the SPEC89 benchmark set. This suggests that trace storage conflicts with the aim of architecture prototyping to use large, diverse workloads. Statistical techniques can be used to reduce the size of traces to manageable sizes [5]. This thesis further develops these ideas. In order to validate the results of the statistical techniques, the simulation results from full-trace simulations are still required.

This thesis uses a solution to the problem of large trace size termed *in-process trace* generation. In this technique, the simulation is combined with the benchmark in the same process. The simulator is compiled as an auxiliary function to the benchmark, and the compiler inserts periodic calls to the simulator to flush the trace buffer. The trace need not be recorded since it is re-generated by running the benchmark. Section 3.2.2 of Chapter 3 exploits this trace generation method to improve upon statistical techniques.

### 2.1.4 Library code

The most common operating systems used for workstations are based on 4.3BSD Unix [27]. Unix employs a set of user-code libraries to implement many functions. Exclusion of library code from the trace would exclude frequently used functions. To circumvent this problem, software-instrumented versions of the libraries are compiled and used along with the benchmarks. The specific libraries are taken from SunOS version 4.1.1, but generic versions of most library functions are used.

In addition to library functions, the operating system kernel interacts with the benchmark either at the request of the benchmark via system calls or periodically to implement multiprogramming [27]. This thesis treats these system call interactions as special events and records their occurrence. As an example of system call usage, Table 2.3 reports the

Table 2.3: Dynamic system call usage.

| Benchmark | System calls                                         |

|-----------|------------------------------------------------------|

| gcc       | getrusage (6072), write (164), sbrk (66), read (15), |

|           | open (2), close (2), fstat (2), ioctl (2),           |

|           | getpagesize (1)                                      |

| espresso  | write (27), sbrk (18), read (4), ioctl (2),          |

|           | fstat (2), open (1), getpagesize (1)                 |

| spice     | write (784), lseek (6), fstat (5), sbrk (3),         |

|           | close (3), read (3), ioctl (3), getpagesize (1)      |

| xlisp     | sbrk (7), ioctl (2), fstat (2), open (1),            |

|           | getpagesize (1), read (1)                            |

| matrix300 | lseek (12), fstat (5), close (5), stat (3),          |

|           | sbrk (3), write (3), ioctl (2), open (2),            |

|           | getdtablesize (1), getpagesize (1)                   |

system calls used by some members of the SPEC benchmark set and the number of dynamic occurrences of each system call (in parentheses). The getrusage system call that is prominent for gcc is used by the times library call to report run times. The sbrk call is used in the heap space allocator. Heap space is used significantly in xlisp and espresso. Since the malloc() function is included in the tracing process, heap management is included in the virtual address trace. I/O intensive benchmarks reveal themselves here by the use of the read, write, open, close, fstat, lseek, and ioctl calls. These benchmarks are spice and gcc. The dynamic percentage of execution taken up by system call events was not reported in Table 2.3 since it would be close to zero for all cases.

Kernel code is specific to each vendor and as such is difficult to generalize to a system-independent format. However, it is possible to view the kernel as simply another benchmark for the purposes of prototyping. The kernel appears to the hardware as just another program that it must execute along with other programs (benchmarks) in the system. Although this is an appealing approach to the treatment of prototyping using the kernel, the kernel is not included in the benchmark set used in this thesis. System call interactions between an executing benchmark and the kernel are captured, and interactions such as interrupts due to expired quanta are modeled. These models are used to adjust the prototypes of the memory system in Chapter 3.

#### 3. MEMORY SYSTEM PROTOTYPING

Multiple levels of caching and buffering have become the norm in memory system design. Memory hierarchies composed of cache memories are so crucial to high-performance computer architecture design that performance evaluation of cache memories has received phenomenal attention. In 1991, Smith catalogued 487 technical papers and reports that dealt with some aspect of caching [28]. This chapter addresses the problem of deriving prototypes of memory systems designed with caching. To do this requires measurement of the performance of a large number of cache designs. This cache performance evaluation process must be fast yet accurate. The importance of accuracy is self-evident. A fast method is important so that memory address traces from long-running benchmarks can be used to explore a large design space of potential prototypes.

Researchers have devised analytic models and novel simulation approaches to measure cache performance [4],[29],[30]. Analytic cache models achieve low accuracy and are therefore inappropriate for prototyping memory systems. Of the simulation approaches, the direct approach is to simulate the cache at the register-transfer level. This approach

is called the traditional cache simulation approach throughout this chapter. Prototyping demands simulation of a large number of cache designs, limiting the usefulness of traditional cache simulation. To eliminate the number of required simulations, single-pass cache simulation is used. Such methods simulate multiple cache dimensions in a single pass by exploiting the inclusion property of stacking replacement algorithms (least-recently used is the most common member of this class of replacement algorithms [4]). This method has been extended to include rigid placement/replacement algorithms used in direct-mapped caches [31]. Single-pass cache simulation is ideally suited for prototyping.

This chapter focuses on using the recurrence/conflict single-pass cache simulation technique for prototyping memory systems. Two extensions to this single-pass technique are discussed. The speed of the technique is improved while maintaining acceptable accuracy by adapting statistical sampling techniques developed for traditional simulation to work with single-pass simulation. The single-pass technique is also extended to capture multiprogramming effects. Multiprogramming degrades memory system performance since (process) context switching reduces the effectiveness of cache memories. For the prototypes to be correct, multiprogramming effects must be taken into account.

### 3.1 Single-Pass Cache Simulation

A traditional cache simulator uses a data structure that is a replica of the tag store of the cache being simulated. The simulation involves updating this data structure at each reference. When an address in the trace is not present in the tag store structure, the corresponding cache miss is recorded. The advantages of such a technique are its efficiency and simplicity. A simple array can be used for the tag store of a direct-mapped cache. The time complexity for such an algorithm is O(N) in N inputs. Since the tag store does not change in size during simulation, the space complexity is O(1).

The disadvantage of the traditional cache simulator is its lack of generality. A simulation must be performed for each configuration of cache under study. Hence the term multiple-pass cache simulator can be used to describe the traditional simulator since it requires multiple passes over the trace.

Single-pass cache simulation techniques rely on the inclusion property of stacking replacement algorithms. Exploitation of this property allows this class of simulators to find the miss ratios for an entire design space of cache dimensions with one pass over the trace. The space complexity of these algorithms is directly proportional to the *static* program size. Hence, it is O(1). The disadvantage of these approaches is their time complexity, which is  $O(N \times d)$ , where d is the average stack depth [30]. The particular single-pass simulation approach presented in this paper is based on the recurrence/conflict model of the miss ratio. The model is introduced below followed by a description of the simulation method.

#### 3.1.1 Recurrences and conflicts

The metric used in many memory system studies is the miss ratio. This is the ratio of the number of references that are not satisfied (i.e., that miss) for a cache at a level of the memory system hierarchy over the total number of references made at that level. The miss ratio has served as a good metric for memory systems since it is a characteristic of the workload (e.g., the memory trace) yet independent of the access time of the memory elements. A given miss ratio can be used to decide whether a potential memory element technology will meet the required access time for the memory system [13]. The recurrence/conflict model of the miss ratio is best illustrated with an example. Consider the trace of Figure 3.1. The recurrences in the trace are accesses e, f, g and h. In the ideal case of an infinite cache, the miss ratio may be expressed as

$$\rho = \frac{N - R}{N},\tag{3.1}$$

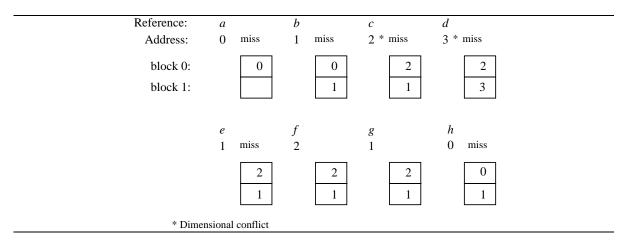

where R is the total number of recurrences and N is the total number of references. Non-ideal behavior occurs due to conflicts. A dimensional conflict is defined as an event which converts a recurrence into a miss due to limited cache capacity or mapping inflexibility. For illustration, consider a direct mapped cache composed of two one-byte blocks shown in Figure 3.2. (Note that in practice, such a small cache would be impractical to build.)

Figure 3.1: An example trace of addresses.

Figure 3.2: An example two-block direct-mapped cache behavior.

A miss occurs for the recurring reference e because reference d purges address 1 from the cache due to insufficient cache capacity. Similarly, a miss occurs for recurring reference h due to reference e. References e and e represent a dimensional conflict for the recurrences e and e and e respectively. The other misses, e and e and e occur because these are the first references to addresses e and e and e are present and e are following formula can be used for deriving cache miss ratio, e, for a given trace, a given cache dimension:

$$\rho = \frac{N - (R - D)}{N},\tag{3.2}$$

where D the total number of dimensional conflicts. (For the example,  $\rho = (8 - (4 - 2))/8$  = 0.75.) This is a general model and can be extended to account for other effects, such as conflicts due to multiprocessor cache coherence [32] and context switching (see Section 3.3).

#### 3.1.2 Reference streams and cache dimensions

A formal abstraction of a benchmark's trace is termed a reference stream. This is a sequence of references to addresses, w(k), of length N ( $0 \le k < N$ ). When required, the addresses are represented by lower-case Greek letters, such as  $\alpha, \beta, \gamma$ . The reference stream is assumed to be generated by a single process in a multiprogramming system. Note that a reference at w(k) occurs later than w(k+1) in time, but the parameter k does not represent parameterized time since it does not take into account the difference in service times between cache hits and cache misses. For this reason, k is referred to as the reference count. The trace also contains information about voluntary context switching. A reference is called a voluntary context-switch event if the benchmark relinquished the CPU after the reference (e.g., a system call was performed).

The dimension of a cache is expressed using the notation, (C, B, S), for a cache of size  $2^C$  bytes, with block size  $2^B$  bytes, and  $2^S$  blocks contained in each associativity set. The term set size is used to mean associativity level, or the number of blocks per set. Cache size is the total number of bytes per cache. Block size has been called line size elsewhere [17]. Note that  $C \geq B + S$ . The notation  $(C, B, \infty)$  is an abbreviation for the dimension of a fully associative cache (S = C - B). For example, a cache of dimension (10,6,0) is a 1KB direct-mapped cache with a block size of 64 bytes; and, a cache of dimension (21,10,11) (alternately,  $(21,10,\infty)$ ) is of size 2MB with 1KB-length blocks and it is fully associative. A dash is substituted for an entry in the triple to indicate all caches of that dimension: (-,5,1) are all caches with block size of 32 bytes and having

2-way associativity. Caches are assumed to use LRU replacement and map addresses into sets using bit selection [30].

It is useful to partition the reference stream by setting the block offset portion of all addresses in the stream to zero. This produces a block reference stream,  $w_B(k)$ , which is defined such that

$$w_B(k) = 2^B \left| \frac{w(k)}{2^B} \right| .$$

In binary, this is equivalent to setting the least-significant B bits to zero.

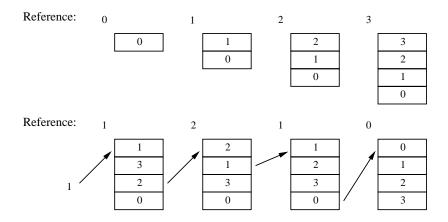

## 3.1.3 Least-recently used (LRU) stack operation

Least-recently used (LRU) stacks were first introduced by Mattson et al. in [4] as a way to model the behavior of paging systems. An LRU stack operates as follows: when an address,  $w_B(k) = \alpha$ , is encountered in the block reference stream, the LRU stack is checked to see if  $\alpha$  is present on the stack. If  $\alpha$  is not present, it is pushed onto the stack. However, if  $\alpha$  is present (e.g., it is a recurring reference), it is removed from the stack,

Figure 3.3: An example of LRU stack operation.

then repushed onto the stack. This is illustrated in Figure 3.3 for the example reference stream at the beginning of this section (Figure 3.1).

A stack is represented as  $S_B(k)$ , maintained for a block size B at time k. The ith ordered item of  $S_B(k)$  is expressed as,  $S_B(k)[i]$ . The stack may also be expressed as an ordered list, such that  $S_B(k) = \{S_B(k)[0], S_B(k)[1], \ldots, S_B(k)[m]\}$ , where m is the depth of the stack. The following operations are defined for a stack: the  $\mathbf{push}(\cdot)$  function,

$$\mathbf{push}(S_B(k), \alpha) = \{ \alpha, S_B(k)[0], S_B(k)[1], \dots, S_B(k)[m] \},\$$

the  $\Delta(\cdot)$  function,

$$\Delta(S_B(k), \alpha) = i,$$

if  $S_B(k)[i] = \alpha,$

and, the  $repush(\cdot)$  function,

repush

$$(S_B(k), \alpha) = \{ \alpha, S_B(k)[0], S_B(k)[1], \dots, S_B(k)[\Delta(S_B(k), \alpha) - 1], S_B(k)[\Delta(S_B(k), \alpha) + 1], \dots, S_B(k)[m] \}.$$

$\Delta(S_B(k), \alpha)$  and  $\mathbf{repush}(S_B(k), \alpha)$  are undefined when  $\alpha \notin S_B(k)$ . When  $S_B(k)$  and  $\alpha$  are understood, it is convenient to use  $\Delta = \Delta(S_B(k), \alpha)$ . Note that  $\mathbf{push}(\cdot)$  and  $\mathbf{repush}(\cdot)$  are defined as side-effect-free functions rather than procedures. This is to remove dependence on the time variable, k.

The least-recently used management policy for a stack is shown in Figure 3.4 for an address  $\alpha = w_B(k)$ . In Step 1.1, the references between the top of stack and the recurring

reference have been referred to as the set,  $= \{\beta_i \mid \beta_i = S_B(k-1)[i], 0 \le i \le \Delta \}$ . Figure 3.4 is applied to  $\alpha = w_B(k)$  for all k. The LRU policy is essentially a definition

```

1. if \alpha \in S_B(k-1) then

1.1 do_recurrence(\alpha, , )

1.2 S_B(k) \leftarrow \operatorname{repush}(S_B(k-1), \alpha),

2. else S_B(k) \leftarrow \operatorname{push}(S_B(k-1), \alpha)

3. N \leftarrow N+1

```

Figure 3.4: The least-recently used management policy for a stack,  $S_B(k)$  (adapted from Mattson *et al.*).

for calculating  $S_B(k)$  from  $S_B(k-1)$  and  $\alpha$ . In most situations,  $S_B(k)$  is calculated in order to obtain other statistics, such as the stack depth distribution.

The complexity of the algorithm of Figure 3.4 depends on the complexity of the do\_recurrence() procedure. Assume for the moment that the complexity of this procedure is O(d) on average (the validity of this assumption is justified below). The outer algorithm's complexity is also dependent on the efficiency of the set (stack) existence operator in Step 1. In Mattson et al. [4], the set-existence operation was determined by scanning the entire stack. This has an average complexity O(d) for the set existence, where d is the average stack depth [30]. This results in a complexity of  $O(N \times d)$  for the entire algorithm. This approach to calculating set existence can be replaced by using a hash table lookup, where each entry of the new table contains a pointer to the stack frame. Hash table lookup also has complexity of O(d) on average [33]. However, there is a practical advantage to using hash table lookup. For the hash table implementation,

only the hash conflict set for the block needs to be searched to determine whether the reference is first-time. This is a constant-time improvement and does not change the asymptotic behavior.

## 3.1.4 Recurrence/conflict-based single-pass simulation

The single-pass cache simulation algorithm for limited associativities (S < C - B) is created by expanding the do\_recurrence procedure of Figure 3.4 [30]. A single-pass algorithm that uses the recurrence/conflict model is presented in Figure 3.5. This algorithm is similar to the original algorithm of Traiger and Slutz [31]. However, where Traiger and Slutz recorded temporal localities, this algorithm records recurrences and conflicts. Since temporal locality functions can occupy considerable space, using recurrences and conflicts is an advantage. In this respect, the recurrence/conflict approach is similar to the algorithm of Hill and Smith [30].

Whenever a reference is found on the stack in Figure 3.5, its presence indicates that it is a recurrence. The calculation of the number of recurrences (R[B]) is implemented by recording the number of times this event occurs in Step 1 of Figure 3.5. The remainder of the algorithm is devoted to calculating the dimensional conflicts (D[C, B, S]).

The for statement that iterates for all intervening references in Step 2 of Figure 3.5 calculates the raw information for determining two classes of cache organizations. The maintenance of the number of unique references (u) in Step 2.1 is used to calculate the largest-sized fully associative cache with a dimensional conflict  $(c_{\infty})$ . This calculation is

```

do_recurrence(\alpha,,):

R[B] \leftarrow R[B] + 1

1

2

for \beta_i \in, do

2.1

u \leftarrow u + 1

2.2

d \leftarrow |\beta_i - \alpha|

z \leftarrow \operatorname{ctz}(d)

2.3

p[z] \leftarrow p[z] + 1

2.4

z_{\text{max}} \leftarrow \max(z, z_{\text{max}})

c_{\infty} \leftarrow \lfloor \lg u \rfloor + B

2.5

3

D[c_{\infty}, B, \infty] \leftarrow D[c_{\infty}, B, \infty] + 1

4

z \leftarrow z_{\max}

5

6

S_{target} \leftarrow 1

7

nss \leftarrow 0

8

for s \leftarrow 0 to S_{\max}

8.1

C_{MC} \leftarrow B

while z \ge 0 and nss < S_{target}

8.2

nss \leftarrow p[z]

8.2.1

8.2.2

z \leftarrow z - 1

if nss \geq S_{target} then

8.3

C_{MC} \leftarrow z + s + 1

8.3.1

D[C_{MC}, B, s] \leftarrow D[C_{MC}, B, s] + 1

8.4

S_{target} \leftarrow 2 \times S_{target}

8.5

```

Figure 3.5: The recurrence/conflict single-pass cache simulation algorithm.

done in Steps 3 and 4 by finding the lg (log base two) of this count. Unlike the algorithm of Mattson et al., only cache sizes that are multiples of powers of 2 are considered [4]. The remainder of Step 2 calculates a histogram, p[z], of a function of the current reference ( $\alpha$ ) and each intervening reference ( $\beta_i$ ) (Step 2.4). This function is the lowest power of two factor of the arithmetic difference between the two references (Steps 2.2 and 2.3). For a range of direct-mapped caches, this function is equivalent to the largest cache size in which a miss will still occur for  $\alpha$  due to the intervening reference to  $\beta_i$ . The remainder of the procedure uses this information to calculate this cache size for all associativities (Steps 5–8).

The histogram (p[z]) is processed for all associativities by scanning the histogram from largest to smallest potential conflicting cache size. A set size can be thought of as a conflict tolerance. A conflict between  $\alpha$  and  $\beta_i$  for a direct-mapped cache of dimension (C, B, 0) is equivalent to  $\alpha$  and  $\beta_i$  occupying the same set in caches (C, B, S) for  $C - B \ge S > 0$ . The larger the set size, S, the more numerous the allowed same-set mappings between references to  $\alpha$  before these mappings result in a miss.

In Steps 6 to 8, the set sizes are considered in increasing order to determine how many same-set mappings are tolerable. For each set, the largest cache size in which a miss will occur,  $C_{MC}$ ,  $(MC = maximum\ conflict)$  is the product of the same cache size for a direct-mapped cache times the set size (Step 8.3.1, note that addition of these exponents of base 2 implies multiplication). If no same-set mappings remain in the histogram,

the only conflicts accounted for are those that occur in caches containing a single block (Step 8.1).