#### DATA RELOCATION AND PREFETCHING FOR PROGRAMS WITH LARGE DATA SETS

#### BY

#### YOJI YAMADA

B.Engr., Tokyo Institute of Technology, 1980 M.Engr., Tokyo Institute of Technology, 1982

#### THESIS

Submitted in partial fulfillment of the requirements for the degree of Doctor of Philosophy in Computer Science in the Graduate College of the University of Illinois at Urbana-Champaign, 1995

Urbana, Illinois

# DATA RELOCATION AND PREFETCHING FOR PROGRAMS WITH LARGE DATA SETS

#### YOJI YAMADA, Ph.D.

Department of Computer Science University of Illinois at Urbana-Champaign, 1995 Wen-mei W. Hwu, Advisor

Numerical applications frequently contain nested loop structures that process large arrays of data. The execution of these loop structures often produces memory preference patterns that poorly utilize data caches. Limited associativity and cache capacity result in cache conflict misses. Also, non-unit stride access patterns can cause low utilization of cache lines. Data copying has been proposed and investigated in order to reduce the cache conflict misses [1][2], but this technique has a high execution overhead since it does the copy operations entirely in software.

I propose a combined hardware and software technique called data relocation and prefetching which eliminates much of the overhead of data copying through the use of special hardware. Furthermore, by relocating the data while performing software prefetching, the overhead of copying the data can be reduced further. Experimental results for data relocation and prefetching show a large improvement in cache performance.

#### ACKNOWLEDGMENTS

First and foremost, I would like to acknowledge my advisor, Professor Wen-mei W. Hwu, for his kind guidance, his intellectual support, and his patience. I am very glad to have worked with him, and I will be pround of that forever.

Next, I would like to acknowledge the support of my Ph.D. committee members for their useful suggestions with regard to my thesis research.

This research would not have been possible without the support of the IMPACT research group. I would like to thank John Gyllenhaal and Grant Haab for the simulation support and useful discussion regarding my research. Many thanks to Sadun Anik, Roger Bringmann, William Chen, Dave Gallagher, Rick Hank, Sabrina Hwu, Dan Lavery, Scott Mahlke, Krishna Subramanian, and Nancy Warter.

I would like to acknowledge the financial support of Mazda Motor Corporation for my graduate study.

Lastly, I would like to acknowledge the support of my family. I would like to acknowledge my parents for their love. I would like to thank my son, Shinji, and daughter, Emi, for their smiles, which really relaxed my fatigue due to this thesis work. I would like to thank my wife, Hideko, for her cooking, love and patience.

# TABLE OF CONTENTS

| CF | HAPT       | ER     |                                          | PAGE |

|----|------------|--------|------------------------------------------|------|

| 1  | INT<br>1.1 |        | CTION                                    |      |

|    | 1.2        |        | Memory                                   |      |

|    | 1.2        | 1.2.1  | Capacity Misses                          |      |

|    |            | 1.2.2  | Conflict Misses                          |      |

|    |            | 1.2.3  | Line Fetch Overhead                      |      |

|    | 1.3        | Previo | ous Work                                 | . 8  |

| 2  | HIG        | H LEV  | EL PROFILING AND SIMULATION              | . 10 |

|    | 2.1        | IMPA   | CT Compiler                              | . 10 |

|    |            | 2.1.1  | Overview                                 |      |

|    |            | 2.1.2  | Pcode Overview                           |      |

|    | 2.2        |        | Profiling                                |      |

|    | 2.3        |        | Cache Simulation                         |      |

|    | 2.4        | 1      | iments                                   |      |

|    |            | 2.4.1  | Cache Size                               |      |

|    |            | 2.4.2  | Set Associativity                        |      |

|    |            | 2.4.3  | Line Size                                | . 24 |

| 3  | LOC        | P BLC  | OCKING                                   | . 27 |

|    | 3.1        | Metho  | d                                        | . 27 |

|    | 3.2        | Compi  | iler Support                             |      |

|    |            | 3.2.1  | Validity Analysis                        |      |

|    |            | 3.2.2  | Blocking Decision                        |      |

|    |            | 3.2.3  | Code Transformation                      |      |

|    | 3.3        | -      | imental Evaluation                       |      |

|    |            | 3.3.1  | Statistics for Loop Blocking             |      |

|    |            | 3.3.2  | Cache Miss Ratios for Blocked Loop Nests | . 32 |

| 4  | DAT        | A REL  | OCATION AND PREFETCHING                  | . 35 |

|    | 4.1        | Metho  | d                                        | . 35 |

|    | 4.2        | Archit | ectural Support                          | . 38 |

|    |            | 4.2.1  | Precollect                               |      |

|    |            | 4.2.2  | Distribute                               |      |

|    |            | 4.2.3  | Preallocate                              |      |

|    |            | 4.2.4  | Await                                    | . 41 |

|   |     | 4.2.5  | Finishup                                              |

|---|-----|--------|-------------------------------------------------------|

|   | 4.3 |        | vare Support                                          |

|   | 4.4 | Comp   | iler Support                                          |

|   |     | 4.4.1  | Loop Analysis                                         |

|   |     | 4.4.2  | Array Analysis                                        |

|   |     | 4.4.3  | High-level Code Transformation                        |

|   |     | 4.4.4  | Low Level Code Transformations                        |

| 5 | EXF | PERIMI | ENTAL EVALUATION                                      |

|   | 5.1 |        | dology                                                |

|   |     | 5.1.1  | Compiler Transformation Statistics                    |

|   |     | 5.1.2  | Transformation Correctness Verification via Emulation |

|   |     | 5.1.3  | Simulation Experiments                                |

|   | 5.2 | Exper  | imental Results                                       |

|   |     | 5.2.1  | Individual Loop Nest Results                          |

|   |     | 5.2.2  | Entire Benchmark Results                              |

|   |     | 5.2.3  | Effect of <i>DRP</i> for Write Accesses               |

|   |     | 5.2.4  | Effect of Write Buffer Size                           |

|   |     | 5.2.5  | Effect of Priority of <i>Precollect</i> Operation     |

|   |     | 5.2.6  | Effect of Distribute Operation                        |

|   |     | 5.2.7  | Comparison with Larger Caches                         |

| 6 | CON | NCLUS  | IONS                                                  |

|   | 6.1 | Summ   | ary                                                   |

|   | 6.2 | Future | e Research                                            |

|   | REF | EREN   | CES                                                   |

|   | VIT | Δ      | 111                                                   |

# LIST OF TABLES

| Tab | le                                                                         | Page |

|-----|----------------------------------------------------------------------------|------|

| 2.1 | Static Loop Information for PERFECT and SPEC                               | 14   |

| 2.2 | Loop Invocation Counts of PERFECT and SPEC                                 | 17   |

| 2.3 | Loop Iteration Counts of PERFECT and SPEC                                  | 18   |

| 2.4 | Loop Increments for PERFECT and SPEC                                       | 19   |

| 2.5 | Array Accesses of Each Loop Type of Several Benchmarks                     | 21   |

| 2.6 | Array Access Statistics for Several Benchmarks                             | 22   |

| 3.1 | Blockable Loops for PERFECT Benchmarks                                     | 32   |

| 3.2 | Blocked Loop Nests for PERFECT Benchmarks                                  | 33   |

| 3.3 | Array Access Counts of PERFECT                                             | 33   |

| 3.4 | Motivation for a More Aggressive Method                                    | 34   |

| 5.1 | Inner-most Loops Excluded by Static Loop Characteristics                   | 70   |

| 5.2 | Results of Static Array Reference and Dynamic Loop Iteration Count Analyse | s 71 |

| 5.3 | Results of Effectiveness Analyses for <i>DRP</i> -transformed Loops        | 73   |

| 5.4 | Instruction Latencies for Simulation Experiments                           | 75   |

| 5.5 | Array Information of Transformed Loop Nests                                | 78   |

| 5.6 | Statistics of $DRP$ -transformed Entire Benchmark                          | 85   |

# LIST OF FIGURES

| Figu                                 | Pa                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | g€                                                                                     |

|--------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------|

| 1.1<br>1.2<br>1.3<br>1.4<br>1.5      | Capacity Misses Due to Large Working Set Capacity Misses Due to Non-Sequential Accesses Intra-array Conflict Misses Inter-array Conflict Misses Cache Line Fetch Overhead Due to Non-Sequential Accesses                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 5<br>6<br>7<br>7<br>8                                                                  |

| 2.1<br>2.2<br>2.3<br>2.4             | Effect of Cache Size on Cache Miss Ratios                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 11<br>24<br>25<br>26                                                                   |

| 3.1<br>3.2<br>3.3<br>3.4             | Code Transformation for Loop Blocking                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 27<br>31<br>33<br>34                                                                   |

| 4.13<br>4.14<br>4.15<br>4.16<br>4.17 | Example of Preallocate Operation  Data Relocation and Prefetch Unit Interfaces  Data Relocation and Prefetch Unit Data Path  Relationships of Iteration Variables in Blocked Loop  Iteration Space in Blocked Loop  Example of Shared Relocation Buffer  Example of Forwarded Relocation Buffer  Example of Application of DRP to All Array Accesses Except Last Stores  Declaration of New Variables for DRP  Strip-mining Transformation  Insertion of Operation for DRP  Replacement of Array References for DRP  Software Pipelining for DRP  Loop Unrolling Transformation for DRP  Loop Peeling Transformation for DRP  Machine Level Instructions for Each DRP Operation | 37<br>40<br>43<br>44<br>49<br>50<br>51<br>52<br>54<br>57<br>60<br>61<br>62<br>64<br>66 |

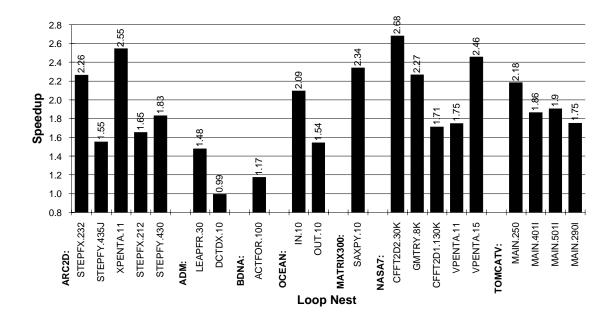

| <ul><li>4.18</li><li>5.1</li></ul>   | Speedup of the $DRP$ -transformed Code Over the Original Code for the Loop                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 68<br>79                                                                               |

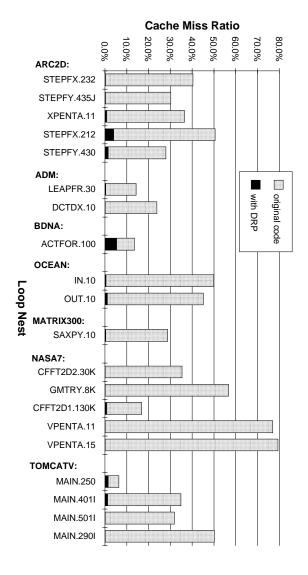

| 5.2  | Cache Miss Ratios of the <i>DRP</i> -transformed Code and the Original Code for   |

|------|-----------------------------------------------------------------------------------|

|      | Loop Nests                                                                        |

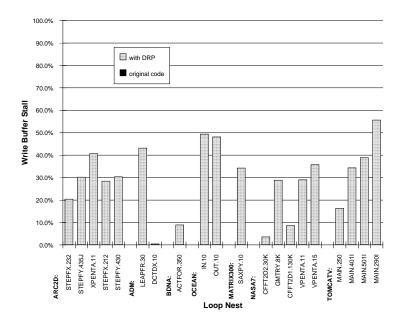

| 5.3  | Stalls Due to the Full Write Buffer                                               |

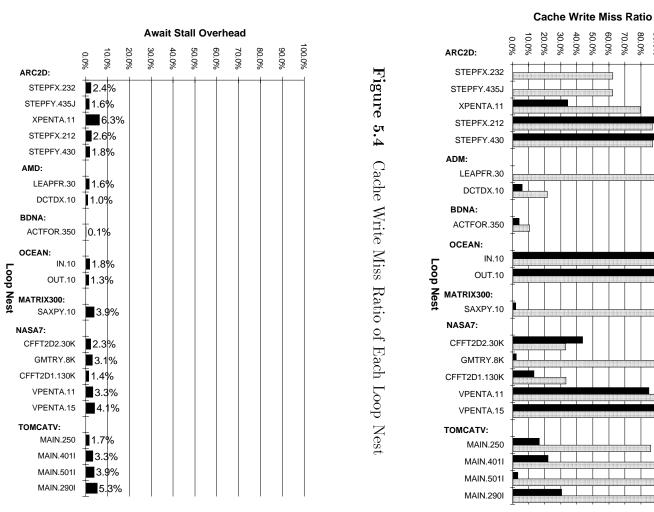

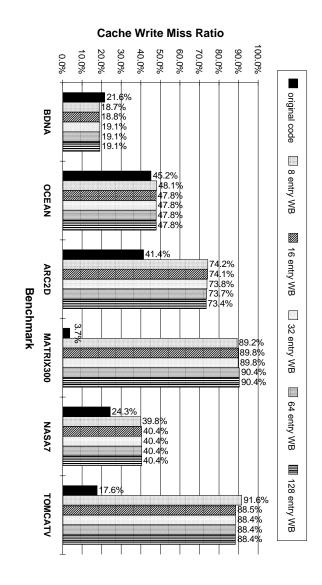

| 5.4  | Cache Write Miss Ratio of Each Loop Nest                                          |

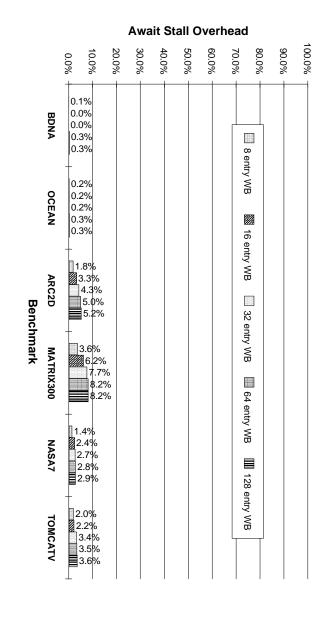

| 5.5  | Await Stall Overhead for the DRP-transformed Code and the Original Code           |

|      | for Loop Nests                                                                    |

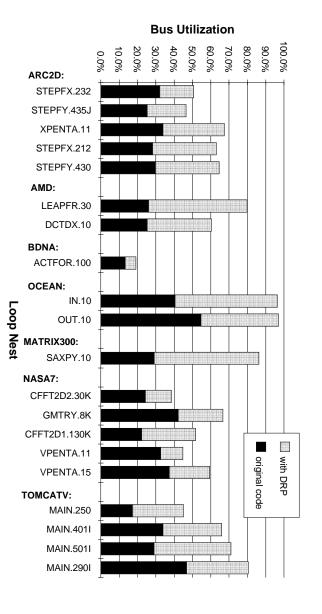

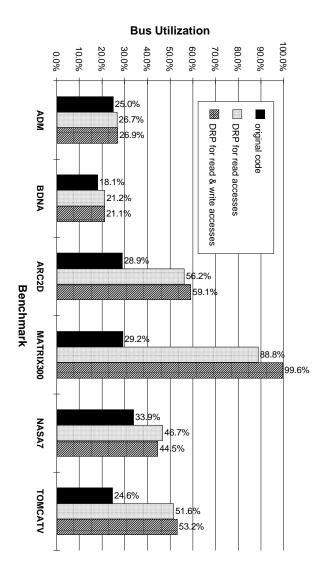

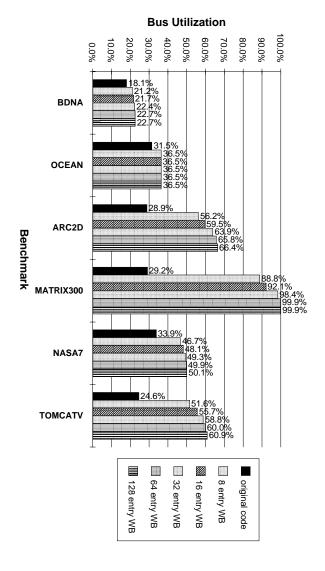

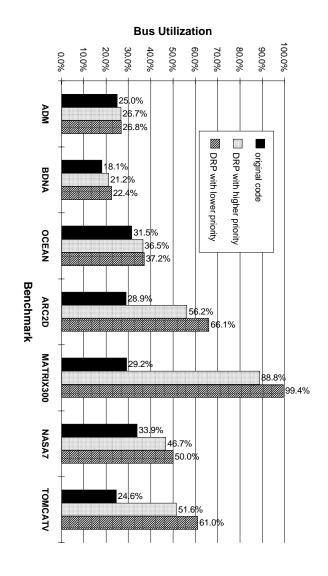

| 5.6  | Bus Utilization for the $DRP$ -transformed Code and the Original Code for         |

|      | Loop Nests                                                                        |

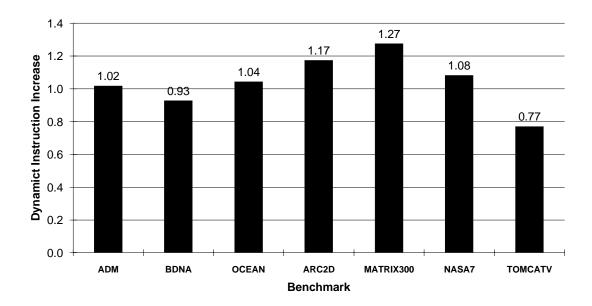

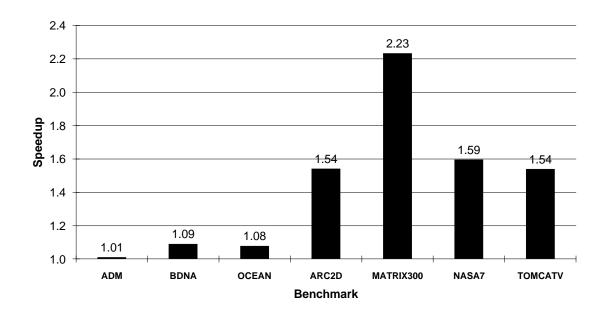

| 5.7  | Instruction Overhead of $DRP$ -transformed Code Over the Original Code 86         |

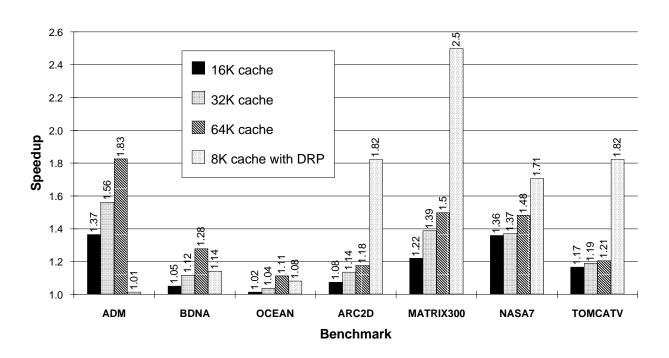

| 5.8  | Speedup of <i>DRP</i> -transformed Code Over the Original Code                    |

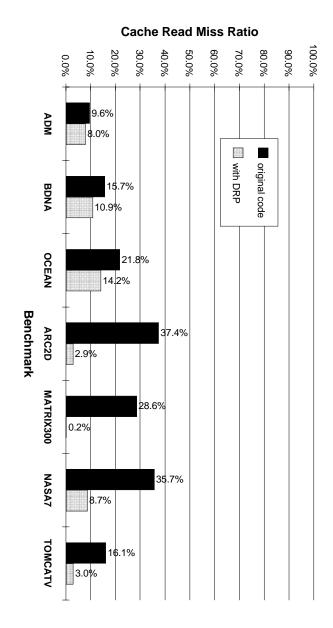

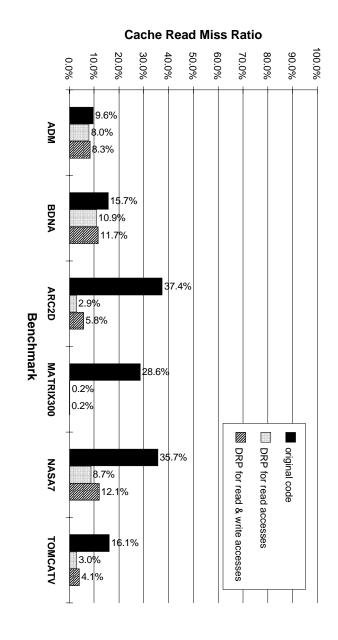

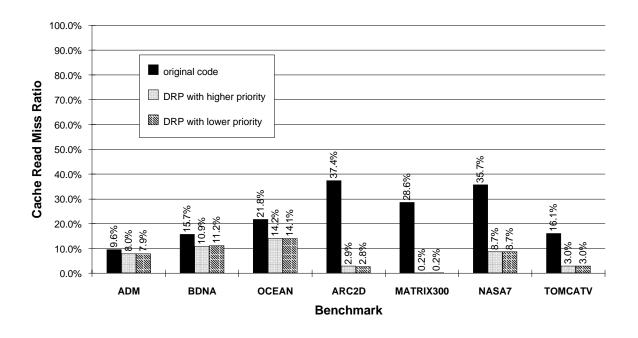

| 5.9  | Cache Read Miss Ratio for Original Code and <i>DRP</i> -transformed Code 88       |

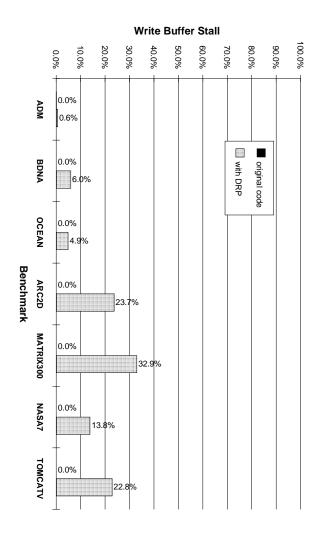

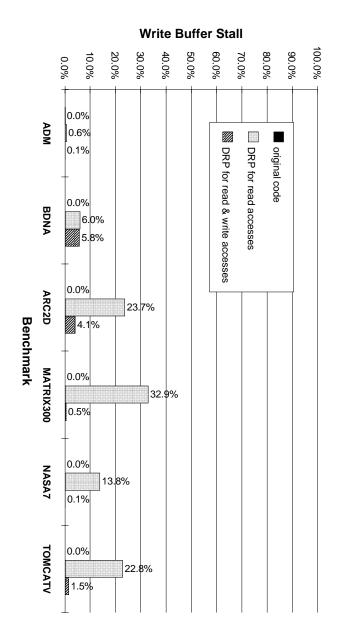

| 5.10 | Stalls Due to the Full Write Buffer for Original Code and DRP-transformed         |

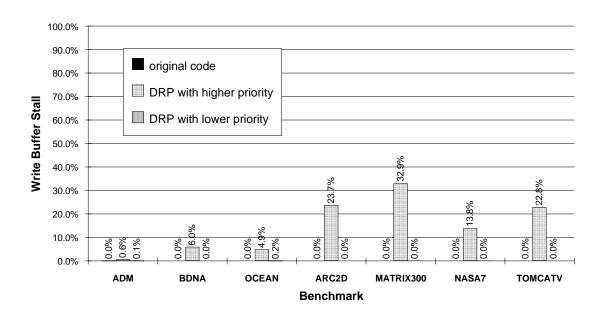

|      | Code                                                                              |

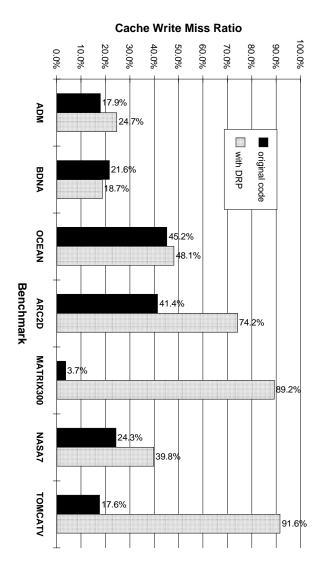

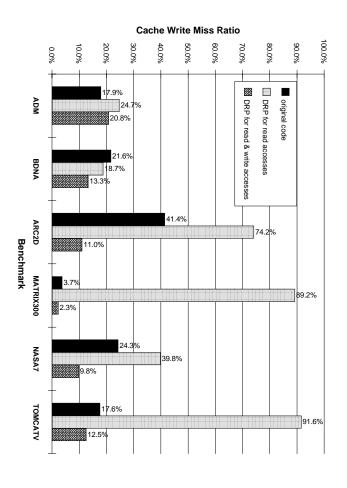

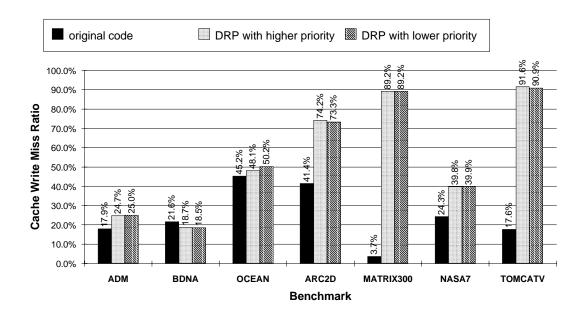

| 5.11 | Data Cache Write Miss Ratio for Original Code and <i>DRP</i> -transformed Code 89 |

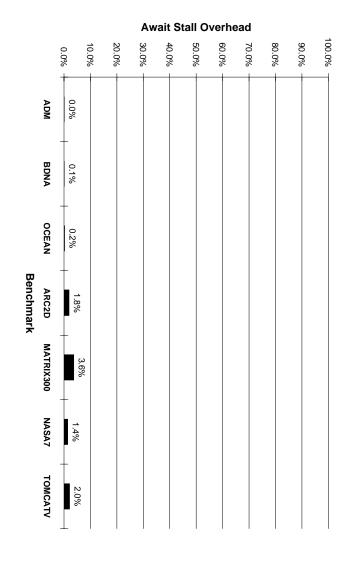

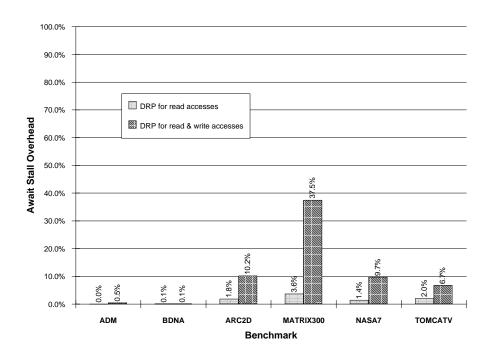

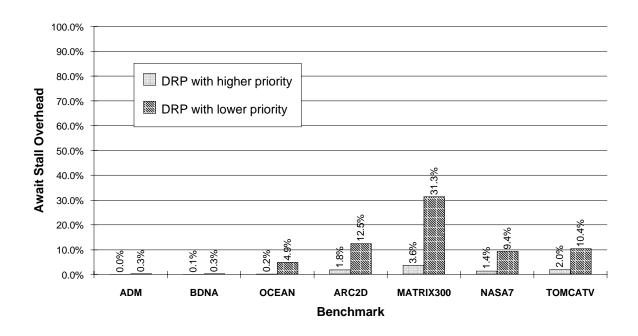

| 5.12 | Await Stall Overhead for DRP-transformed Code                                     |

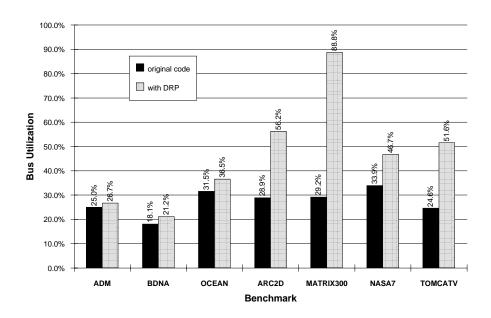

| 5.13 | Bus Utilization for the $DRP$ -transformed Code and the Original Code 91          |

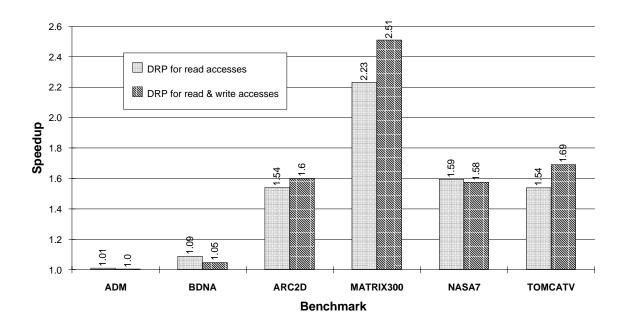

|      | Effect of $DRP$ for Write Accesses on Speedup                                     |

|      | Effect of <i>DRP</i> for Write Accesses on Cache Read Miss                        |

|      | Effect of <i>DRP</i> for Write Accesses on Write Buffer Stall                     |

| 5.17 | Effect of <i>DRP</i> for Write Accesses on Cache Write Miss                       |

| 5.18 | Effect of <i>DRP</i> for Write Accesses on <i>Await</i> Stall Overhead 95         |

| 5.19 | Effect of <i>DRP</i> for Write Accesses on Bus Utilization                        |

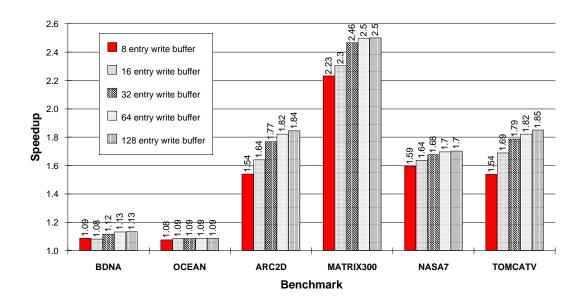

| 5.20 | Effect of Write Buffer Size on Speedup                                            |

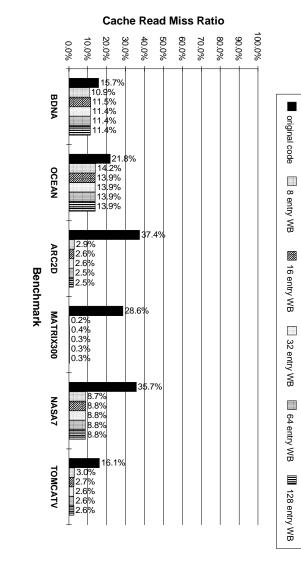

|      | Effect of Write Buffer Size on Cache Read Miss                                    |

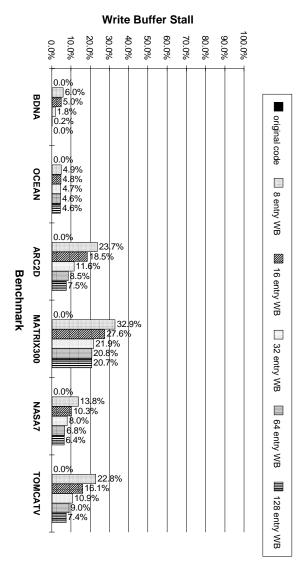

| 5.22 | Effect of Write Buffer Size on Write Buffer Stall                                 |

| 5.23 | Effect of Write Buffer Size on Cache Write Miss                                   |

|      | Effect of Write Buffer Size on Await Stall Overhead                               |

|      | Effect of Write Buffer Size on Bus Utilization                                    |

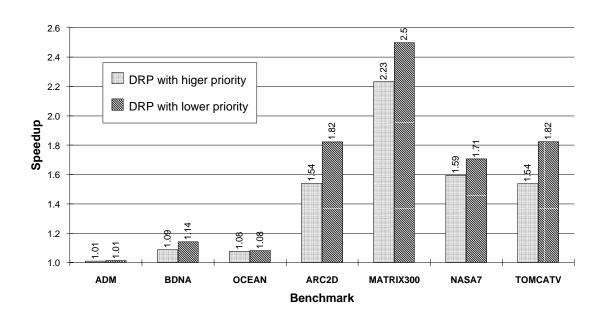

|      | Effect of Priority of <i>Precollect</i> Operation on Speedup                      |

|      | Effect of Priority of <i>Precollect</i> Operation on Cache Read Miss              |

|      | Effect of Priority of <i>Precollect</i> Operation on Write Buffer Stalls 103      |

|      | Effect of Priority of <i>Precollect</i> Operation on Cache Write Miss             |

|      | Effect of Priority of <i>Precollect</i> Operation on Await Stall                  |

|      | Effect of Priority of <i>Precollect</i> Operation on Bus Utilization              |

| 5.32 | Comparison of Speedup by $DRP$ with Larger Caches                                 |

## CHAPTER 1

#### INTRODUCTION

## 1.1 Overview

Numerical applications frequently contain nested loop structures that process large arrays. The execution of these loop structures has been shown to produce memory reference patterns that poorly utilize data caches [3][4]. At least three problems have been identified as the cause of poor cache utilization. The first problem involves an insufficient capacity of the cache: The data accessed by each loop may exceed the cache size, resulting in cache misses. Limited associativity of the cache leads to a second problem: accesses to different arrays, or even to different elements of a single array, may conflict. The third problem involves non-unit stride access patterns that can cause low utilization of cache lines and wasted bus and memory cycles [5].

Potentially, one could use a larger cache size and higher cache associativity to eliminate cache capacity misses and cache conflict misses. This brute force approach, however, does not scale well with the rapidly increasing amount of data used in sophisticated numerical applications. Moreover, it would result in significant hardware cost and increased cache access latency, both of which could be avoided via the more cost-effective approach proposed in this research.

The use of loop blocking transformations could reduce the working-set size of data accessed in loop nests [4] [1] [6]. By reordering the execution of iterations, loop blocking transformations reduce the amount of data referenced between two references to the same datum. Once the data accessed between two references to the same datum is reduced to an amount smaller than the cache size, capacity misses are eliminated. In practice, however, loop blocking transformations may not reduce cache misses because of cache mapping conflicts. Additionally, blocking alone does not reduce the working-set size of data accessed in single loops since the data accesses are not reordered.

Data prefetching has also been proposed to reduce cache misses by fetching data into the cache before it is referenced [7] [8]. When used in conjunction with small cache-block sizes, one can potentially eliminate the problem of low utilization of cache blocks and wasted bus cycles [5]. However, data prefetching may increase the size of the working set, introducing capacity misses. Also, prefetched data may conflict with the current working set in the cache, introducing more conflict misses [9] [10]. In order for data prefetching to improve performance in a reliable manner, one must ensure that both current and future working sets can fit into the cache. The proposed approach achieves this goal by compressing the current and future working sets into a localized region in the virtual address space such that no cache mapping conflicts exist among locations in the region.

This thesis research introduces an approach to solve all three cache performance problems for array-based applications, rather than a solving these problems singly. The first phase in this technique consists of strip-mining inner loops to reduce the number of array accesses in the working set. In the second phase, the insertion of special hardware

instructions compress the working set into a localized region in the virtual address space and prefetch the compressed working set into the cache. The compiler also modifies the working set accesses so that all references will be made to the compressed data in the cache. Since array data are compressed in the localized region, most conflict misses are eliminated. Also, if the original data access pattern is of non-unit stride, unused data are not brought into the cache during compression and prefetch, resulting in improved cacheline utilization. After the computation is completed, additional instructions decompress the modified data and relocate it back to the original program arrays.

In order to minimize the overhead of compressing and decompressing data, compression is performed as the data is prefetched from the memory into the cache. Also, through the use of compiler transformations, compression and prefetching of the next working set is overlapped with the computation for the current working set in order to hide the latency of the relocation.

Using a prototype compiler, an emulation tool, and a simulation tool, I show that this extension to the cache and processor architecture along with the requisite compiler support greatly improves the data cache performance for array-based applications.

# 1.2 Cache Memory

A cache memory is a small, fast memory located to close to the CPU that holds the most recently accessed code or data. Accessing a cache takes much less time than accessing main memory due to the property that *smaller is faster*, which means that the cache is smaller and can be made faster than the large main memory. The cache can hold data that will be accessed in the near future due to the property of *locality of reference*.

There are several objectives in the design of a cache. The most important objective is generally the high hit ratio, which is a measure of the likelihood that the cache contains the requested data in it. Another important objective is to achieve fast access time, which is determined by the hardware complexity. Also, it should be as small as possible while maintaining the desired hit ratio. The degree to which these objectives are achieved depends on not only the cache structure but also the characteristics of the targeted program. For example, the cache performance of an array-oriented program is likely different from that of a scalar-oriented program. Supercomputer applications, especially, have many loops that access large arrays. These array accesses are classified into two categories: sequential accesses and no-sequential accesses. Non-sequential accesses occur:

• when elements of an array are accessed by column,

• when the stride of the access is larger than one,

• or when different arrays are accessed in turn.

These characteristics of numerical programs introduce some inefficiency cache as shown in Section 1.2.1 - 1.2.3.

```

- Direct mapped cache (size:4 words, line size:2 words)

- Working set={A[0],A[1],A[2],A[3],A[4],A[5],A[6],A[7]}

Access A[0]: Miss

A[4]

A[5]

Access A[1]: Hit

Access A[2]: Miss

A[0]

A[1]

Access A[3]: Hit

Access A[4]: Miss, purge A[0], A[1]

A[2]

A[3]

Access A[5]: Hit

Access A[6]: Miss, purge A[2], A[3]

Access A[7]: Hit

A[6]

A[7]

Access A[0]: Miss,purge A[4],A[5]

A[0]

A[1]

Access A[1]: Hit

Access A[2]: Miss, purge A[6], A[7]

Access A[3]: Hit

A[4]

A[5]

A[6]

A[7]

- Every element of working set is purged

- Only the second element in the cache line can hit

- Miss rate = 0.5

A[2]

A[3]

```

Figure 1.1 Capacity Misses Due to Large Working Set

#### 1.2.1 Capacity Misses

If the cache cannot hold all data needed during the execution of a program, capacity misses will occur due to data being purged and later referenced. In general, numerical programs use large working sets, resulting in frequent capacity misses. This concept is illustrated in Figure 1.1. In this case, the capacity misses comes from an actual lack of cache capacity.

Non-sequential access, another characteristic of numerical programs, may also introduce capacity misses, as shown in Figure 1.2. These capacity misses do not result wholly from a lack of cache capacity, but rather the underutilization of the cache.

```

- Direct mapped cache (size: 4 words, line size: 2 words)

- Array size = 4 \times 2

A[2][0]

- Working set = {A[0][0], A[1][0], A[2][0], A[3][0]}

A[0][0]

Access A[0][0]: Miss

Access A[1][0]: Miss

A[1][0]

Access A[2][0]: Miss, purge A[0][0]

Access A[3][0]: Miss, purge A[1][0]

A[3][0]

A[0][0]

Access A[0][0]: Miss, purge A[2][0]

Access A[1][0]: Miss, purge A[3][0]

A[2][0]

- Every element in working set is purged

A[3][0]

- Miss rate = 1.0

- Only 50% utilization of cache

A[1][0]

```

Figure 1.2 Capacity Misses Due to Non-Sequential Accesses

#### 1.2.2 Conflict Misses

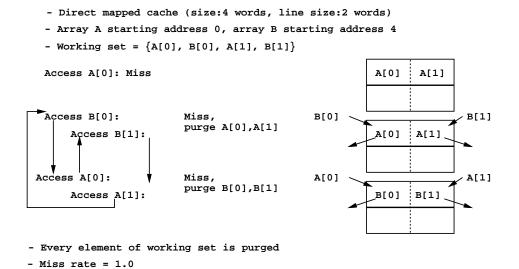

If too many cache lines are mapped to a set in the cache, conflict misses will occur due to lines being purged and later referenced. Non-unit stride accesses in an array introduce conflict misses as shown in Figure 1.3. Unlike capacity misses, conflict misses will occur even though unused cache lines exist in the cache. Conflict misses also occur when different arrays are accessed in turn and the elements map to the same set (Figure 1.4).

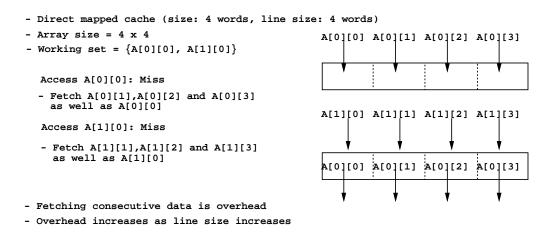

#### 1.2.3 Line Fetch Overhead

Another problem due to non-sequential accesses is line fetch overhead. In general, the cache line size is larger than one word. When an element of an array is brought into the cache, consecutive elements are also fetched into the same cache line. If the array accesses have non-unit stride, the consecutive elements that were fetched in cache are

```

- Direct mapped cache (size: 4 words, line size: 2 words)

- Array size = 4 x 4

- Working set = {A[0][0], A[1][0]}

Access A[0][0]: Miss

Access A[1][0]: Miss, purge A[0][0]

Access A[0][0]: Miss, purge A[1][0]

- Every element in working set is purged

- Miss rate = 1.0

```

Figure 1.3 Intra-array Conflict Misses

Figure 1.4 Inter-array Conflict Misses

unlikely to be used in near future. Thus, fetching the consecutive elements is considered as overhead, not useful work (Figure 1.5).

Figure 1.5 Cache Line Fetch Overhead Due to Non-Sequential Accesses

#### 1.3 Previous Work

- Only 25% utilization of cache

A technique called data copying has been proposed and investigated in order to reduce the cache conflict misses [1][2]. Data copying, however is beneficial only if the performance improvement outweighes the overhead of copying by reusing the data many times. The overhead of copying data from array to array is significant in general. Our proposed method, data relocation and prefetching, has the same benefits as data copying while reducing the overhead of copying. Furthermore, unlike data copying, data relocation and prefetching relocates data into the cache during prefetching, which minimizes the overhead of the relocation. Gather and Scatter operations for vector machines are used in the Cray-1 [11] in order to handle non-unit stride data effectively. In the Cray-1, the array elements are "gathered" from memory into the vector registers before performing vector operations, and "scattered" back to memory after the vector operations are complete. However, the hardware necessary to support data relocation and prefetching would be much easier to add to an existing processor than the hardware to support vectorization.

## CHAPTER 2

## HIGH LEVEL PROFILING AND SIMULATION

In general, profiling information is very useful for code transformation and optimization [12][13]. This chapter describes a high-level profiling tool for loop iteration analysis and array reference analysis. The statistics of the profiled results for some benchmarks are also described. Finally, high-level cache simulation is described with some results to motivate data relocation and prefetching.

# 2.1 IMPACT Compiler

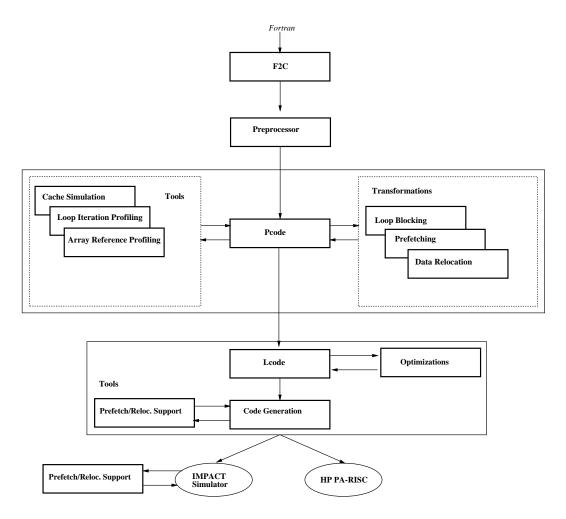

The high-level profiling and simulation have been implemented in IMPACT compiler [17], which is a research-oriented proto-type C compiler.

#### 2.1.1 Overview

Figure 2.1 is an overview of the IMPACT C compiler. FORTRAN programs are first translated into C by f2c before being compiled by IMPACT. The C program is then parsed, semantically analyzed, and translated into Pcode. Dependence analysis and high-level transformations are done in Pcode. After all transformations and optimizations are performed at the high level, Pcode is translated into Lcode, where low-level optimizations are performed. The code generator converts the Lcode into the assembly language of the

Figure 2.1 An Overview of the IMPACT C Compiler

target machine using a machine specification. The IMPACT C compiler generates code for several existing processor architectures: Sun SPARC, HP PA-RISC, AMD29k and Intel X86.

#### 2.1.2 Pcode Overview

Pcode is the intermediate format which represents C programs. High-level transformations and optimizations are performed at the Pcode level. The restructuring process at the Pcode level consists of the following steps:

- (1) Read the source code into the Pcode intermediate representation. The for, while and do loops in the source are read into the Ser\_loop statement structure.

- (2) Dependence analysis and transformations can be performed on for loops that meet the following criteria:

- Loops with simple header expressions,

- Loops with scalar iteration variables,

- Loops nested up to six levels deep,

- Loops that have non-negative integer constant increment expressions,

- Loops that are natural loops (have only one entry point).

These loops are identified and their representation is changed from a  $Ser\_loop$  to a  $Par\_loop$  data structure.

- (3) Loop summary information is calculated for each loop nest. Since dependence analysis is performed only on  $Par\_loops$ , the loop summary information is used to check if all the loops for which dependence information is needed to perform a given transformation are  $Par\_loops$ . Transforming a loop nest without this test could be semantically incorrect since the dependence information for such a loop nest is incomplete.

- (4) Dependence analysis for scalar and array references is performed on all the loop nests in each function and the information is maintained in an auxiliary data structure. Currently, the dependences across loop nests are not calculated since this

information is not needed by the transformations. The dependence analyzer uses the Omega test [14][15] to compute dependence direction and distance vectors for array references, which is an algorithm based on an extension of Fourier-Motzkin variable elimination to integer programming. An extended data flow algorithm is used to compute loop-carried dependence information for scalars.

(5) Each transformation uses the dependence information to determine validity. The transformations are performed in the order specified by the user of the IMPACT compiler.

Table 2.1 shows some static loop information. The benchmarks are selected from the PERFECT [16], SPEC'89 and SPEC'92 benchmark suits. In these benchmarks, most for loops are transformed into Par\_loops. A few for loops are not transformed into Par\_loops since the header expression are complex. In the Table 2.1, the Par\_loops are classified into two types: Outer and Innermost. An Outer Par\_loop is one that has one or more loops nested within it. An Innermost Par\_loop is one that has no loops nested within it.

# 2.2 Pcode Profiling

Some profile information such as loop iteration counts is very important in order to make the transformations effective. For example, performance degradation can occur if a loop nest is blocked and the iteration counts is smaller than the transformed blocking size. Also, loop invocation counts can be used to screen the unimportant loops so that the possible code expansion due to the transformation can be minimized. In the IMPACT

| Benchmark | # of      | # of Par loops |       |     |    |    |   |       |  |  |  |  |

|-----------|-----------|----------------|-------|-----|----|----|---|-------|--|--|--|--|

| Name      | Ser_loops | Loop           | 1 0 1 |     |    |    |   | Total |  |  |  |  |

|           |           | Type           | 1     | 2   | 3  | 4  | 5 |       |  |  |  |  |

| ADM       | 1         | Outer          | 75    | 35  | 2  | 2  | 0 | 114   |  |  |  |  |

|           |           | Innermost      | 79    | 67  | 40 | 0  | 2 | 188   |  |  |  |  |

| SPICE     | 5         | Outer          | 27    | 7   | 0  | 0  | 0 | 34    |  |  |  |  |

|           |           | Innermost      | 250   | 49  | 11 | 0  | 0 | 310   |  |  |  |  |

| MGD       | 2         | Outer          | 12    | 4   | 1  | 0  | 0 | 17    |  |  |  |  |

|           |           | Innermost      | 13    | 10  | 11 | 1  | 0 | 35    |  |  |  |  |

| TRACK     | 0         | Outer          | 18    | 8   | 2  | 0  | 0 | 28    |  |  |  |  |

|           |           | Innermost      | 34    | 23  | 7  | 5  | 0 | 69    |  |  |  |  |

| BDNA      | 0         | Outer          | 50    | 6   | 2  | 0  | 0 | 58    |  |  |  |  |

|           |           | Innermost      | 129   | 74  | 7  | 2  | 0 | 212   |  |  |  |  |

| OCEAN     | 9         | Outer          | 42    | 11  | 0  | 0  | 0 | 53    |  |  |  |  |

|           |           | Innermost      | 28    | 39  | 12 | 0  | 0 | 79    |  |  |  |  |

| DYFESM    | 2         | Outer          | 70    | 23  | 6  | 0  | 0 | 99    |  |  |  |  |

|           |           | Innermost      | 68    | 65  | 25 | 7  | 0 | 165   |  |  |  |  |

| ARC2D     | 1         | Outer          | 63    | 20  | 0  | 0  | 0 | 83    |  |  |  |  |

|           |           | Innermost      | 71    | 59  | 20 | 0  | 0 | 150   |  |  |  |  |

| FLO52     | 3         | Outer          | 48    | 22  | 0  | 0  | 0 | 70    |  |  |  |  |

|           |           | Innermost      | 45    | 49  | 24 | 0  | 0 | 118   |  |  |  |  |

| TRFD      | 1         | Outer          | 11    | 13  | 16 | 6  | 0 | 46    |  |  |  |  |

|           |           | Innermost      | 3     | 3   | 6  | 14 | 6 | 32    |  |  |  |  |

| SPEC77    | 0         | Outer          | 98    | 26  | 4  | 0  | 0 | 128   |  |  |  |  |

|           |           | Innermost      | 84    | 150 | 41 | 4  | 0 | 279   |  |  |  |  |

| MATRIX300 | 0         | Outer          | 2     | 0   | 0  | 0  | 0 | 2     |  |  |  |  |

|           |           | Innermost      | 13    | 2   | 0  | 0  | 0 | 15    |  |  |  |  |

| NASA7     | 5         | Outer          | 33    | 17  | 6  | 0  | 0 | 56    |  |  |  |  |

|           |           | Innermost      | 24    | 30  | 13 | 6  | 0 | 73    |  |  |  |  |

| TOMCATV   | 0         | Outer          | 6     | 0   | 0  | 0  | 0 | 6     |  |  |  |  |

|           |           | Innermost      | 6     | 6   | 0  | 0  | 0 | 12    |  |  |  |  |

Table 2.1

Static Loop Information for PERFECT and SPEC

compiler, profiling tools for Lcode have already been implemented. Since a profiling tool for Pcode was unavailable, one has been implemented for my thesis research.

Profiling is the process of selecting a set of inputs for a program, executing the program with these inputs and recording the run-time behavior of the program. The following information is collected by the Pcode profiler.

- (1) The invocation count of each loop nest.

- (2) The initial value, final value and increment value of each loop nest

- (3) The iteration count of each loop nest.

Pcode profiling is supported by three tools: a probe insertion program, an execution monitor and a program to summarize profile information. There are three steps to generate execution profiles:

(1) The probe insertion program assigns a unique identifier or line number to each loop nest and inserts a probe just before the loop nest in Pcode. Whenever the prove is activated, it increments the invocation counter for the associated loop nest. It also produces the initial value, final value and increment value of the loop iteration variable. The probe insertion program also inserts a probe just before the first line in the loop nest to increment the iteration count every time that the body of the loop nest is executed.

- (2) The probed insertion program is reverse-translated into C code. The C code is compiled by a standard C compiler, and linked with the execution monitor program to generate the probed executable program.

- (3) The executable program is executed for a set of inputs, and generated profile information is collected.

- (4) Finally, the average profile data is generated by the program using the profile information and merged back into the Pcode intermediate representation.

Table 2.2 - 2.4 show some dynamic loop information that is summarized from the profile information. Table 2.2 shows how many times each loop was invoked on average at run time for a input. **ADM** and **SPICE** have many loops that are never invoked at run time by the input used. **SPICE**, **BDNA**, **MATRIX300** and **TOMCATV** have very small invocation counts for *Outer* loops compared with those for *Innermost* loops.

Table 2.3 shows how many iterations each loop had on average at run time for a input. This information is very important for some transformations such as loop blocking since the blocking size should be smaller than the iteration counts. The last column of the table shows the average iteration counts per invocation. **ADM** and **SPICE** have very small iteration counts for both *Outer* and *Innermost* loops. In most benchmarks, the iteration counts for *Outer* loops are equal to or less than that for *Innermost* loops. However, **MGD** and **TRACK** have larger iteration counts for *Outer* loops than for *Innermost* loops.

| Bench<br>Name | -         |       |     |     |         |      |     |      | A verage<br>Invocation |           |

|---------------|-----------|-------|-----|-----|---------|------|-----|------|------------------------|-----------|

| Name          | туре      | Loops | 0   | 10  | A verag | 1000 | 10K | 100K | More                   | Per Loop  |

| ADM           | Outer     | 114   | 71  | 12  | 2       | 20   | 0   | 6    | 3                      | 19,579    |

|               | Innermost | 188   | 102 | 20  | 7       | 7    | 2   | 37   | 13                     | 58,784    |

| SPICE         | Outer     | 34    | 20  | 9   | 5       | 0    | 0   | 0    | 0                      | 17        |

|               | Innermost | 310   | 240 | 31  | 11      | 22   | 3   | 0    | 3                      | 10,971    |

| MGD           | Outer     | 17    | 5   | 3   | 1       | 6    | 1   | 1    | 0                      | 3,256     |

|               | Innermost | 35    | 5   | 8   | 1       | 5    | 0   | 3    | 13                     | 1,602,565 |

| TRACK         | Outer     | 28    | 5   | 5   | 6       | 4    | 2   | 6    | 0                      | 7,670     |

|               | Innermost | 69    | 12  | 5   | 13      | 8    | 7   | 23   | 1                      | 17,391    |

| BDNA          | Outer     | 58    | 14  | 43  | 1       | 0    | 0   | 0    | 0                      | 2         |

|               | Innermost | 212   | 61  | 113 | 14      | 3    | 21  | 0    | 0                      | 414       |

| OCEAN         | Outer     | 53    | 4   | 16  | 5       | 23   | 4   | 1    | 0                      | 862       |

|               | Innermost | 79    | 7   | 15  | 5       | 19   | 1   | 25   | 7                      | 41,763    |

| DYFESM        | Outer     | 99    | 20  | 42  | 8       | 3    | 17  | 9    | 0                      | 5,486     |

|               | Innermost | 165   | 32  | 65  | 26      | 6    | 12  | 15   | 9                      | 53,996    |

| ARC2D         | Outer     | 83    | 11  | 18  | 0       | 54   | 0   | 0    | 0                      | 144       |

|               | Innermost | 150   | 43  | 10  | 9       | 42   | 19  | 22   | 5                      | 14,533    |

| FLO52         | Outer     | 70    | 9   | 8   | 0       | 23   | 28  | 2    | 0                      | 2,016     |

|               | Innermost | 118   | 11  | 30  | 6       | 9    | 35  | 23   | 4                      | 20,370    |

| TRFD          | Outer     | 46    | 28  | 5   | 0       | 2    | 7   | 4    | 0                      | 16,598    |

|               | Innermost | 32    | 17  | 2   | 0       | 1    | 1   | 7    | 4                      | 478,393   |

| SPEC77        | Outer     | 128   | 11  | 39  | 26      | 6    | 23  | 23   | 0                      | 6,972     |

|               | Innermost | 279   | 20  | 37  | 32      | 49   | 38  | 57   | 46                     | 80,700    |

| MATRIX300     | Outer     | 2     | 0   | 2   | 0       | 0    | 0   | 0    | 0                      | 1         |

|               | Innermost | 15    | 1   | 9   | 0       | 2    | 2   | 0    | 1                      | 51,815    |

| NASA7         | Outer     | 56    | 0   | 19  | 9       | 14   | 4   | 10   | 0                      | 6,142     |

|               | Innermost | 73    | 0   | 13  | 11      | 14   | 10  | 19   | 6                      | 28,927    |

| TOMCATV       | Outer     | 6     | 0   | 1   | 0       | 5    | 0   | 0    | 0                      | 84        |

|               | Innermost | 12    | 1   | 3   | 0       | 3    | 0   | 5    | 0                      | 11,614    |

Table 2.2

Loop Invocation Counts of PERFECT and SPEC

| Bench     | Loop      | # of             |   |    |               | of Loo           |               |           | Average           | Average                 |

|-----------|-----------|------------------|---|----|---------------|------------------|---------------|-----------|-------------------|-------------------------|

| Name      | Туре      | Loops<br>Invoked | 0 | 10 | verage<br>100 | Iteratio<br>1000 | n Coun<br>10K | t<br>More | Iter. Per<br>Loop | Iter. Per<br>Invocation |

| ADM       | Outer     | 43               | 1 | 27 | 15            | 0                | 0             | 0         | 16                | 3                       |

| ADWI      | Innermost | 86               | 0 | 18 | 66            | 2                | 0             | 0         | 44                | 12                      |

| SPICE     | Outer     | 14               | 0 | 7  | 6             | 1                | 0             | 0         | 37                | 4                       |

|           | Innermost | 70               | 0 | 43 | 19            | 8                | 0             | 0         | 31                | 3                       |

| MGD       | Outer     | 12               | 0 | 3  | 0             | 7                | 2             | 0         | 687               | 223                     |

|           | Innermost | 30               | 0 | 16 | 6             | 4                | 3             | 1         | $1,\!141$         | 12                      |

| TRACK     | Outer     | 23               | 0 | 12 | 7             | 4                | 0             | 0         | 95                | 81                      |

|           | Innermost | 57               | 0 | 31 | 15            | 10               | 1             | 0         | 11                | 9                       |

| BDNA      | Outer     | 44               | 0 | 35 | 5             | 1                | 3             | 0         | 126               | 176                     |

|           | Innermost | 151              | 1 | 65 | 19            | 11               | 54            | 1         | 869               | 285                     |

| OCEAN     | Outer     | 49               | 0 | 8  | 29            | 12               | 0             | 0         | 72                | 40                      |

|           | Innermost | 72               | 0 | 0  | 28            | 42               | 2             | 0         | 182               | 169                     |

| DYFESM    | Outer     | 79               | 0 | 68 | 11            | 0                | 0             | 0         | 8                 | 12                      |

|           | Innermost | 133              | 6 | 97 | 28            | 2                | 0             | 0         | 11                | 20                      |

| ARC2D     | Outer     | 72               | 0 | 11 | 44            | 17               | 0             | 0         | 122               | 150                     |

|           | Innermost | 107              | 1 | 0  | 41            | 65               | 0             | 0         | 204               | 154                     |

| FLO52     | Outer     | 61               | 0 | 26 | 34            | 1                | 0             | 0         | 15                | 16                      |

|           | Innermost | 107              | 0 | 4  | 77            | 26               | 0             | 0         | 75                | 58                      |

| TRFD      | Outer     | 18               | 0 | 0  | 16            | 2                | 0             | 0         | 63                | 24                      |

|           | Innermost | 15               | 0 | 1  | 13            | 1                | 0             | 0         | 37                | 21                      |

| SPEC77    | Outer     | 117              | 0 | 31 | 81            | 5                | 0             | 0         | 59                | 13                      |

|           | Innermost | 259              | 0 | 57 | 167           | 34               | 1             | 0         | 153               | 15                      |

| MATRIX300 | Outer     | 2                | 0 | 0  | 0             | 2                | 0             | 0         | 300               | 300                     |

|           | Innermost | 14               | 0 | 1  | 0             | 13               | 0             | 0         | 279               | 300                     |

| NASA7     | Outer     | 56               | 0 | 25 | 14            | 17               | 0             | 0         | 80                | 6                       |

|           | Innermost | 73               | 0 | 10 | 13            | 46               | 3             | 1         | 697               | 190                     |

| TOMCATV   | Outer     | 6                | 0 | 0  | 0             | 6                | 0             | 0         | 255               | 255                     |

|           | Innermost | 11               | 0 | 0  | 0             | 11               | 0             | 0         | 256               | 255                     |

Table 2.3

Loop Iteration Counts of PERFECT and SPEC

| Bench     | Loop      | # of          | N      |     | r of Loop | Average   | Average   |      |            |

|-----------|-----------|---------------|--------|-----|-----------|-----------|-----------|------|------------|

| Name      | Туре      | $_{ m Loops}$ |        |     | ge Increr | Iter. Per | Iter. Per |      |            |

|           |           | Invoked       | 0 to 1 | 1   | 1 to 2    | 2         | More      | Loop | Invocation |

| ADM       | Outer     | 43            | 0      | 43  | 0         | 0         | 0         | 1.00 | 1.00       |

|           | Innermost | 86            | 0      | 83  | 0         | 3         | 0         | 1.03 | 1.17       |

| SPICE     | Outer     | 14            | 0      | 14  | 0         | 0         | 0         | 1.00 | 1.00       |

|           | Innermost | 70            | 0      | 70  | 0         | 0         | 0         | 1.00 | 1.00       |

| MGD       | Outer     | 12            | 0      | 12  | 0         | 0         | 0         | 1.00 | 1.00       |

|           | Innermost | 30            | 0      | 30  | 0         | 0         | 0         | 1.00 | 1.00       |

| TRACK     | Outer     | 23            | 0      | 23  | 0         | 0         | 0         | 1.00 | 1.00       |

|           | Innermost | 57            | 0      | 57  | 0         | 0         | 0         | 1.00 | 1.00       |

| BDNA      | Outer     | 44            | 0      | 44  | 0         | 0         | 0         | 1.00 | 1.00       |

|           | Innermost | 151           | 0      | 151 | 0         | 0         | 0         | 1.00 | 1.00       |

| OCEAN     | Outer     | 49            | 0      | 46  | 0         | 3         | 0         | 1.06 | 1.09       |

|           | Innermost | 72            | 0      | 70  | 0         | 0         | 2         | 1.08 | 1.00       |

| DYFESM    | Outer     | 79            | 0      | 79  | 0         | 0         | 0         | 1.00 | 1.00       |

|           | Innermost | 133           | 0      | 133 | 0         | 0         | 0         | 1.00 | 1.00       |

| ARC2D     | Outer     | 72            | 0      | 72  | 0         | 0         | 0         | 1.00 | 1.00       |

|           | Innermost | 107           | 0      | 107 | 0         | 0         | 0         | 1.00 | 1.00       |

| FLO52     | Outer     | 61            | 0      | 57  | 0         | 4         | 0         | 1.07 | 1.03       |

|           | Innermost | 107           | 0      | 102 | 0         | 5         | 0         | 1.05 | 1.01       |

| TRFD      | Outer     | 18            | 0      | 18  | 0         | 0         | 0         | 1.00 | 1.00       |

|           | Innermost | 15            | 0      | 15  | 0         | 0         | 0         | 1.00 | 1.00       |

| SPEC77    | Outer     | 117           | 0      | 109 | 0         | 6         | 2         | 1.14 | 1.51       |

|           | Innermost | 259           | 0      | 237 | 0         | 22        | 0         | 1.08 | 1.59       |

| MATRIX300 | Outer     | 2             | 0      | 2   | 0         | 0         | 0         | 1.00 | 1.00       |

|           | Innermost | 14            | 0      | 14  | 0         | 0         | 0         | 1.00 | 1.00       |

| NASA7     | Outer     | 56            | 0      | 55  | 0         | 0         | 1         | 1.05 | 1.00       |

|           | Innermost | 73            | 0      | 73  | 0         | 0         | 0         | 1.00 | 1.00       |

| TOMCATV   | Outer     | 6             | 0      | 6   | 0         | 0         | 0         | 1.00 | 1.00       |

|           | Innermost | 11            | 0      | 11  | 0         | 0         | 0         | 1.00 | 1.00       |

Table 2.4

Loop Increments for PERFECT and SPEC

Table 2.4 shows the average increment of each loop. ADM, OCEAN, FLO52, SPEC77 and NASA7 have a few loops whose increment is not one. Especially, SPEC77 has two as the increment in the half of the loop invocations. The increments for all other benchmarks are one.

#### 2.3 Pcode Cache Simulation

In addition to the loop profile information, some cache simulation information is useful to determine whether a loop nest should be transformed or not. Since the purpose of the transformation is to reduce the cache misses, any loop nest with few cache misses should not be transformed in order to avoid the possible performance penalty due to the instruction overhead introduced by the transformation. Simulation is the process of selecting a set of inputs for a program, executing the program with these inputs, and simulating the cache behavior of the program. The following information is simulated by the Pcode cache simulator:

- (1) The cache compulsory misses, capacity misses and conflict misses.

- (2) The cache anti-conflict hits.

Pcode cache simulation is supported by three tools: a probe insertion program, a cache simulator and a program to summarize cache simulation information. There are three steps to perform Pcode cache simulation:

(1) The probe insertion program assigns a unique identifier or line number to each array reference and inserts a probe just before the array reference in Pcode. The probe is inserted only for reads if the cache has does not allocate line when a writemiss occurs. Whenever the prove is activated, it produces the associated memory address and identifier.

| Bench     | Array Acce           | ss in Parloop            | Other Array        | Total Array           |

|-----------|----------------------|--------------------------|--------------------|-----------------------|

| Name      | Outer (%)            | Innermost (%)            | Accesses~(%)       | Access Counts         |

| TRACK     | 17,704,495 (33.4)    | 14,862,168 (28.1)        | 20,412,350 (38.5)  | 52,979,013            |

| BDNA      | 91,292 (0.0)         | 318,842,870 (100.0)      | 833 (0.0)          | 318,934,995           |

| OCEAN     | 1,909,884 (0.1)      | 1,602,459,335 (97.3)     | 42,489,908 (2.6)   | $1,\!646,\!859,\!127$ |

| ARC2D     | 1,441,725 (0.1)      | $1,459,178,576 \ (99.9)$ | 2(0.0)             | $1,\!460,\!620,\!303$ |

| MATRIX300 | 300 (0.0)            | 432,000,000 (100.0)      | 0 (0.0)            | 432,000,300           |

| NASA7     | $1,221,\!370\ (0.1)$ | $2,080,443,485 \ (99.9)$ | $162,\!807\ (0.0)$ | 2,081,827,662         |

| TOMCATV   | 0 (0.0)              | 325,218,099 (100.0)      | 0 (0.0)            | 325,218,099           |

Table 2.5 Array Accesses of Each Loop Type of Several Benchmarks

- (2) The Probed Pcode is reverse-translated into C code. The C code is compiled by a standard C compiler and linked with the cache simulator program.

- (3) The executable program is executed for a set of inputs. The generated cache simulation data for each line is collected.

- (4) Finally, the summary cache simulation information is generated by the program using the cache simulation data for each line. The cache simulation data for each loop nest is also generated using the loop nest information. This information is then merged back into the Pcode representation of the program.

Table 2.5 shows some characteristics of array accesses of several benchmarks. In all benchmarks except **TRACK**, the *Innermost* loops contain the vast majority of the array accesses in the program. The array accesses in **TRACK** occur not only in the *Innermost* loops but also in *Outer* loops and the other regions where the accesses are not within loops.

| Bench     | Loop      | Number of Par_loops |                   |     |      |      |     |  |

|-----------|-----------|---------------------|-------------------|-----|------|------|-----|--|

| Name      | Type      |                     | Array Access Rate |     |      |      |     |  |

|           |           | 0                   | 0.1               | 1.0 | 10.0 | more |     |  |

| TRACK     | Outer     | 3                   | 5                 | 4   | 2    | 1    | 15  |  |

|           | Innermost | 6                   | 15                | 15  | 16   | 0    | 52  |  |

| BDNA      | Outer     | 14                  | 24                | 0   | 0    | 0    | 38  |  |

|           | Innermost | 49                  | 78                | 6   | 4    | 2    | 139 |  |

| OCEAN     | Outer     | 0                   | 8                 | 0   | 0    | 0    | 8   |  |

|           | Innermost | 4                   | 25                | 15  | 11   | 4    | 59  |  |

| ARC2D     | Outer     | 1                   | 14                | 0   | 0    | 0    | 15  |  |

|           | Innermost | 41                  | 50                | 13  | 33   | 0    | 137 |  |

| MATRIX300 | Outer     | 0                   | 1                 | 0   | 0    | 0    | 1   |  |

|           | Innermost | 1                   | 0                 | 0   | 0    | 1    | 2   |  |

| NASA7     | Outer     | 0                   | 15                | 0   | 0    | 0    | 15  |  |

|           | Innermost | 0                   | 20                | 11  | 14   | 3    | 48  |  |

| TOMCATV   | Outer     | 0                   | 0                 | 0   | 0    | 0    | 0   |  |

|           | Innermost | 1                   | 5                 | 0   | 2    | 3    | 11  |  |

Table 2.6 Array Access Statistics for Several Benchmarks

Table 2.6 shows the number of loops with each array access counts for several benchmarks. **BDNA** and **ARC2D** have many loops that do not read from arrays. Also, in **BDNA** a few loops contain the vast majority of the array accesses.

# 2.4 Experiments

The experiments in this section show the effect of the cache structure for numerical programs. Since there exist a lot of possible cache configurations, testing all configurations is impossible with available computer resources and time. To test the effect of a particular cache parameter, a base cache was defined and a single parameter was varied

on each simulation. The selected base cache was a 8K, direct mapped cache with 16 byte cache line, using a write-back and no-allocate-on-write-miss policy.

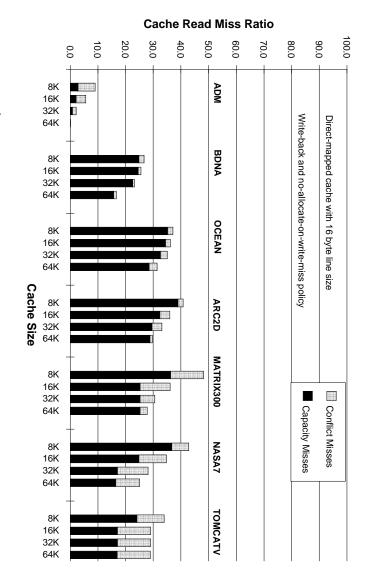

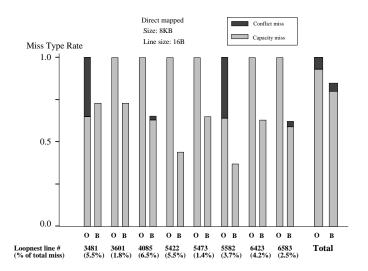

#### 2.4.1 Cache Size

The first cache characteristic is the size. The cache simulations examined the effects of increasing cache size from 8K to 64K bytes. As shown in Figure 2.2, for all the benchmarks, the total cache misses as well as the cache capacity misses decreased as the data cache size increased. The cache conflict misses not necessarily decreased as the cache size increased since the conflict misses come from the lack of the cache line associativity, not directly from the lack of the cache size. Regarding the capacity misses, increasing the cache size decrease the cache capacity misses in the most cases. For **TOMCATV**, however, doubling the cache size from 16K did not decrease the cache capacity misses as well as the total cache misses. This may happens if the working set size is larger than the cache size. Cache size does not affect the cache line overhead.

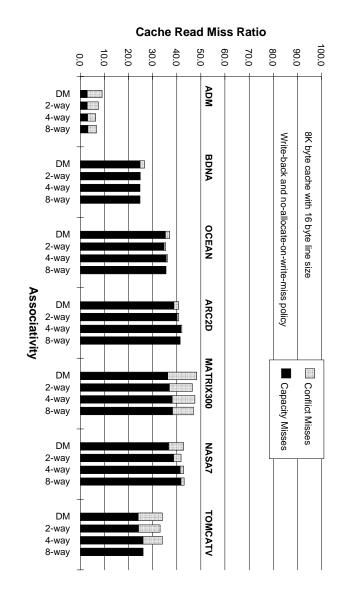

# 2.4.2 Set Associativity

The second cache parameter examined was set associativity. The cache simulations examined the effects of increasing set associativity from direct-mapped to 8-way set. As shown in Figure 2.3, for most benchmarks, the total cache misses did not necessarily decrease as the set associativity increased. Although increasing the set associativity can decreases the cache conflict misses in almost all cases, it increases the capacity misses

Figure 2.2 Effect of Cache Size on Cache Miss Ratios

instead. The improvement of the conflict misses is easily canceled by the increase of the capacity misses. Like cache size, set associativity does not affect the cache line overhead

of the data register can be just ignored. cache into a data register while comparing the tag. If the tag is not matched, the content mapped cache is much faster than a set associative cache since it can fetch the data from the tags. Also, the extra hardware may slow down the cache speed. Especially, a direct-In general, the cache with higher set associativity need more hardware to compare

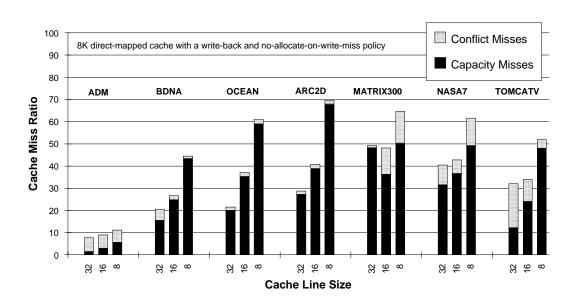

# 2.4.3 Line Size

examined the effects of increasing cache line from 32 to 8 bytes as shown in Figure 2.4. The third cache parameter examined was cache line size. The cache simulations

Figure 2.3 Effect of Set Associativity on Cache Miss Ratios

significant increase of the cache misses due to the small cache line. line can effectively decrease the cache line fetch, the advantage is easily cancelled by the line cannot take the advantage of the locality of the reference. Although smaller cache Overall, decreasing the cache line size increases the cache misses since smaller cache

Figure 2.4 Effect of Cache Line Size on Cache Miss Ratios

## CHAPTER 3

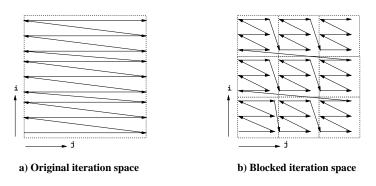

## LOOP BLOCKING

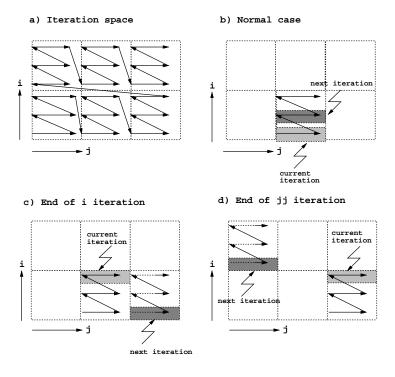

Loop blocking is an optimization technique to increase the chance for data reuse in the cache. The basic idea is to reduce the number of accesses between two accesses to the same datum. In this method, as illustrated in Figure 3.1, a large iteration space (Figure 3.1a) is divided into smaller sub-iteration spaces (Figure 3.1b) so that the array accesses that occur within each sub-iteration space can fit within the cache. This more localized memory reference pattern can increase data reuse within the cache and reduce processor stalls due to cache misses.

## 3.1 Method

The original program is transformed in order to divide the iteration space of loops into smaller sub-iteration spaces. Using this method, no special hardware is necessary at run-

Figure 3.1 Concept of Loop Blocking

time. Instead, a sophisticated compiler is essential to perform the blocking transformation

correctly and effectively. The compiler need identify the following:

• the loop nests that are valid to block.

• the loop nests that should be blocked to improve cache performance.

• the blocking size that should be used to improve cache performance effectively.

The automatic blocking transformation has been implemented as one of the transfor-

mations for the IMPACT compiler.

3.2 Compiler Support

The loop blocking transformation consists of three phases:

• Phase 1: Validity Analysis

• Phase 2: Blocking Decision

• Phase 3: Code Transformation

3.2.1Validity Analysis

Validity analysis is done as the first phase in order to confirm that the blocking trans-

formation is valid, which means that the result of the computation after the blocking

transformation is exactly the same as that before the transformation. In the current im-

plementation, only perfectly nested and structured loops are considered as the candidate

28

for loop blocking. Loop nests that contain multiple inner loops, return, goto, or break statements are excluded, as well as which contain subroutine calls with possible side effects. Then, for the remaining loop nests, the dependence analysis checks the validity of loop blocking.

The dependence analysis and the criteria for loop blocking are same as those for the loop interchange. Loop blocking is an iteration space reordering transformation, and therefore, may reverse dependence directions. Therefore, the dependence direction vector can be used to check whether or not a loop nest can be legally blocked. If the dependence direction vectors for the transformed loop nest are not lexically positive, the transformation will be invalid. The dependence analyzer used by my implementation is a version of the Omega test tailored to IMPACT by Grant Haab.

## 3.2.2 Blocking Decision

In the second phase of loop blocking, a fast compile time cache simulation is done in order to determine the effective blocking size. In the current implementation, the address of each array reference is calculated by a fast approximate method which uses a constant number for the size of each array dimension and the coefficient of each loop iteration variable in the array subscript. Therefore, the loop nests which contain arrays whose subscripts include variables other than loop iteration variables are excluded. Furthermore, the starting address of the array itself is very hard or impossible to determine at compile time; thus, some approximation is necessary in order to perform cache simulation at compile time.

Using a given cache size, the simulator estimates the cache misses for a blocked loop nest, starting from the smallest blocking size or one. Then, the blocking size is expanded in each dimension. In order to speedup the blocking size determination, each dimension for which blocking is to be applied is expanded by factors of power of 2 (i.e. 2, 4, 8, 16 and so on). Then, the cache miss ratio for each expanded blocking size is estimated. The blocking size with the lowest miss ratio among the expanded blocked loop nests is picked. This expansion process is repeated until the blocking size is expanded a predefined number of times. If the estimated cache misses for the finally selected blocking size is less than a predefined threshold, use this blocking size for the transformation. Otherwise, this loop nest is not blocked. Thus, the computational complexity of the algorithm is O(DlogN), where D is the number of dimensions and N is the number of iterations in each dimension.

#### 3.2.3 Code Transformation

As the final phase of the blocking transformation, the loop nest is actually modified into the blocked loop nest with the blocking size determined by the previous phase.

A doubly-nested loop is given as an example in Figure 3.2a. The accesses to array B are sequential within each row, while the accesses to array C are sequential within each column, causing low utilization of the cache storage. The loop nesting after the blocking transformation is shown in Figure 3.2b.

Figure 3.2 Code Transformation for Loop Blocking

# 3.3 Experimental Evaluation

In this section, the cache miss ratio of the loop blocking are evaluated through cache simulations.

## 3.3.1 Statistics for Loop Blocking

Table 3.1 shows the statistics of blockable loops of several PERFECT benchmarks. As described in Section 3.2.1, unstructured loops, imperfectly nested loops and loops that contain calls with possible side effects are excluded. Then, dependence analysis is performed for the remained loops. The last column of the Table 3.1 shows the number of blockable loop nests. However, most of them are singly-nested loops that do not benefit from loop blocking since the access pattern would not change.

For the blockable loops, the cache miss is estimated using various blocking sizes. As described before, the singly-nested loops has show no cache performance improvement through loop blocking as shown in Table 3.2. The last column of Table 3.2 shows the number of the blocked loop nests. Several benchmarks have blocked loop nests, but the

|        | # of          |          | Excluded  | l Loops   |         |       | Bl | ockabl              | е Lоор | s         |

|--------|---------------|----------|-----------|-----------|---------|-------|----|---------------------|--------|-----------|

| Bench  | $_{ m Loops}$ | Unstruct | Imperfect | S. Effect | Depend  | # of  | N  | est De <sub>l</sub> | pth    | Total     |

|        | Analyzed      | Loops    | Nest      | Calls     | Invalid | Loops | 3  | 2                   | 1      | Loopnests |

| ADM    | 302           | 13       | 50        | 51        | 20      | 198   | 9  | 25                  | 121    | 155       |

| SPICE  | 348           | 87       | 22        | 245       | 0       | 55    | 0  | 0                   | 55     | 55        |

| MGD    | 52            | 5        | 19        | 6         | 2       | 29    | 0  | 0                   | 29     | 29        |

| TRACK  | 97            | 25       | 15        | 29        | 2       | 53    | 0  | 4                   | 45     | 49        |

| BDNA   | 270           | 26       | 40        | 71        | 0       | 158   | 0  | 8                   | 142    | 150       |

| OCEAN  | 132           | 4        | 34        | 22        | 26      | 79    | 0  | 8                   | 63     | 71        |

| DYFESM | 264           | 15       | 62        | 83        | 9       | 124   | 0  | 18                  | 88     | 106       |

| MG3D   | 111           | 1        | 42        | 27        | 0       | 62    | 0  | 13                  | 36     | 49        |

| ARC2D  | 233           | 2        | 31        | 9         | 0       | 198   | 5  | 46                  | 91     | 142       |

| FLO52  | 188           | 14       | 35        | 22        | 4       | 128   | 7  | 27                  | 53     | 87        |

| TRFD   | 78            | 4        | 30        | 3         | 0       | 37    | 0  | 8                   | 21     | 29        |

| SPEC77 | 407           | 29       | 110       | 63        | 18      | 249   | 0  | 28                  | 193    | 221       |

| Total  | 2482          | 225      | 490       | 631       | 81      | 1370  | 21 | 185                 | 937    | 1143      |

Table 3.1

Blockable Loops for PERFECT Benchmarks

number of the blocked loop nests is relatively small compared with the total number of the loop nests.

## 3.3.2 Cache Miss Ratios for Blocked Loop Nests

Table 3.3 shows dynamic array access statistics for the blocked loops. Among the eight benchmarks that have the blocked loop nests, only two benchmarks, **BDNA** and **ARC2D**, have blocked loop nests that contain relatively high percentages of array access counts.

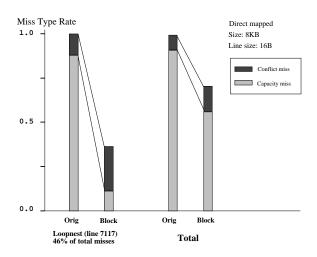

Figure 3.3 shows the cache miss ratio of the blocked loop nest and the entire loop nests of **BDNA**. **BDNA** has a very frequently executed loop nest that contains many arrays, and therefore, loop blocking is very successful in improving the cache performance.

Figure 3.4 shows the cache miss ratio of the blocked loop nest and the entire loop nests of **ARC2D**. Unlike **BDNA**, **ARC2D** has relatively many blocked loop nests, but

|        |    | Bloo    | kable l | Loops     |    | No I    | mprov | ement     |     |        |    | Loops     |

|--------|----|---------|---------|-----------|----|---------|-------|-----------|-----|--------|----|-----------|

| Bench  | N  | est Dej | pth     | Total     | N  | est Dej | pth   | Total     | Nes | st Dep | th | Total     |

|        | 3  | 2       | 1       | Loopnests | 3  | 2       | 1     | Loopnests | 3   | 2      | 1  | Loopnests |

| ADM    | 9  | 25      | 121     | 155       | 1  | 3       | 121   | 125       | 8   | 22     | 0  | 30        |

| SPICE  | 0  | 0       | 55      | 55        | 0  | 0       | 55    | 55        | 0   | 0      | 0  | 0         |

| MDG    | 0  | 0       | 29      | 29        | 0  | 0       | 29    | 29        | 0   | 0      | 0  | 0         |

| TRACK  | 0  | 4       | 45      | 49        | 0  | 4       | 45    | 49        | 0   | 0      | 0  | 0         |

| BDNA   | 0  | 8       | 142     | 150       | 0  | 3       | 142   | 145       | 0   | 5      | 0  | 5         |

| OCEAN  | 0  | 8       | 63      | 71        | 0  | 0       | 63    | 63        | 0   | 8      | 0  | 8         |

| DYFESM | 0  | 18      | 88      | 106       | 0  | 16      | 88    | 104       | 0   | 2      | 0  | 2         |

| MG3D   | 0  | 13      | 36      | 49        | 0  | 13      | 36    | 49        | 0   | 0      | 0  | 0         |

| ARC2D  | 5  | 46      | 91      | 142       | 3  | 26      | 91    | 120       | 2   | 20     | 0  | 22        |

| FLO52  | 7  | 27      | 53      | 87        | 6  | 25      | 53    | 84        | 1   | 2      | 0  | 3         |

| TRFD   | 0  | 8       | 21      | 29        | 0  | 2       | 21    | 23        | 0   | 6      | 0  | 6         |

| SPEC77 | 0  | 28      | 193     | 221       | 0  | 21      | 193   | 214       | 0   | 7      | 0  | 7         |

| Total  | 21 | 185     | 937     | 1143      | 10 | 113     | 937   | 1060      | 11  | 72     | 0  | 83        |

Table 3.2

Blocked Loop Nests for PERFECT Benchmarks

|        |               | Blocked Loops |           |              |              |  |

|--------|---------------|---------------|-----------|--------------|--------------|--|

| Bench  | Total         | # of L        | loopnests | Array Access | % of Total   |  |

|        | Array Access  | Source        | Executed  |              | Array Access |  |

| ADM    | 462,824,761   | 30            | 0         | 0            | 0            |  |

| BDNA   | 436,028,173   | 5             | 5         | 285,750,080  | 65.5         |  |

| OCEAN  | 2,669,877,945 | 8             | 0         | 0            | 0            |  |

| DYFESM | 410,046,035   | 2             | 2         | 1,873,872    | 0.5          |  |

| ARC2D  | 1,981,154,040 | 22            | 14        | 561,837,852  | 28.4         |  |

| FLO52  | 736,423,318   | 3             | 1         | 5,715,360    | 0.7          |  |

| TRFD   | 666,159,027   | 6             | 0         | 0            | 0            |  |

| SPEC77 | 2,530,747,172 | 7             | 0         | 0            | 0            |  |

Table 3.3

Array Access Counts of PERFECT

Figure 3.3 Cache Miss Detail of BDNA

Figure 3.4 Cache Miss Detail of ARC2D

|                          | Effective ?     | Somewhat effective | X Not effective        |  |  |

|--------------------------|-----------------|--------------------|------------------------|--|--|

|                          | Capacity misses | Conflict misses    | Line fetch<br>overhead |  |  |

| Large Cache              | ?               | ×                  | N/A                    |  |  |

| Highly Associative Cache | ×               | ?                  | N/A                    |  |  |

| Small Cache Line Size    | X               | ×                  |                        |  |  |

| Loop Blocking            | ?               | ×                  | N/A                    |  |  |

Table 3.4 Motivation for a More Aggressive Method

each execution percentage is small. Therefore, the entire benchmark cache performance is not improved significantly.

Loop blocking as well as changing cache parameters as described in Section 2.4 does not solve all cache problems at the same time. This motivates a more aggressive method that can solve all the cache problems at the same time (Table 3.4).

## CHAPTER 4

## DATA RELOCATION AND PREFETCHING

## 4.1 Method

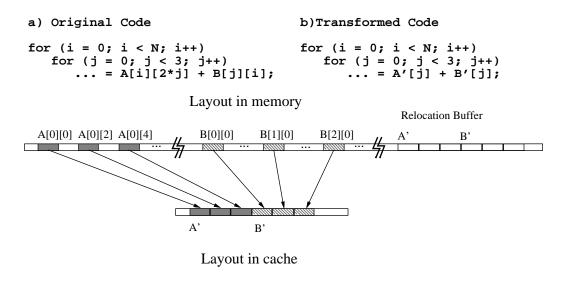

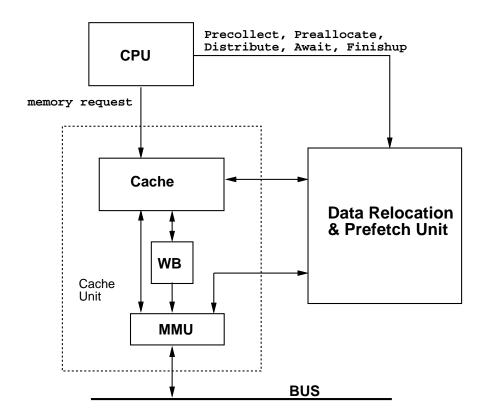

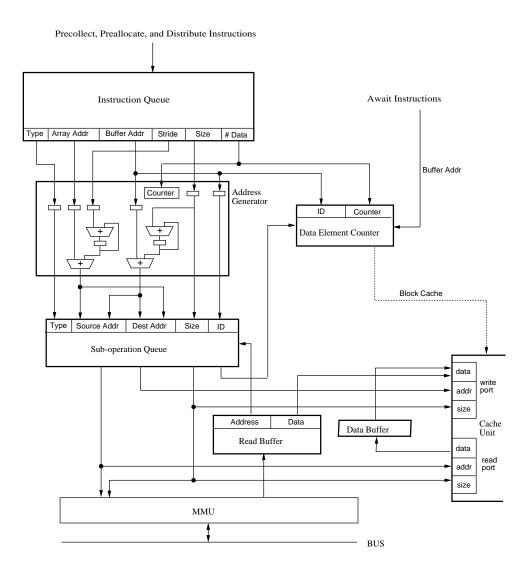

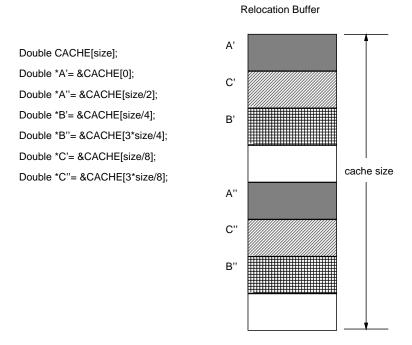

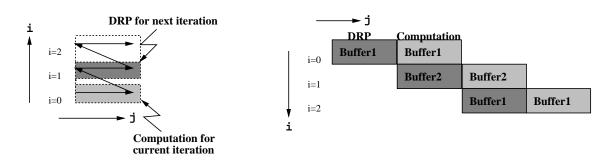

I propose a compiler-supported, hardware-based technique called data relocation and prefetching in order to improve the data cache performance. In this method, the array references in the inner loop of a nest are sequentially mapped in the cache before they are accessed. The relocation operations are invoked by explicit instructions inserted by the compiler. The compiler also inserts a declaration into the original code for the relocation buffer that allocates space for the relocated data in memory. Special hardware that is attached to the cache unit maps and compresses the data into the virtual buffer space so that the relocation can be performed while prefetching the data from the memory to the cache and without stalling the *CPU*. In order to access the relocated data (instead of the original array data) during the computation, the compiler replaces the original array references with corresponding relocation buffer references.

Because the array data is relocated, the prefetch is binding. During the computation, the newly assigned address in the relocation buffer space is used to access the data rather than the original address. Consequently, the relocation must be completed before the computation on the same data begins. If the relocated, cached data is replaced by

some other original address accesses, such as scalar accesses, the relocated data must be written back to the relocation buffer in memory since the accesses in the computation use the address of the relocated data. To insure write-back of the relocated data, the dirty bit is set when the cache line for the data is allocated. When the computation that uses the relocated data is finished, all modified, relocated data are written back from the relocation buffer to their original memory locations using an explicit machine instruction.

Data Relocation and Prefetching (DRP) can improve the spatial locality of array accesses for a loop nest. Figure 4.1 shows how array data elements accessed in the first iteration of the outer loop are copied to sequential cache locations that map to the relocation buffer in memory. Array  $\mathbf{A}$  is accessed with a stride of two, and array  $\mathbf{B}$  is accessed in column order during the execution of the inner loop. Accesses to these array elements can result in poor performance because:

- (1) The accesses may not exhibit any spatial locality because of the non-unit access stride, resulting in wasted cache capacity which may lower the cache hit rate.

- (2) The sets of accesses for different arrays may conflict with each other because they happen to be mapped to some of the same locations in the cache.

- (3) The accesses for a single array may conflict with each other because of a large access stride.

If the accessed elements of these arrays are relocated in the cache, spatial locality can be improved by packing elements of the arrays into contiguous locations. Also, since only necessary elements are brought into the cache, the extra memory requests and time to