UILU-ENG-90-2236 CRHC-90-6

Center for Reliable and High-Performance Computing

# **COMPILER-ASSISTED SIGNATURE MONITORING**

Nancy J. Warter Wen-mei W. Hwu

Coordinated Science Laboratory College of Engineering UNIVERSITY OF ILLINOIS AT URBANA-CHAMPAIGN

Approved for Public Release. Distribution Unlimited.

|                                                                                                                |                                                                                                                                                                                                                                          |                                                                                                                                                                                                                                                            | REPORT DOCU                                                                                                                                                                                                                                                                                                                  | MENTATION                                                                                                                                                                                                                                           | PAGE                                                                                                                                                                                    |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | •                                                                                                                                                |  |

|----------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------|--|

| a. REPORT SE                                                                                                   | ECURITY CLASSI                                                                                                                                                                                                                           | FICATION                                                                                                                                                                                                                                                   |                                                                                                                                                                                                                                                                                                                              | 16. RESTRICTIVE                                                                                                                                                                                                                                     |                                                                                                                                                                                         |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                                                                                                                                                  |  |

| Unclass                                                                                                        |                                                                                                                                                                                                                                          |                                                                                                                                                                                                                                                            |                                                                                                                                                                                                                                                                                                                              | None                                                                                                                                                                                                                                                |                                                                                                                                                                                         | and the second                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                                                                                                                                                  |  |

| a. SECURITY                                                                                                    | CLASSIFICATION                                                                                                                                                                                                                           | AUTHORITY                                                                                                                                                                                                                                                  |                                                                                                                                                                                                                                                                                                                              | 3. DISTRIBUTION                                                                                                                                                                                                                                     |                                                                                                                                                                                         |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                                                                                                                                                  |  |

| b. DECLASSIF                                                                                                   | CATION / DOW                                                                                                                                                                                                                             | NGRADING SCHED                                                                                                                                                                                                                                             | ULE                                                                                                                                                                                                                                                                                                                          |                                                                                                                                                                                                                                                     | d for publication unlied                                                                                                                                                                |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | se;                                                                                                                                              |  |

| PERFORMIN                                                                                                      | IG ORGANIZATI                                                                                                                                                                                                                            | ON REPORT NUMB                                                                                                                                                                                                                                             | ER(S)                                                                                                                                                                                                                                                                                                                        | 5. MONITORING                                                                                                                                                                                                                                       | ORGANIZATION                                                                                                                                                                            | N REPORT NU                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | UMBER(S)                                                                                                                                         |  |

| UILU-E                                                                                                         | NG-90-2236                                                                                                                                                                                                                               | (CRHC-90-6                                                                                                                                                                                                                                                 | )                                                                                                                                                                                                                                                                                                                            | 1                                                                                                                                                                                                                                                   |                                                                                                                                                                                         |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                                                                                                                                                  |  |

| 6a. NAME OF PERFORMING ORGANIZATION<br>Coordinated Science Lab (If applicable)                                 |                                                                                                                                                                                                                                          |                                                                                                                                                                                                                                                            | 7a. NAME OF MONITORING ORGANIZATION<br>Office of Naval Research                                                                                                                                                                                                                                                              |                                                                                                                                                                                                                                                     |                                                                                                                                                                                         |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                                                                                                                                                  |  |

|                                                                                                                | sity of Il                                                                                                                                                                                                                               |                                                                                                                                                                                                                                                            | N/A                                                                                                                                                                                                                                                                                                                          |                                                                                                                                                                                                                                                     |                                                                                                                                                                                         |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                                                                                                                                                  |  |

| 1101 W.                                                                                                        | (City, State, and<br>. Springfi<br>, IL 6180                                                                                                                                                                                             | eld Ave.                                                                                                                                                                                                                                                   |                                                                                                                                                                                                                                                                                                                              |                                                                                                                                                                                                                                                     | Quincy St.<br>on, VA 22                                                                                                                                                                 |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                                                                                                                                                  |  |

| Ba. NAME OF FUNDING/SPONSORING<br>ORGANIZATION Joint Services<br>Electronics Program                           |                                                                                                                                                                                                                                          |                                                                                                                                                                                                                                                            | 9. PROCUREMENT INSTRUMENT IDENTIFICATION NUMBER<br>N00014-84-C-0149                                                                                                                                                                                                                                                          |                                                                                                                                                                                                                                                     |                                                                                                                                                                                         |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                                                                                                                                                  |  |

| c. ADDRESS (                                                                                                   | City, State, and                                                                                                                                                                                                                         | ZIP Code)                                                                                                                                                                                                                                                  |                                                                                                                                                                                                                                                                                                                              | 10. SOURCE OF                                                                                                                                                                                                                                       |                                                                                                                                                                                         | and the second se |                                                                                                                                                  |  |

| 800 N. Quincy St.<br>Arlington, VA 22217                                                                       |                                                                                                                                                                                                                                          |                                                                                                                                                                                                                                                            |                                                                                                                                                                                                                                                                                                                              | PROGRAM<br>ELEMENT NO.                                                                                                                                                                                                                              | PROJECT<br>NO.                                                                                                                                                                          | TASK<br>NO.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | WORK UI<br>ACCESSIO                                                                                                                              |  |

| 2. PERSONAL                                                                                                    | COMPILER                                                                                                                                                                                                                                 |                                                                                                                                                                                                                                                            | GNATURE MONITORIN                                                                                                                                                                                                                                                                                                            |                                                                                                                                                                                                                                                     |                                                                                                                                                                                         |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                                                                                                                                                  |  |

|                                                                                                                | COMPILER                                                                                                                                                                                                                                 | ASSISTED SI                                                                                                                                                                                                                                                | cy J. and Hwu, We                                                                                                                                                                                                                                                                                                            |                                                                                                                                                                                                                                                     | ORT (Year, Mon<br>ugust 9                                                                                                                                                               | th, Day) 15                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 5. PAGE COUNT<br>41                                                                                                                              |  |

| 3a. TYPE OF<br>Techn:                                                                                          | COMPILER-<br>LAUTHOR(S)<br>REPORT                                                                                                                                                                                                        | Warter, Nan<br>13b. TIME<br>FROM                                                                                                                                                                                                                           | cy J. and Hwu, We<br>COVERED                                                                                                                                                                                                                                                                                                 | en-mei W.<br>14. DATE OF REPO                                                                                                                                                                                                                       | ORT (Year, Mon<br>ugust 9                                                                                                                                                               | th, Day) 15                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |                                                                                                                                                  |  |

| 3a. TYPE OF<br>Techn:<br>6. SUPPLEME                                                                           | COMPILER<br>LAUTHOR(S)<br>REPORT<br>ical                                                                                                                                                                                                 | Warter, Nan<br>13b. TIME<br>FROM                                                                                                                                                                                                                           | cy J. and Hwu, We<br>COVERED                                                                                                                                                                                                                                                                                                 | en-mei W.<br>14. DATE OF REPA<br>1990 Au                                                                                                                                                                                                            | ugust 9                                                                                                                                                                                 | <u> </u>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 41                                                                                                                                               |  |

| 3a. TYPE OF<br>Techn:<br>6. SUPPLEME<br>7.<br>FIELD                                                            | COMPILER-<br>LAUTHOR(S)<br>REPORT<br>ical<br>ENTARY NOTAT<br>COSATI<br>GROUP                                                                                                                                                             | Warter, Nan<br>13b. TIME<br>FROM<br>TION<br>CODES<br>SUB-GROUP                                                                                                                                                                                             | cy J. and Hwu, We<br>COVERED<br>TO<br>18. SUBJECT TERMS (<br>performance<br>assisted                                                                                                                                                                                                                                         | en-mei W.<br>14. DATE OF REP<br>1990 Au<br>Continue on rever<br>, memory, si<br>arc                                                                                                                                                                 | ugust 9<br>rse if necessary                                                                                                                                                             | and identify                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 41                                                                                                                                               |  |

| 3a. TYPE OF<br><u>Techn:</u><br>6. SUPPLEME<br>7.<br>FIELD<br>9. ABSTRACT<br>fo<br>an<br>tic<br>on<br>is<br>to | COMPILER-<br>L AUTHOR(S)<br>REPORT<br>ical<br>ENTARY NOTAT<br>COSATI<br>GROUP<br>I (Continue on<br>A methodormance overhead<br>the signature<br>on complexitic<br>the error dete<br>significantly b                                      | ASSISTED SI<br>Warter, Nan<br>13b. TIME<br>FROM<br>ION<br>CODES<br>SUB-GROUP<br>reverse if necessar<br>ology for applying<br>ead and simplify in<br>e placement. The<br>s low. Our signa<br>ection latency. Ju<br>etter than previou<br>s signature placem | cy J. and Hwu, We<br>COVERED<br>TO<br>18. SUBJECT TERMS (<br>performance                                                                                                                                                                                                                                                     | en-mei W.<br>14. DATE OF REPU-<br>1990 Au<br>Continue on rever<br>arc<br>number)<br>echniques to signa<br>oduced. We press<br>odel is designed<br>to insert reference<br>userted on program<br>tion algorithms.                                     | agust 9<br>rea if necessary<br>ignature mo<br>ignature mo<br>ignature mo<br>ignatures mo<br>to keep both the<br>e signatures in<br>m arcs using ar<br>We use optimin<br>minimize the po | and identify<br>on i tor i ng<br>g in order to<br>the monitor<br>he hardware<br>order to sat<br>a $O(N^2)$ algo<br>zing compile                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 41<br>by block number)<br>g, compiler-<br>to reduce per-<br>or architecture<br>e and integra-<br>tisfy a bound<br>orithm which<br>ler techniques |  |

| 3a. TYPE OF<br>Techn:<br>6. SUPPLEME<br>7.<br>FIELD<br>9. ABSTRACT<br>fo<br>an<br>tic<br>on<br>is<br>to<br>to  | COMPILER-<br>L AUTHOR(S)<br>REPORT<br>ical<br>ENTARY NOTAT<br>GROUP<br>GROUP<br>T (Continue on<br>A methodormance overhead<br>the signature<br>on complexitic<br>a the error dete<br>significantly b<br>customize the<br>justifying sign | ASSISTED SI<br>Warter, Nan<br>13b. TIME<br>FROM<br>ION<br>CODES<br>SUB-GROUP<br>reverse if necessar<br>ology for applying<br>ead and simplify in<br>e placement. The<br>s low. Our signa<br>ection latency. Ju<br>etter than previou<br>s signature placem | cy J. and Hwu, We<br>COVERED<br>TO<br>18. SUBJECT TERMS (<br>performance<br>assisted<br>y and identify by block<br>g optimizing compiler to<br>monitor hardware is intre-<br>monitor architecture model<br>ture model is designed<br>stifying signatures are in<br>s exponential node inser-<br>nent for various target pro- | en-mei W.<br>14. DATE OF REP<br>1990 Au<br>Continue on rever<br>, memory, si<br>arc<br>number)<br>echniques to signa<br>oduced. We press<br>odel is designed<br>to insert reference<br>userted on program<br>tion algorithms.<br>rocessors and to r | agust 9<br>rea if necessary<br>ignature mo<br>ignature mo<br>ignature mo<br>ignatures mo<br>to keep both the<br>e signatures in<br>m arcs using ar<br>We use optimin<br>minimize the po | and identify<br>on i toring<br>g in order to<br>the monitor<br>he hardware<br>order to sat<br>$O(N^2)$ algo<br>zing compile<br>erformance of<br>i nued                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 41<br>by block number)<br>g, compiler-<br>to reduce per-<br>or architecture<br>e and integra-<br>tisfy a bound<br>orithm which<br>ler techniques |  |

UNCLASSIFIED

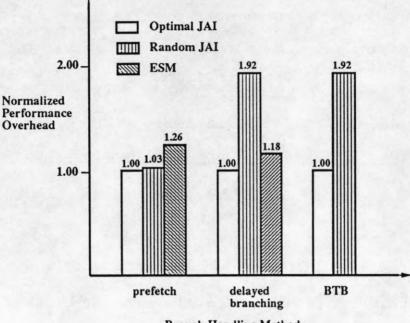

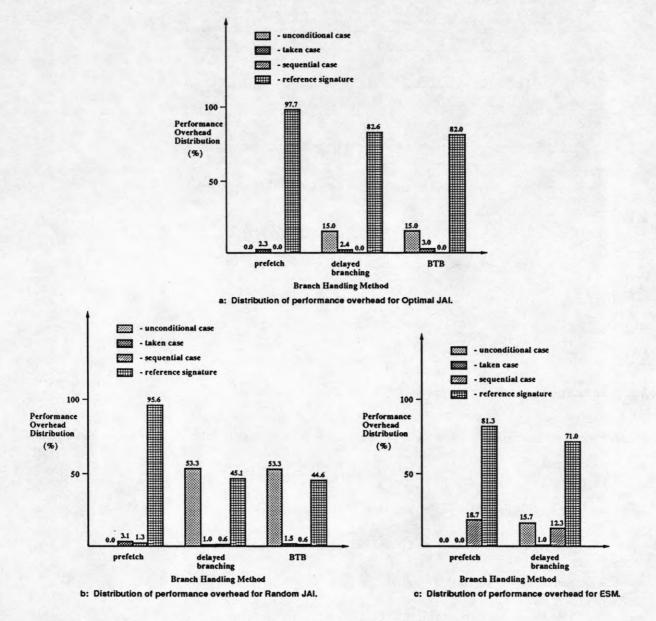

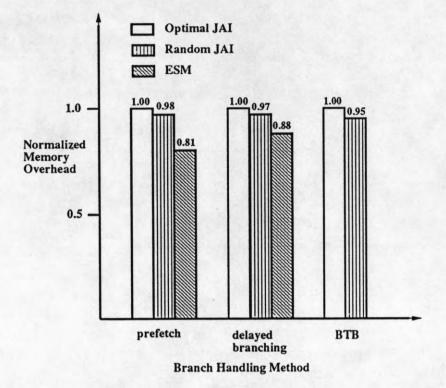

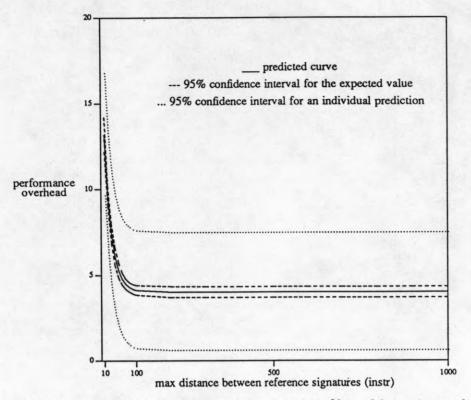

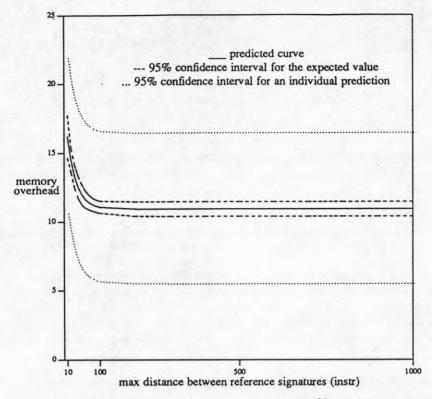

Experiments were performed to study the performance and memory overheads of our compiler-assisted arc insertion signature monitoring method for a variety of architectures with different branch handling schemes. Using run-time information for processors with delayed branching or branch target buffers improves the performance overhead by approximately 50. However, processors that always fetch the instruction following a branch and squash it if the branch is taken (e.g., the MC68000) are able to hide some of the performance overhead and therefore the run-time information only slightly improves the performance overhead. Using the MC68000 as the target processor, the performance and memory overheads for latencies between 10 and 200 instruction cycles, range from 16 to 4 and from 17 to 11 respectively. After 200 cycles, the overheads remain relatively constant. In general, there is an inverse exponential relationship between the performance and memory overheads and the error detection latency.

# **Compiler-Assisted Signature Monitoring**

Nancy J. Warter

Wen-mei W. Hwu

August 8, 1990

Center for Reliable and High-Performance Computing Coordinated Science Laboratory 1101 W. Springfield Ave. University of Illinois at Urbana-Champaign Urbana, IL 61801

#### Abstract

A methodology for applying optimizing compiler techniques to signature monitoring in order to reduce performance overhead and simplify monitor hardware is introduced. We present models for the monitor architecture and the signature placement. The monitor architecture model is designed to keep both the hardware and integration complexities low. <sup>1</sup> Our signature model is designed to insert reference signatures in order to satisfy a bound on the error detection latency. Justifying signatures are inserted on program arcs using an  $O(N^2)$  algorithm which is significantly better than previous exponential node insertion algorithms. We use optimizing compiler techniques to customize the signature placement for various target processors and to minimize the performance overhead due to justifying signatures.

Experiments were performed to study the performance and memory overheads of our compilerassisted arc insertion signature monitoring method for a variety of architectures with different branch handling schemes. Using run-time information for processors with delayed branching or branch target buffers improves the performance overhead by approximately 50%. However, processors that always fetch the instruction following a branch and squash it if the branch is taken (e.g., the MC68000) are able to hide some of the performance overhead and therefore the run-time information only slightly improves the performance overhead. Using the MC68000 as the target processor, the performance and memory overheads for latencies between 10 and 200 instruction cycles, range from 16% to 4% and from 17% to 11% respectively. After 200 cycles, the overheads remain relatively constant. In general, there is an inverse exponential relationship between the performance and memory overheads and the error detection latency.

<sup>&</sup>lt;sup>1</sup>Preliminary research for this paper was presented at FTCS-20[23].

# 1 Introduction

An efficient concurrent error detection scheme should have good error coverage, be easy to implement, not significantly degrade the target system performance, and have reasonable error detection latency. For embedded concurrent error detection schemes, it is particularly important to keep the implementation complexity low. Otherwise, the additional hardware may actually lower the system reliability. To keep the implementation complexity low, the hardware should be simple and the integration should not require major modifications to the basic system architecture.

In recent years, signature monitoring has become an attractive embedded concurrent error detection scheme because it can detect approximately 99% of the control flow errors [11, 17, 25] using a simple watchdog monitor<sup>2</sup> [15, 12, 16, 20]. In signature monitoring, the compiler encodes the program control flow information into signatures. At run-time, the watchdog monitor uses these signatures to detect instruction bit and sequence errors [21]. Sequence errors correspond to failures that result in incorrect program flow.

In most signature monitoring schemes, signatures are inserted directly into the program code [14, 18, 25]. Adding these signatures degrades the target system performance and increases the program memory requirements. In order to reduce these performance and memory overheads, previous schemes have added hardware assists to the watchdog monitor [15, 19, 25].

In this paper, we present a signature monitoring method which uses optimizing compiler techniques instead of hardware assists to reduce the performance overhead.<sup>3</sup> The optimizing compiler is customized to the target processor so that other than a simple interface, the monitor architecture is target processor independent. Furthermore, signatures are placed such that they guarantee a

<sup>&</sup>lt;sup>2</sup>Experiments performed by Gunneflo et al. indicate that approximately 78% of the measured errors were control flow errors [7].

<sup>&</sup>lt;sup>3</sup>Preliminary research for this paper was presented at FTCS-20[23].

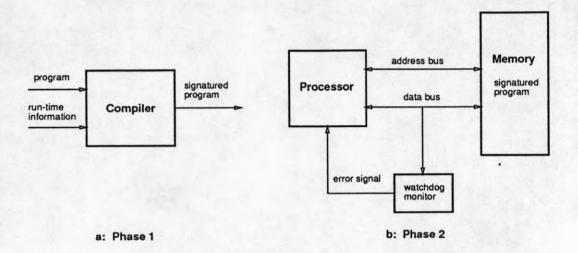

Figure 1: The phases of signature monitoring.

bound on the error detection latency.

To analyze the effectiveness of our compiler-assisted approach we compare the performance and memory overheads with the best hardware-assisted method, Wilken and Shen's Embedded Signature Monitoring [25]. In addition, we analyze the effect of bounding the error detection latency on the performance overhead, memory overhead, and error coverage.

# 2 Signature Monitoring

There are two phases to signature monitoring as shown in Figure 1. In the first phase, the compiler generates the signatures off-line and either embeds them into the original code [5, 10, 14, 17, 19, 20, 26] or provides the information directly to the watchdog [5, 15]. During the second phase, the watchdog monitor computes a run-time signature based on the instructions fetched by the target processor. At certain points the run-time signature is compared against the precomputed signature. Errors in the instructions or in their sequencing are detected if the signatures differ.

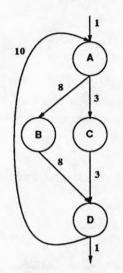

A program can be represented as a control flow graph. A typical control flow graph is presented

Figure 2: Weighted program control flow graph.

in Figure 2. A node represents a sequence of instructions with only one entry and one exit point. Arcs represent the flow of control as determined by branch statements. The weights on the arcs represent the execution frequency of that branch. For programs that are not self-modifying, the control flow graph is fixed and known at compile time. For compilers that can estimate the runtime behavior of the program, the weights are also known at compile time. This graph is used to generate signatures.

There are two types of signatures, reference and justifying. A reference signature is used to verify the control flow of a *program interval* which can consist of one or more nodes. Reference signatures are inserted either within the entry node or within the exit node of an interval. If it is inserted within the entry node of the interval, when the signature is fetched the watchdog performs a zero check on the run-time signature and resets the run-time signature to the new reference value. On the other hand, if it is inserted within the exit node of the interval, when the signature is fetched the watchdog verifies its run-time signature with the reference value and resets the run-time signature to zero.

If an interval associated with a reference signature includes more than one node, the signature at either the branch or the merge point, for entry node and exit node insertion respectively, is inconsistent. Justifying signatures are used to make the signature consistent at these points. Justifying signatures can be inserted either within a node, *justifying node insertion*, or on an arc, *justifying arc insertion*.

#### 2.1 Existing Approaches

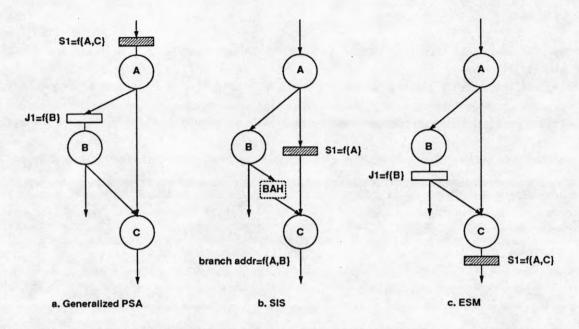

Namjoo's Path Signature Analysis (PSA) is an example of node insertion [14]. In the original PSA, reference signatures are inserted at the beginning of each node. To reduce the memory and performance overhead, generalized PSA (Figure 3a) computes reference signatures for an interval or path set with a common start node. For each branch in the path set, the signatures will become inconsistent. Justifying signatures are added to make the signatures of all paths within a path-set consistent.

In more recent approaches, reference signatures are assigned to the exit or terminal nodes of paths. In such approaches, the signatures are inconsistent at the merge nodes. In the Signatured Instruction Stream (SIS) approach (Figure 3b) which uses Branch Address Hashing (BAH), reference signatures are placed before a merge on the sequential path [17, 18, 19]. Instead of using explicit justifying signatures, Shen and Schuette hash the branch address with the implicit signature value of the branch. If the run-time signature is incorrect then the rehashed branch address will be incorrect and the error will be detected unless the incorrect target is to another merge node. Although this scheme does not use justifying signatures, it is a predecessor of arc insertion because the implicit signature is only hashed along the taken arc of a branch.

Figure 3: Existing signature monitoring schemes.

Embedded Signature Monitoring (ESM) is a hybrid node/arc insertion method (Figure 3c) [25, 26]. The compiler inserts justifying signatures within the node after a branch instruction. At run-time, hardware is used to determine whether or not the branch is taken. If it is then the justifying signature is included into the run-time signature. Otherwise it is discarded. Thus, the justifying signature is only included into the run-time signature along the taken arc of a branch.

In general, in arc insertion justifying signatures can be placed on any merge merge arc, not just the taken arc of a branch. Our signature model presented in Section 4.1.1 considers all of the cases for arc insertion.

#### 2.1.1 Software Complexity

The implementation complexity includes both the hardware and software complexities. In this paper, the software complexity refers to the time required to compile a program. For a signature

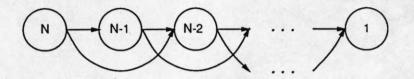

Figure 4: Directed acyclic graph with out-degree two.

monitoring approach to be practical the time to compile a program with signatures must be reasonable. The algorithm complexity of the signature insertion method reflects the additional time required to compile the program with signatures. In addition, any optimizing compiler techniques used specifically for signature insertion should also be included in the software complexity.

In Namjoo's PSA node insertion algorithm, all paths within a program interval are enumerated [14]. These paths are then resolved to determine the justifying signatures, their placement, and the reference signature of the interval. As shown in the following theorem, this algorithm has exponential complexity.

Theorem 1 The maximum number of paths between two nodes in a directed acyclic graph with an out-degree of two is exponential in the number of nodes in the interval.

**Proof** For the graph depicted in Figure 4 if node N is added to the graph with arcs to nodes N-1 and N-2 then the number of paths is P(N) = P(N-1) + P(N-2). This is the Fibonnaci recurrence. The solution is

$$F_N = \frac{1}{\sqrt{5}} \left( \frac{1+\sqrt{5}}{2} \right)^N - \frac{1}{\sqrt{5}} \left( \frac{1-\sqrt{5}}{2} \right)^N.$$

In Section 5 we present algorithms for arc insertion which have  $O(N^2)$  complexity for a program graph with N nodes. In addition, we discuss the software complexity associated with the optimizing compiler techniques we use.

#### 2.1.2 Hardware Complexity

To reduce the performance overhead due to inserting the signatures into the program code, previous methods have used hardware assists. Namjoo modified PSA by moving the signatures from the program code to the Cerebus-16 watchdog monitor environment [15]. Eifert and Shen extended SIS by removing the signatures from the program code and instead storing the program control flow graph and signature information in the monitor memory [5]. This method, Asynchronous Signature Instruction Stream (ASIS) can monitor multiple processors continuously. Both of these schemes eliminate the performance overhead but significantly increase the monitor complexity.

SIS and ESM use simple hardware assists to reduce the number of signatures fetched by the processor and thus reduce the performance overhead. SIS uses branch detection and address hashing hardware to combine the signature with the branch instruction. ESM uses hardware to determine whether or not the branch is taken or not.

# 3 Monitor Architecture Model

The watchdog monitor design should be simple and easy to integrate into the target system. It is especially important to keep the monitor design simple if the target processor has an on-chip instruction cache. Since the monitor must lie between the processor and memory, the monitor will have to be integrated into the chip design. To simplify the monitor and ease integration, we assume that the signature placement scheme does not require additional hardware support or place restrictions on the target architecture.

The two basic parts of the monitor are the interface and checking modules. The interface module is responsible for detecting instruction words and signatures and propagating the error signal from the checking module to the target processor. The interface module is target processor dependent. Previous work has addressed the interface implementation issues for a variety of target architectures [9, 14, 16, 18, 20].

The checking module is application specific rather than processor specific. The signature encoding scheme is chosen based on the error coverage, error detection latency, and performance and memory overhead requirements of the application. The basic functions of the checking module are to generate the run-time signature, encorporate justifying signatures, compare against reference signatures, and propagate an error signal to the interface module if the run-time and reference signatures disagree.

Subroutine calls and interrupts require special handling. Previous methods use signature stacks to store the signature during a subroutine call or interrupt handling routine [4, 5, 18, 19]. On a subroutine return or return from interrupt, the signature is popped off the stack and checking of the interrupted routine continues. The signature stack significantly increases the monitor complexity because it requires a memory interface to handle stack overflows. Saxena and McCluskey propose a software approach for target processors that support coprocessors [16]. On an interrupt, the signature can be saved by generic processor save/restore routines. While this simplifies the monitor complexity, it will increase the performance and memory overheads. Wilken and Shen eliminate the signature stack by using a characteristic signature for each routine [26]. On a return from interrupt, this characteristic routine is used to justify the run-time signature. The disadvantage of this approach is that reference signatures cannot be inserted within the interrupt handling routines.

In our approach, we assume that there is a bound on the error detection latency. If the error is not detected within this bound, the error is assumed to be undetected. If a signature stack is used and an error occurs within a program interval before an interrupt, the error will not be detected until after the interrupt handler has been executed. Such errors will likely exceed the bound on the error detection latency and are considered undetected. Therefore, signature stacks are not included in our model. To eliminate the need for a subroutine signature stack, we assume that reference signatures are placed before a subroutine call and at the end of a subroutine.

Interrupts, on the other hand, are asynchronous and therefore reference signatures cannot be placed before an interrupt. Instead, the signature checker is reset on an interrupt and checking begins on the interrupt handling routine. Reference signatures are inserted within the handling routine in order to satisfy the bound and at the end of the routine. On a return from interrupt, the signature checker is disabled until the next reference signature is fetched. After that normal checking resumes.

The elimination of signature stacks greatly simplifies the monitor hardware. In addition, for on-chip monitors the signatures do not need to be incorporated into the processor state. Therefore, it is possible to integrate the monitor without major modifications to the original processor design.

# 4 Signature Insertion Model

The signature insertion model indicates how justifying signatures and reference signatures should be inserted into the program code in order to guarantee that the program is properly encoded. Furthermore, the justifying signature insertion model is designed to minimize the performance overhead and the reference signature insertion model is designed to guarantee a specified bound on the error detection latency. The models have low software complexity and do not require special hardware support beyond the basic monitor.

#### 4.1 Justifying Signature Insertion

In this section we present our arc insertion model and show how optimizing compiler techniques can be used to simplify the monitor and reduce the performance overhead.

In justifying arc insertion, the program interval is justified at the program merge nodes. At a merge node, the signature along each incoming arc is different. Only one signature can be used to define the signature at the merge node. Justifying signatures are used to transform the remaining incoming signatures to this unique signature. There is only one constraint to placing the signatures on the program arcs.

Constraint 1: For a merge node with i incoming arcs, justifying signatures must be placed on i-1 arcs.

The arcs with justifying signatures are justifying arcs and the remaining arc is the unique arc.

#### 4.1.1 Arc Insertion Model

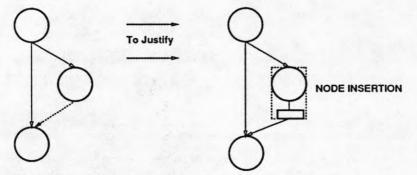

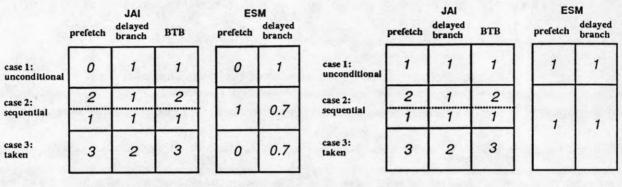

There are three types of justifying arcs, which are drawn as dashed lines in the control flow graphs of the three cases in Figure 5.

In the first case, the justifying arc represents an unconditional branch. Since it is an unconditional branch, the signature can be placed directly in the node without affecting any other program path. The signature can either be placed before or after the branch instruction. If the target architecture always fetches the instruction following a branch, it can be placed after the branch. Otherwise, it must be placed before the branch.

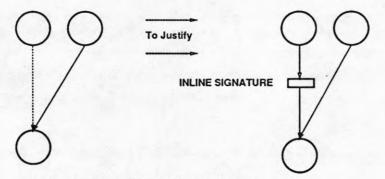

In the second case, the justifying arc is on the sequential path. The sequential path can either be the not taken path of a conditional branch or after a non-branching node. Either way, the last

CASE 1: JUSTIFYING ARC FROM UNCONDITIONAL BRANCH

CASE 2: JUSTIFYING ARC ON SEQUENTIAL PATH

CASE 3: JUSTIFYING ARC IS THE TAKEN PATH OF CONDITIONAL BRANCH

Figure 5: Justifying arc insertion.

instruction in the source node and the first instruction in the destination node of the justifying arc are in sequential memory locations. The justifying signature is placed between these two instructions.

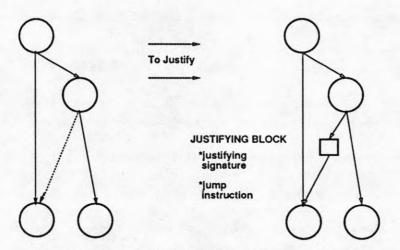

In the third case, the justifying arc is on the taken path of a conditional branch. In this case the source and destination nodes of the justifying arc are not in sequential memory locations. Therefore, to place the justifying signature on the arc, a *justifying block* is inserted between the source and destination nodes. The justifying block consists of a signature instruction and a jump instruction. The destination of the branch instruction in the source node is modified to jump to the justifying block, and the justifying block jumps to the original destination node.

#### 4.1.2 Justifying Signature Generation

For arc insertion, signature generation depends on the following property.

**Property 1:** There is a path along unique arcs between the start and terminal nodes of a program interval.

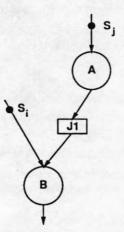

Based on this property, all of the signatures of the unique arcs in a program interval can be determined by a breadth first search. After all the unique arcs are labeled with their signatures, the justifying signatures can be generated as shown in Figure 6. The justifying signature J1 is a function of the unique signature  $S_i$ , the unique signature of its source node  $S_j$ , and the signature of node A.

#### 4.1.3 Optimizing Compiler Techniques

In an optimizing compiler, the architectural features of the target processor are known so that the compiler can order the instructions such that they fully utilize the target processor while not

Figure 6: Signature generation for arc insertion.

violating the execution order. In a similar fashion, the target processor features can be used to ensure that signatures are placed properly. That is, only signatures that are supposed to be included into the run-time signature are fetched by the target processor. In particular, the branch handling scheme must be accounted for. For example, recall that the MC68000 always fetches the instruction following the branch and discards it if the branch is taken. Therefore, signatures can always be placed after an unconditional branch without incurring any performance penalty. On the other hand, signatures cannot be inserted directly after the branch on the sequential arc. Otherwise, if the branch is taken then the signature will be incorrectly included into the run-time signature. A detailed performance and memory cost analysis for a variety of branch handling mechanisms is provided in Section 6.1.1.

Another optimizing compiler technique is to use run-time information to improve the processor performance. For instance, run-time information can be used to place instructions to improve sequential locality. Run-time information can also be used to place signatures to reduce the performance overhead. The minimum number of justifying signatures required to encode a program interval with one reference signature and n conditional branches is n [26]. Arc insertion places the minimum number of signatures into the program code. Our goal is to use run-time information to minimize the number of signatures *fetched* and thus minimize the performance degradation.

In arc insertion, any merge arc can be selected as the unique arc. Run-time information can be used to guide this selection. By measuring the run-time behavior of the program, the node execution and branch frequencies can be predicted. Based on this prediction, the cost of inserting a signature on each merge arc can be determined. The cost, *arc\_cost*, in terms of number of instruction words fetched, is:

### arc\_cost = arc\_frequency \* node\_weight \* just\_words.

For example, if the signature is placed on the taken path of a conditional branch, *arc\_frequency* is the probability that the branch is taken, *node\_weight* is the number of times the branch is executed, and *just\_words* is the number of instructions words required for a justifying block. The *just\_words* also reflects cost of the special architectural features of the target processor.

The following theorem proves that using *arc\_cost* to select the unique arc minimizes the performance overhead for justifying arc insertion.

**Theorem 2** If the unique arc of each merge node corresponds to the incoming arc with the highest arc\_cost, the number of instruction words fetched to justify the program is minimized.

**Proof** Since justifying signatures are placed on the arcs, the signature assignments for each merge node do not depend on the assignments at other merge nodes. Therefore, the total number of justifying signatures fetched is the sum of the justifying signatures fetched at each merge node. For a single merge node, if the unique arc has the highest *arc\_cost* of all the incoming arcs, the number of instruction words fetched to justify that node is a minimum. Since a sum of minimums is a minimum sum, the number of instruction words to justify the entire program is minimized.  $\Box$

This theorem proves that using run-time information will minimize the performance overhead for justifying arc insertion. In the experiment section (Section 6) we empirically prove that optimized arc insertion (i.e., using run-time information) minimizes the overhead due to justifying signatures.

#### 4.2 Reference Signature Insertion

The separation of reference signatures defines the checking interval  $l_{max}$ . For bit errors, the average detection latency is  $l_{max}/2$  and the maximum detection latency is  $l_{max}$  [26]. For single sequence errors, the average detection latency is  $l_{max}$  and the maximum detection latency is  $2l_{max}$ . Let B be the bound of the error detection latency for all bit errors and single sequence errors. Reference signatures must be placed such that l is at most B/2.

#### 4.2.1 Reference Insertion Model

The reference signature insertion model is shown in Figure 7. A reference signature is required at each program exit point in order to correctly check the program (case 1). Recall that a signature stack will violate the bound on the error detection latency. To eliminate the need for a signature stack for subroutine calls, reference signatures are placed before the call and at the end of the routine (cases 2 and 3). A reference signature is placed at the end of an inner loop, case 4, in order to guarantee that loops of length less than  $l_{max}$  do not violate the bound on the detection latency. Furthermore, this breaks cycles in the program graph which simplifies the reference placement algorithm presented in the next section. Finally, signatures are placed such that no two are farther apart than  $l_{max}$  (case 5).

| Reference | signatures are placed:                                             |

|-----------|--------------------------------------------------------------------|

| case 1:   | at program exit points,                                            |

| case 2:   | before a subroutine call,                                          |

| case 3:   | at the end of subroutines,                                         |

| case 4:   | at the end of an inner loop, and                                   |

| case 5:   | to guarantee a bound, <i>Imax,</i> on the error detection latency. |

|           |                                                                    |

Figure 7: Reference signature insertion model.

# 5 Signature Insertion Algorithms

In this section, the algorithms for placing and generating both justifying and reference signatures are presented. A discussion of the algorithm complexities and overhead associated with collecting run-time information is provided at the end of the section.

#### 5.1 Justifying Signature Placement Algorithm

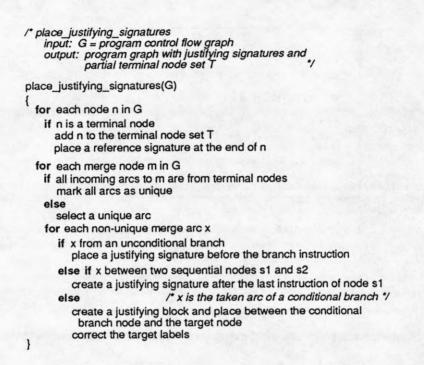

The algorithm for justifying signature placement<sup>4</sup> is shown in Figure 8. The algorithm implements the justifying arc insertion model and generates a partial terminal node set T. This set corresponds to the first four cases of the reference signature model, namely, a program or subroutine exit node, an inner-loop exit node, or the node before a subroutine call. The program control flow graph, G, is the input to the algorithm. First, the terminal nodes are determined. Then, for each merge node, if all incoming arcs are from terminal nodes, none of the signatures need to be justified. Otherwise, a unique arc is selected. The unique arc can be specifically selected (e.g., using run-time information)

<sup>&</sup>lt;sup>4</sup>For the algorithms in this section, it is assumed that the compiler converts all switch statements into the equivalent if-else construct, and program placement information is available at compile time to determine the taken path of a conditional branch.

Figure 8: Justifying signature placement algorithm.

or it can be selected at random. Note that for an unconditional branch, the signature can be placed after the branch for target architectures that always fetch the signature following a branch. The MC68000 is an example of such an architecture [3].

#### 5.2 Reference Signature Placement Algorithm

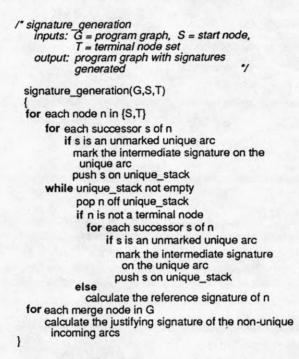

The algorithm for reference signature placement is shown in Figure 9 and its functions are shown in Figure 10. The algorithm places reference signatures so that the maximum distance between any two reference signatures is less than *lmax*. The program control flow graph, G, is effectively an acyclic graph since the terminal nodes break cycles. S and T represent the start node and terminal node set.

The algorithm is a greedy algorithm. Starting from the start node and each terminal node, it

traverses the paths of all successors calculating the maximum path length (step 1). The traversal along each path stops at a terminal node. When the successor of a node makes the path length greater than *lmax*, the current node is marked as a terminal node. The successors of the new terminal nodes are also traversed. The algorithm stops when all arcs have been visited. The reference signatures are then placed at the end of each terminal node (step 2).

During the traversal, when paths merge they are combined in *add\_queue* into one path with the path length set to the maximum path length. In addition, the number of duplicates of the end node, *dups*, is incremented. A merge node is only removed from the queue in *remove\_queue* when all incoming paths have been traversed (i.e., *p.dups* is equal to the number of predecessors of *p.end\_node*).

#### 5.3 Signature Generation Algorithm

The signature generation algorithm is presented in Figure 11. Unique arcs have been identified by the justifying signature placement algorithm. The unique intermediate signatures are marked using a breadth first search. Once all the unique arcs have been marked with their intermediate signatures, the reference signatures are known and the justifying signatures can be calculated as shown in Figure 6 in Section 4.1.2.

#### 5.3.1 Complexity Analysis

For a program graph of N nodes, the complexity of the justifying signature placement algorithm is  $O(N^2)$ . To generate the terminal nodes, loop analysis must be performed. The complexity of the loop generation algorithm is  $O(N^2)$ [1]. Once loop analysis has been performed, N nodes are considered to identify and mark the terminal nodes. To mark the unique arcs, at most 2N - 2 /\* place\_reference\_signatures inputs: G = program\_graph, S = start node, T = partial terminal node set, Imax = 1/2 error detection latency bound outputs: program graph with reference signatures placed no further apart than Imax and the complete terminal node set T \*/

place\_reference\_signatures(G, S, T, Imax)

$p = generate_path(S)$ /\* step 1 \*/ add\_queue(ref\_queue, p) for each terminal node t in T for each successor s of t p = generate path(s)add\_queue(ref\_queue, p) while ref\_queue not empty p = remove\_queue(ref\_queue) if p.length + max(|successors of p.end\_node|) > lmax mark p.end\_node as a terminal node and add to T for each successor s of p.end\_node if p.end\_node is a terminal node new\_p = generate\_path(s) else new\_p = update\_path(s,p) add queue(ref\_queue, new\_p) destroy p for each node in G /\* step 2 \*/ If a terminal node place a reference signature at the end of the node }

Figure 9: Reference signature placement algorithm.

```

/* generate_path

```

input: n = program graph node output: path p which has path length equal to length of n, n, number of duplicates of n initialized to 1

generate path(n)

create p p.length = |n| p.end\_node = n p.dups = 1return p

/\* update\_path inputs: n = program node, p = current path output: a new path, new\_p, which has path length set to length of p + length of n, n, the number of duplicates of n -/ initialized to 1

update\_path(n)

```

create new_p

new_p.length = p.length + |n|

new_p.end_node = n

new_p.dups = 1

return new_p

```

```

/* add_queue

```

3

```

inputs: queue = list of paths, p = path to add

output: queue with either a new path p or an

updated path e that has the same end

node as p. the updated path e has length

set to the maximum length of p and e and

the number of duplicates of the end node

of e is incremented

```

add queue(queue, p)

{

}

for each element e in queue

```

if e.end_node = p.end_node

e.length = max(e.length, p.length)

```

```

e.dups = e.dups + 1

```

```

else

```

```

add p to end of queue

```

```

/* remove_queue

input: queue = list of paths

output: path p whose end node has had

all its incoming arcs visited

```

#### remove queue(queue)

```

p = first element of queue

while p.dups != number of predecessors of p

add p to end of queue

p = first element of queue

return p

}

```

Figure 11: Signature generation algorithm.

merge arcs are considered for a graph with N nodes and an out degree of two.