### ELIMINATING DYNAMIC COMPUTATION REDUNDANCY

# BY

# DANIEL ALEXANDER CONNORS

B.S., Purdue University, 1994 M.S., University of Illinois, 1997

### THESIS

Submitted in partial fulfillment of the requirements for the degree of Doctor of Philosophy in Electrical Engineering in the Graduate College of the University of Illinois at Urbana-Champaign, 2000

Urbana, Illinois

#### ELIMINATING DYNAMIC COMPUTATION REDUNDANCY

Daniel Alexander Connors, Ph.D.

Department of Electrical and Computer Engineering

University of Illinois at Urbana-Champaign, 2000

Wen-mei W. Hwu, Advisor

The traditional method of extracting performance from programs is based on scaling processor resources to execute multiple independent instructions per cycle. In order to enable their cost-effective performance potential, these processors demand that increasing levels of instruction-level parallelism (ILP) be exposed in programs. As a result, compilers must perform increasingly more aggressive analysis and global optimization. Nevertheless, current state-of-the-art compilers cannot expose the level of ILP necessary to overcome the diminishing performance returns of high-issue processors. Ultimately performance becomes limited by the dependences of programs, and not the machine resources. Thus, one of the major challenges to increasing processor performance is overcoming the fundamental dataflow limitation imposed by data dependences. By reusing previous computation results, the dataflow limit can be surpassed for sequences of operations that are otherwise redundantly executed. Effective reuse of previous computation results requires coordinating compiler and hardware techniques in an integrated framework.

Many traditional compiler techniques eliminate program redundancy and optimize the effectiveness of the program. These optimization techniques rely on the detection of static redundancy, which requires computations to be completely redundant for all possible executions. Currently, compiler techniques have no mechanism for capturing dynamic redundancy, redundancy occurring over a temporal set of definitions. As a result, empirical program behavior studies indicate that many instruction traces are dynamically executed with the same inputs, a form of redundancy known as value locality. Such sequences of redundant operations reduce

the effectiveness of ILP processors by wastefully utilizing the multiple functional unit resources. Consequently, the available silicon resources are more effectively allocated to exploiting program redundancy than instruction-level parallelism. This dissertation proposes and investigates architectural and compilation techniques that eliminate dynamic redundancy to improve the resource utilization and performance.

The four key technologies here presented work in a coordinated fashion to eliminate dynamic redundancy from program execution. The Reusable Computation Region Framework (RCRF) provides a compilation framework to accurately determine the regions, called Reusable Computation Regions (RCRs), of a program in which reuse is likely to occur. Generally, these regions are recurring tasks and invariant computations that represent the redundant execution behavior occurring within general purpose programs. By locating and designating these regions at compile time, effective run-time techniques for directing the reuse of computation results can be achieved. To exploit the execution behavior of these regions, this dissertation introduces a reuse approach, called Compiler-directed Computation Reuse (CCR). The CCR approach integrates compiler and architecture techniques to exploit value locality for large regions of code. In this approach, the Instruction Set Architecture (ISA) provides a simple interface for the compiler to communicate the run-time execution of each region into a hardware structure.

The RCRF techniques can identify redundantly executing regions within programs based on analyzing value-profile execution information gathered using training input evaluations. However, since most modern software environments do not support value profiling, static region formation techniques are also developed. To support static region formation in the compile-time techniques, it becomes necessary to add run-time management support to the CCR approach. The Dynamic Computation Management System (DCMS) enhances the effectiveness

of compiler-directed computation reuse by dynamically controlling deployment of statically-selected computation regions by gathering run-time program execution behavior. In addition, program invariance and computation redundancy occur in phases during run-time execution, and compile-time reuse decisions need to adapt to program behavior and contention for the reuse resources. The DCMS uses hardware tables to gather run-time execution behavior to enable accurate allocation policies of the computation reuse buffer. Within the given framework, the DCMS can determine which compiler-selected computations are currently best exploited using a processor's reuse resources.

Finally, a class of computation regions formed by the RCRF can be exploited using compiler transformation and existing architecture support. In the compiler-based Value Optimization Framework (VOF), program reformulation and predicated execution-based value transformations are used to exploit the redundancy of regions. These techniques offer alternatives for the compiler to synthesize codes based on data distribution rather than traditional practice of basic program conversion.

The Reusable Computation Region Framework, the Compiler-directed Computation Reuse Approach, and the Dynamic Computation Management System represent a fundamentally new method of controlling the microarchitecture execution engine of processors to improve program performance. The compiler-based Value Optimization Framework illustrates a new compiler methodology for synthesizing code based on data distribution. Systematically coordinating these compiler techniques and hardware technologies can eliminate significant amounts of the dynamic computation redundancy in program execution. These techniques are new methods of improving modern processor utilization and performance by exploiting readily available program value locality characteristics.

# **DEDICATION**

Dedicated to my mother, father, sister, and brother.

### ACKNOWLEDGMENTS

First and foremost, I would like to thank my advisor, Professor Wen-mei Hwu, for his guidance throughout my graduate studies. Most importantly, I would like to thank him for his patience and understanding. Several occasions I know I truly depended on his advice and his insight. I would also like to thank him for providing me with every opportunity to achieve my dream of becoming a professor. I am grateful for his kindness and hope I can continue to illustrate the positive influence he has had on my life.

Next, I would like to extend my gratitude to the members of my dissertation committee, Professor Nicholas Carter, Professor Steven Lumetta, Dr. Scott Mahlke, and Professor David Padua. Their numerous insights, questions, and suggestions improved the quality of this work immensely. Also, I would like to thank Jim Pierce, Allan Knies, and Dan Lavery at the Intel Corporation; their suggestions had a strong influence on the directions of this work. Mateo Valero provided me with both insight on my research and many opportunities to advance my experience in the computer architecture field. Yale Patt was a great influence on my career. I have been fortunate to learn on many different levels from all of Yale's numerous experiences.

I feel extremely fortunate to have been part of the IMPACT research group. My thesis research truly would not have been possible without the support, hard work of the members of the IMPACT research group. Members of the group were always there to discuss ideas, debate solutions, practice talks, and develop software. I feel extremely fortunate to have been a part of this group. There are several group members that I wish to thank. David August, Ben-Cheng Chung, Rick Hank, Teresa Johnson, Brian Deitrich, John Sias, and John Gyllenhaal provided

invaluable feedback on ideas, papers, and talks. Kevin Crozier, Jeff Monks, Ron Barnes, and Matt Merten made office life enjoyable with their thoughts and discussions. I would also like to specially thank David August and John Sias for developing the predicate-based optimization framework used within this thesis. Lastly, I would like to thank Rick Hank for being my mentor when I first entered the IMPACT research group. Rick served as a great model for me and I wish I had more time to learn from his experience and abilities.

Most importantly, I would like to acknowledge the support of my friends and family. Tammy Rohrbaugh Knoblock helped inspire me to begin the long but worthwhile journey of my development as a professor. Steve Gemelos, Larry Chambers, Marty McKenna, and Krishna Bandaru provided many good times and friendship throughout my life. Jenny Carman Johnson was an incredible influence on who I am today and who I will try to continue to be in the future. I would like to thank Margaret Carns Manuel, a dear friend who always supported me in everything I did. I share incredible connections with Jaymie Braun Oehler, Jake Janovetz, Qudus Olaniran, and Teresa Johnson, all of whom are close friends with whom I have shared some of the best experiences. I thank Jean-Michel Puiatti for simply being himself, a wonderful and amazing person with great insight on how to live life, and a person who continues to teach me about what is important in life. I would like to thank Gigi Gogliotti for being a great friend and always listening to me whenever I needed to talk. Likewise, Hillery Hunter helped restore my balance whenever I started to wander off the path of reason. Similarly, at those times, the charm and kindness of Marie-Pierre Lassiva-Moulin gave me a reason everyday to come into the office and work. Sanjay Patel restored my appreciation for intelligent well-rounded people in the engineering field, and it is near tragic that I did not get to meet him until late in my graduate career. The friendship I share with Scott Mahlke and David August is incredibly

unique and has provided me with great experiences and laughter. I am incredibly thankful for the connections I share with Scott and David. One of the best parts of my experience at the University of Illinois was getting to know Sabrina Hwu and being part of the entire Hwu family. My life would not be the same without her support and friendship.

Finally, I would like to express my heart-felt thanks to my family. My mother, Ann, my sister, Melody, and my brother, Mel, gave me the encouragement and consistent support that I needed to make it through graduate school. My thesis is dedicated in part to the life I have completely shared with them. Lastly, I would like to acknowledge the love and memory of my father, Melvin Francis Connors.

# TABLE OF CONTENTS

| CI | HAPT              | $\Gamma 	ext{ER}$                                 | PAGE |

|----|-------------------|---------------------------------------------------|------|

| 1  | INT<br>1.1<br>1.2 | RODUCTION                                         | 5    |

| 2  | REI               | DUNDANCY OF PROGRAM EXECUTION                     | 8    |

|    | 2.1               | Dynamic Redundancy                                | 9    |

|    | 2.2               | Sources of Value Locality                         | 10   |

|    |                   | 2.2.1 Data redundancy                             | 10   |

|    |                   | 2.2.2 Programming models                          | 11   |

|    |                   | 2.2.3 Application domain                          | 11   |

|    |                   | 2.2.4 Software distribution model                 | 12   |

|    | 2.3               | Value Locality Characteristics in Programs        | 13   |

|    |                   | 2.3.1 Value profiling                             | 14   |

|    |                   | 2.3.2 Reuse Profiling System (RPS)                |      |

|    |                   | 2.3.3 Invariance                                  | 21   |

|    |                   | 2.3.4 Instruction reuse                           | 24   |

|    | 2.4               | Related Work                                      | 30   |

| 3  | CON               | MPUTATION REGION FRAMEWORK                        | 34   |

| 9  | 3.1               | Motivation                                        |      |

|    | 9.1               | 3.1.1 Reuse region opportunities                  |      |

|    |                   | 3.1.2 Computation reuse potential                 |      |

|    | 3.2               | Compiler Support for Reusable Computation Regions |      |

|    | 9.2               | 3.2.1 Deterministic computation                   |      |

|    |                   | 3.2.2 Interprocedural memory disambiguation       |      |

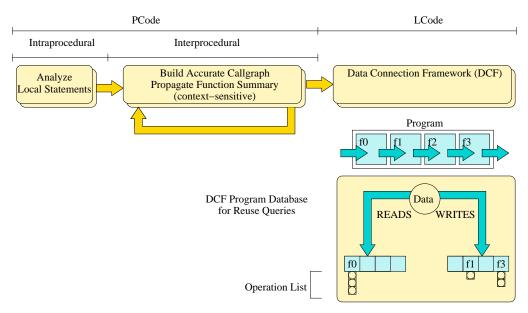

|    |                   | 3.2.3 Data Connection Framework (DCF)             |      |

|    |                   | 3.2.4 Reusable computation regions (RCRs)         |      |

|    |                   | 3.2.5 Computation region formation                |      |

|    | 3.3               | Profile-Guided Computation Region formation       |      |

|    | ა.ა               | 3.3.1 Reuse selection policy                      |      |

|    |                   | 3.3.2 Enhancing profile-guided region formation   |      |

|    | 3.4               | Static Computation Region formation               |      |

|    | J.4               | 3.4.1 Inferred computation regions                |      |

|    |                   | 3.4.1 Interred computation regions                |      |

|    | 3.5               | Computation Region Summary                        |      |

|    | 0.0               | Comparation Region Dummary                        |      |

| 4 | COI | MPILER-DIRECTED COMPUTATION REUSE APPROACH 7                             | 75         |

|---|-----|--------------------------------------------------------------------------|------------|

|   | 4.1 | Introduction                                                             | 75         |

|   | 4.2 | Motivation                                                               | 76         |

|   | 4.3 | Architecture Support                                                     | 7 <u>9</u> |

|   |     | 4.3.1 Computation Reuse Buffer design                                    | 30         |

|   |     | 4.3.2 Instruction set extensions                                         | 32         |

|   |     | 4.3.3 CCR microarchitecture                                              |            |

|   | 4.4 | CCR Compiler Support                                                     |            |

|   | 4.5 | Experimental Evaluation                                                  |            |

|   |     | 4.5.1 Methodology                                                        |            |

|   |     | 4.5.2 Experimental results                                               |            |

|   | 4.6 | CCR Summary                                                              |            |

| 5 | DYI | NAMIC COMPUTATION MANAGEMENT SYSTEM                                      | 19         |

|   | 5.1 | Introduction                                                             |            |

|   | 5.2 | Motivation                                                               |            |

|   | 5.3 | Dynamic Computation Management System                                    |            |

|   | 0.0 | 5.3.1 Reuse Sentry                                                       |            |

|   |     | 5.3.2 Evaluation Buffer                                                  |            |

|   |     | 5.3.3 Reuse Monitoring System                                            |            |

|   | 5.4 | Experimental Evaluation                                                  |            |

|   | 9   | 5.4.1 Methodology                                                        |            |

|   |     | 5.4.2 Experimental results                                               |            |

|   | 5.5 | Summary                                                                  |            |

| 6 | VAI | UE OPTIMIZATION FRAMEWORK                                                | <b>1</b> 9 |

|   | 6.1 | Introduction                                                             |            |

|   | 6.2 | Related Work and Architecture Support                                    |            |

|   | 6.3 | Value-Based Compiler Reformulation Motivation                            |            |

|   | 0.0 | 6.3.1 Dataflow transformation                                            |            |

|   |     | 6.3.2 Memory flow transformation                                         |            |

|   |     | 6.3.3 Advanced predicate optimization                                    |            |

|   | 6.4 | Compiler Framework                                                       |            |

|   |     | 6.4.1 Coordination of compiler-based and compiler-directed techniques 17 |            |

|   |     | 6.4.2 Value Optimization Framework                                       | 30         |

|   | 6.5 | Experimental Evaluation                                                  |            |

|   |     | 6.5.1 Methodology                                                        |            |

|   |     | 6.5.2 Results and analysis                                               |            |

|   | 6.6 | Summary                                                                  |            |

| 7 | COI | NCLUSION                                                                 | )C         |

| 1 | 7.1 | Summary                                                                  |            |

|   | 7.1 | v                                                                        |            |

|   | 1.2 | Future Research                                                          | )1         |

|   | REI | FERENCES                                                                 | )5         |

|   | ИТ  | Λ                                                                        | 1 1        |

# LIST OF TABLES

| Tabl                                                      | e                                                              | Page                 |

|-----------------------------------------------------------|----------------------------------------------------------------|----------------------|

| 2.1<br>2.2<br>2.3<br>2.4                                  | Benchmarks descriptions                                        | . 19                 |

| 3.1<br>3.2<br>3.3<br>3.4<br>3.5                           | Region formation statistics based on profile-guided techniques | . 68<br>. 71<br>. 74 |

| <ul><li>4.1</li><li>5.1</li><li>5.2</li><li>5.3</li></ul> | Hardware cost expressions and cost for models evaluated        | . 138<br>. 140       |

| 6.1<br>6.2<br>6.3                                         | Predicate definition truth table                               | . 189                |

# LIST OF FIGURES

| Figu                | re                                                                                                                                                                      | Page         |

|---------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------|

| 2.1<br>2.2<br>2.3   | Illustration of dynamic computation redundancy                                                                                                                          | . 16         |

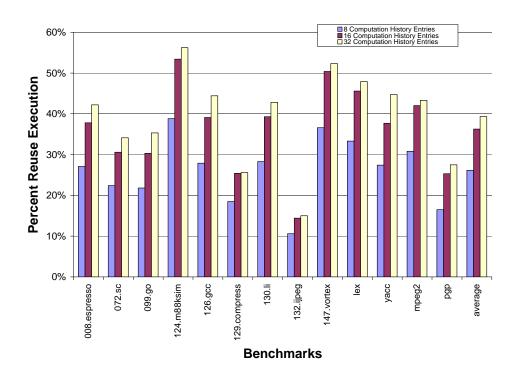

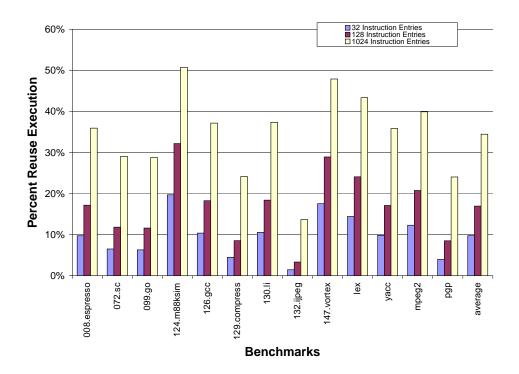

| 2.4<br>2.5<br>2.6   | Distribution of parameter repetition due to top five most frequently executed sets. Percentage of instruction execution reused for history sizes: 8, 16, and 32 entries | . 25         |

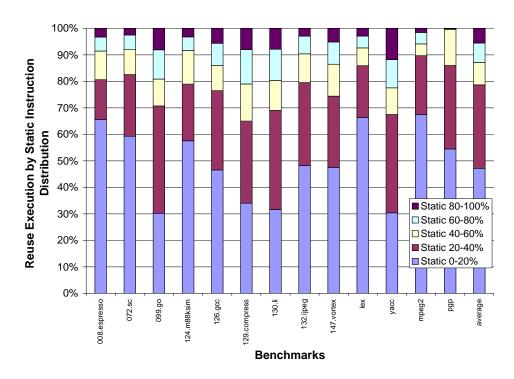

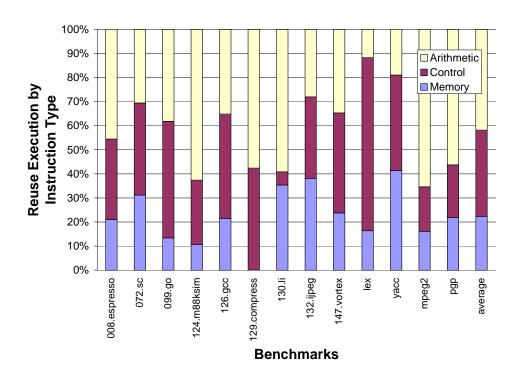

| 2.7<br>2.8<br>2.9   | Reuse execution based on static distribution of instructions                                                                                                            | . 27<br>. 28 |

| 2.10                | reuse                                                                                                                                                                   | . 29         |

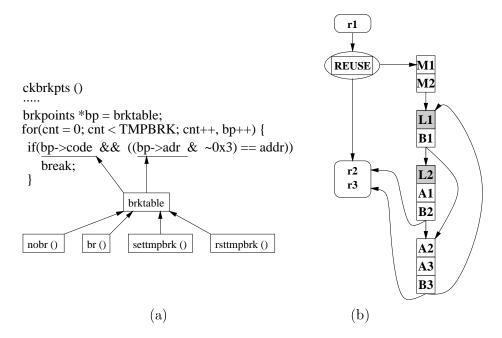

| 3.1                 | Trace-level reuse example source code macro definition (a), dependence graph (b), and potential reuse sequence (c)                                                      | . 36         |

| 3.2                 | Loop example with potential reuse                                                                                                                                       | . 39         |

| 3.3                 | Region-level reuse example (a) source code and (b) reuse sequence                                                                                                       |              |

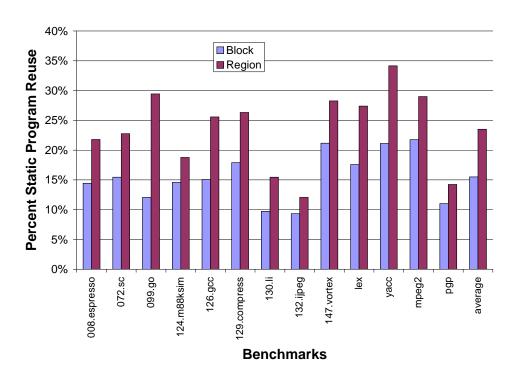

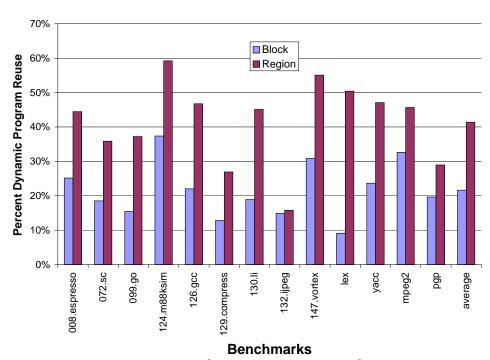

| 3.4                 | Static percentage of program with region reuse potential                                                                                                                |              |

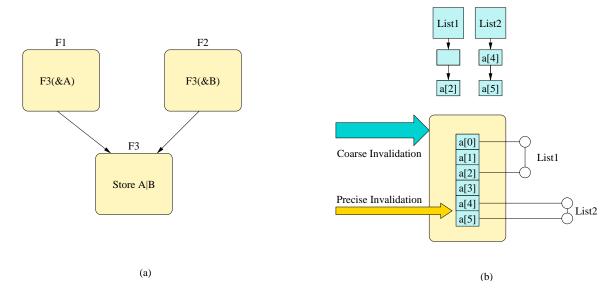

| $3.5 \\ 3.6$        | Dynamic percentage of program execution with region reuse potential Use of compiler analysis in computation redundancy results in two potential false                   | . 41         |

| 3.7                 | conflicts: context based (a) and dynamic-structure (b)                                                                                                                  | . 45         |

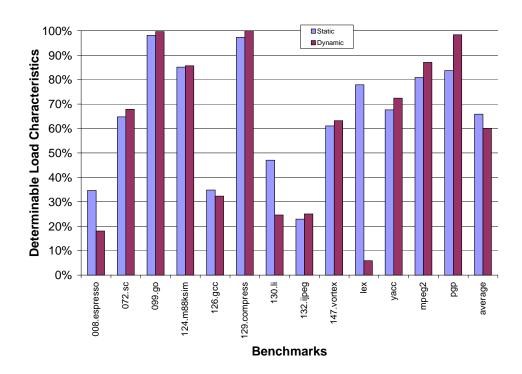

|                     | minable for load instructions                                                                                                                                           | . 46         |

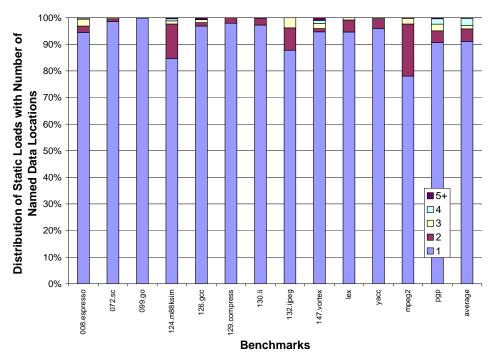

| 3.8                 | Static breakdown of named data locations for load instructions                                                                                                          | . 47         |

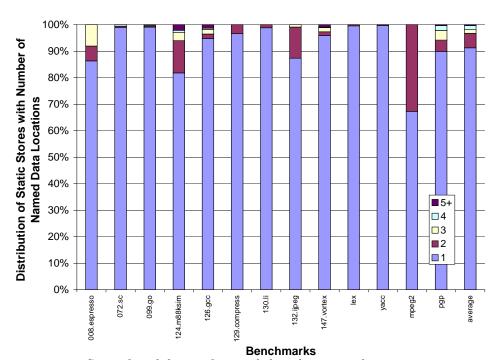

| 3.9<br>3.10<br>3.11 | Static breakdown of named data locations for store instructions                                                                                                         |              |

|                     | (c)                                                                                                                                                                     | . 50         |

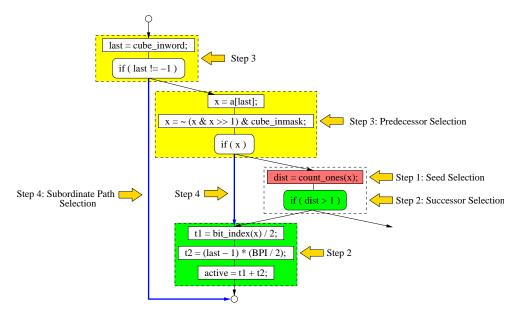

| 3.12                | Function for selecting successor reuse instruction                                                                                                                      | . 54         |

| 3.13                | Algorithm for selecting reusable computation regions.                                                                                                                   | . 57         |

| 3.14                | Region formation example for the function $\_cactive$ of benchmark $008.espresso$                                                                                       | . 58         |

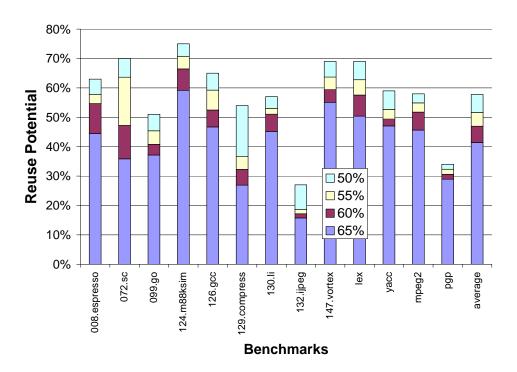

| 3.15                | Dynamic reuse potential based on reuse layering thresholds                                                                                                              | . 64         |

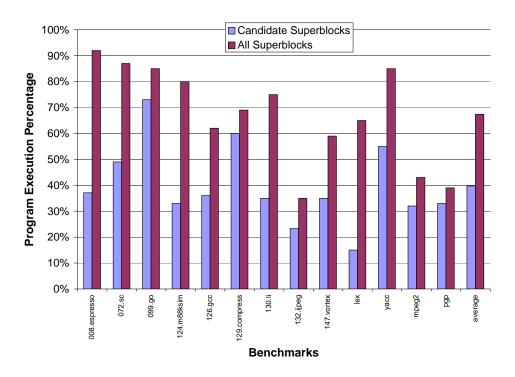

| 3.16                | Distribution of dynamic execution in candidate superblocks and all superblocks                                                                                          | . 66         |

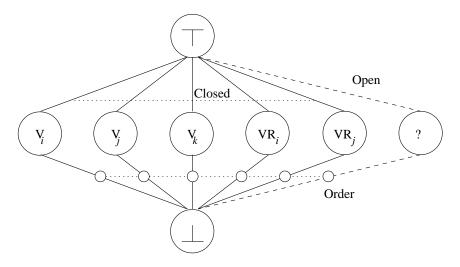

|                     | The value relation inference lattice                                                                                                                                    | . 69         |

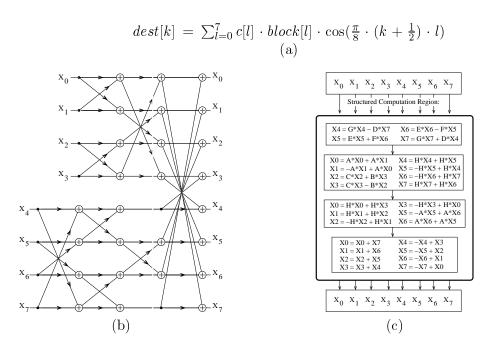

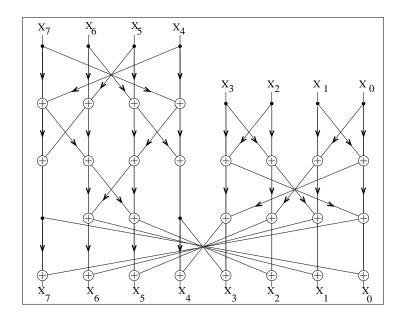

| 3.18                | Structural identification of computation region, MPEG2 IDCT code (a), dependence graph (b), and computation (c)                                                         | . 72         |

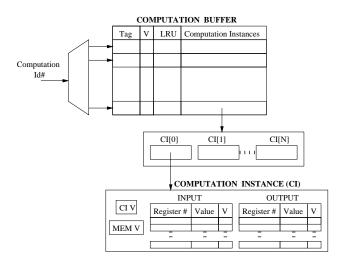

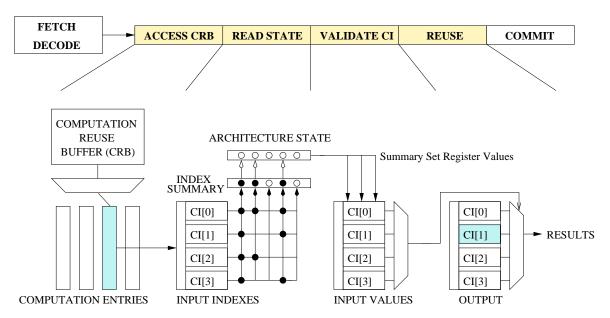

| 4.1                 | Computation Reuse Buffer (CRB) design                                                                                                                                   | . 81         |

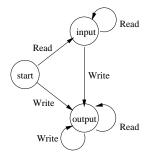

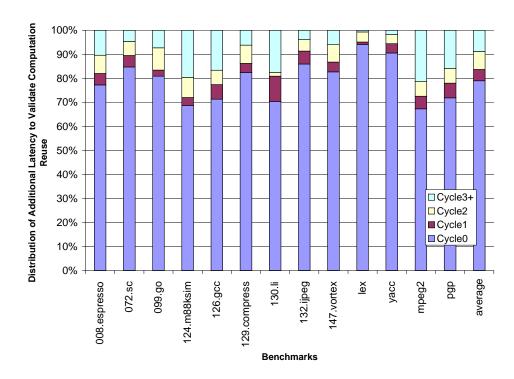

| 4.2  | State transition diagram for recording register contents during memoization mode       | 85  |

|------|----------------------------------------------------------------------------------------|-----|

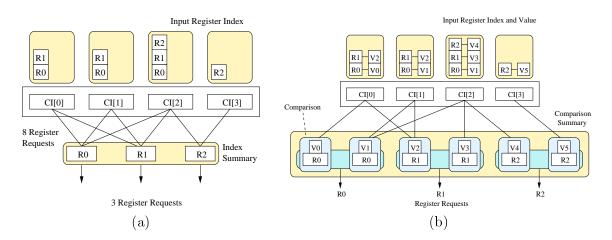

| 4.3  | CCR microarchitecture pipeline                                                         | 86  |

| 4.4  | Methods of summarizing computation instances for verification: index summary (a),      |     |

|      | index and comparison summary (b)                                                       | 88  |

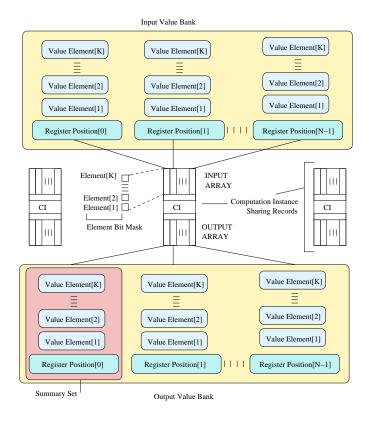

| 4.5  | Shared-Instance CRB design                                                             | 90  |

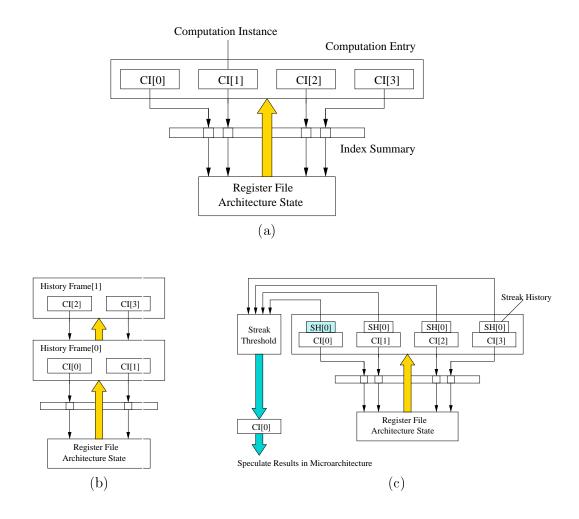

| 4.6  | Verification of computation instance, base model (a), history-based model (b), and     |     |

|      | computation anticipation (c)                                                           | 93  |

| 4.7  | Algorithm for selecting prioritized reusable computation regions                       | 96  |

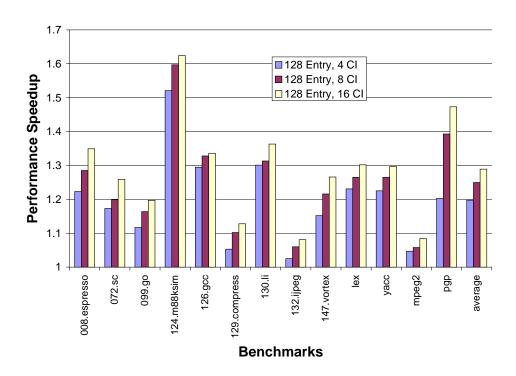

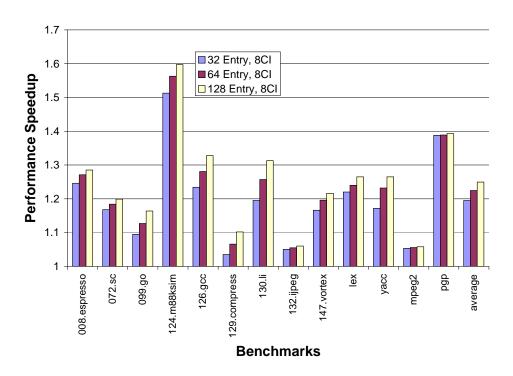

| 4.8  | Speedup for processor with CCR support varying the number of instances                 | 99  |

| 4.9  | Speedup for processor with CCR support varying the number of entries                   | 100 |

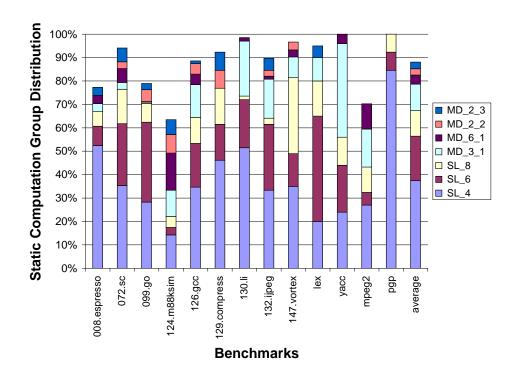

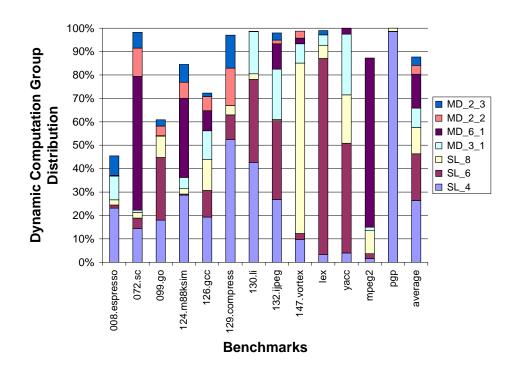

| 4.10 | Computation group static distribution                                                  | 102 |

| 4.11 | Computation group dynamic distribution                                                 | 103 |

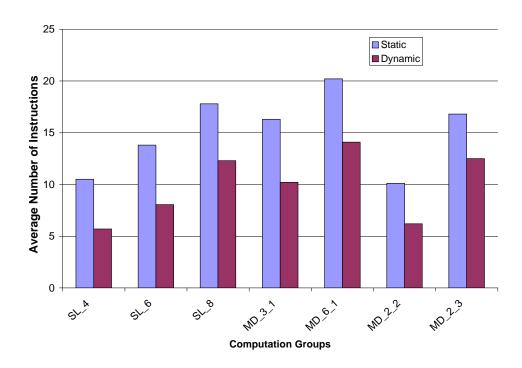

| 4.12 | Average number of instructions reused per each computation group                       | 104 |

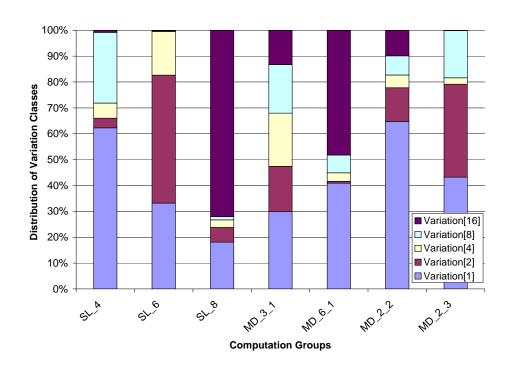

| 4.13 | Computation group variation behavior                                                   | 105 |

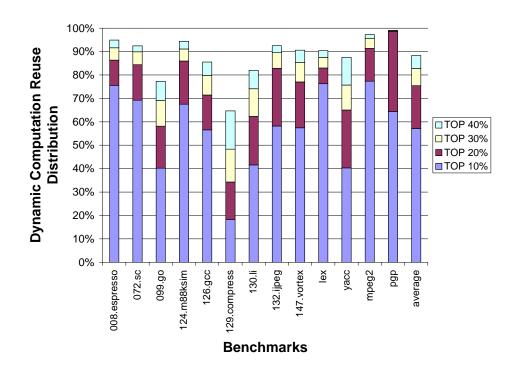

|      | Dynamic reuse distribution                                                             |     |

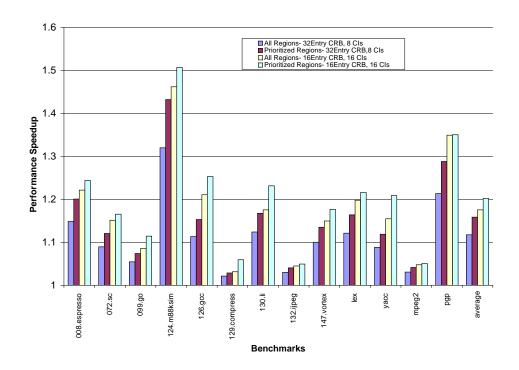

| 4.15 | Compiler allocated computation regions based on priority                               | 107 |

| 4.16 | Performance degradation for increased computation validation latency                   | 108 |

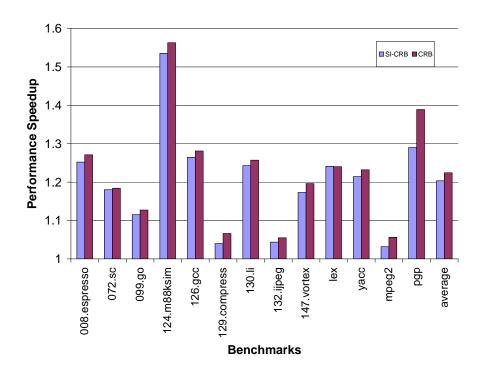

| 4.17 | Speedup for the base CRB model and SI-CRB model over base architecture                 | 109 |

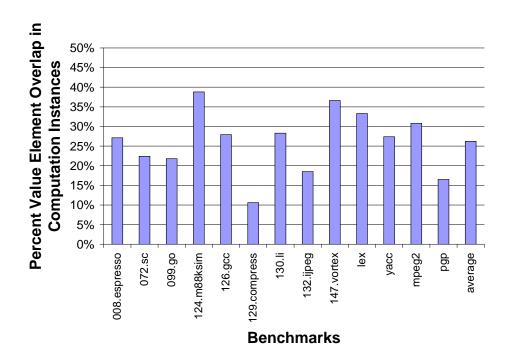

| 4.18 | Percent overlap of computation region register values with regions already occupying   |     |

|      | CRB                                                                                    | 110 |

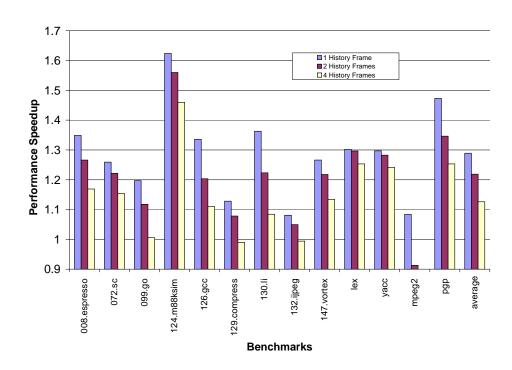

| 4.19 | Performance of history-based computation instance array                                | 111 |

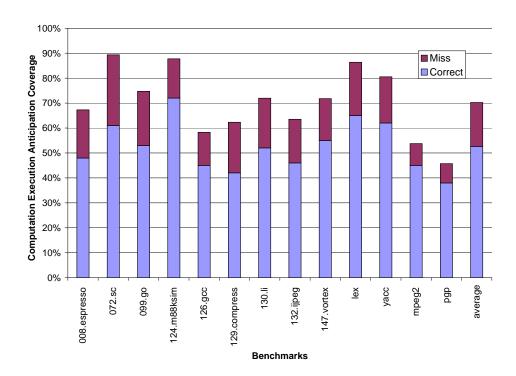

| 4.20 | Accuracy of anticipating computation instance execution behavior                       | 112 |

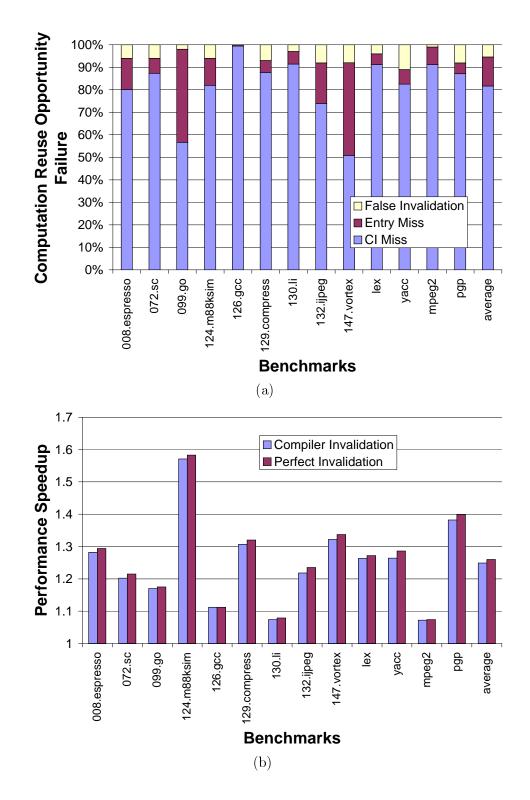

| 4.21 | Distribution of computation reuse conflicts (a) and speedup assuming perfect compiler- |     |

|      | directed memory invalidation (b)                                                       | 113 |

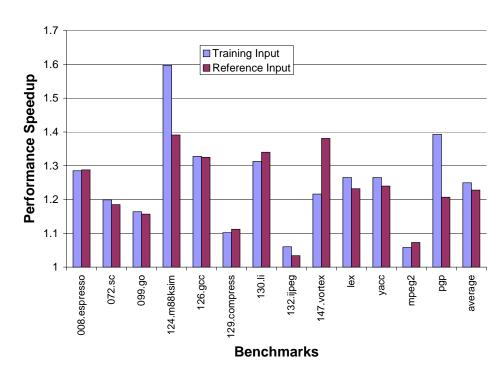

| 4.22 | Performance for training and reference input data sets                                 | 114 |

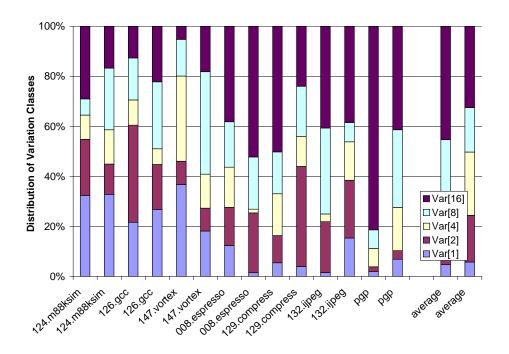

| 4.23 | Variation of computation instance behavior for multiple input sets                     | 115 |

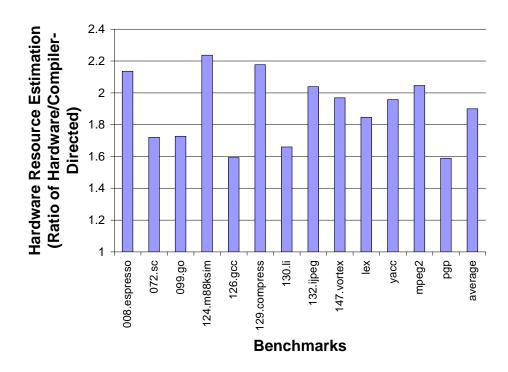

| 4.24 | Resource estimation for hardware exploitation of regions                               | 117 |

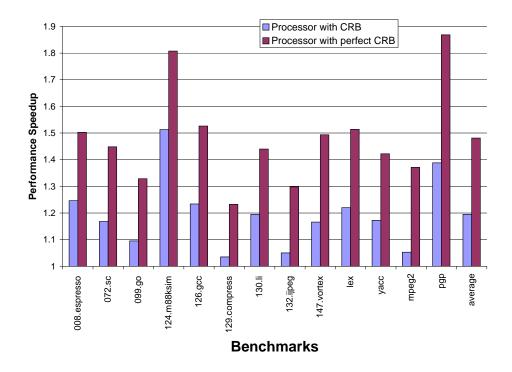

| 5.1  | Performance for processor with base 32-entry CRB and perfect CRB                       | 122 |

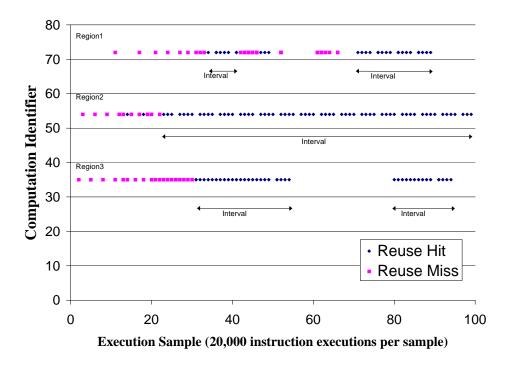

| 5.2  | Computation regions executed for $008.espresso$ . Each data point indicates either a   |     |

|      | computation reuse miss, computation reuse hit, or no computation reuse attempt         | 123 |

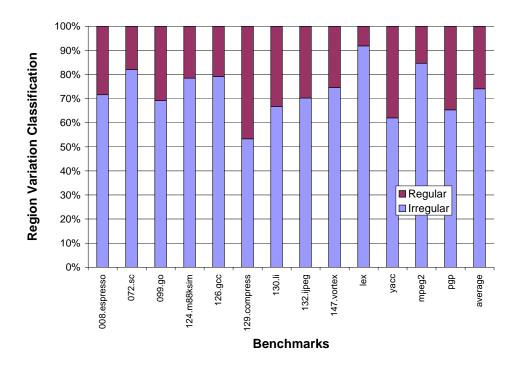

| 5.3  | Computation region variation behavior                                                  | 126 |

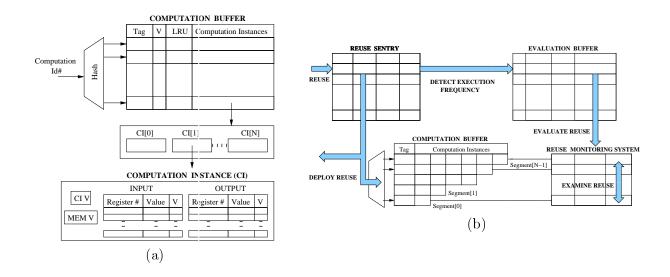

| 5.4  | The Computation Reuse Buffer (a) and the Dynamic Computation Management                |     |

|      | System support (b)                                                                     | 128 |

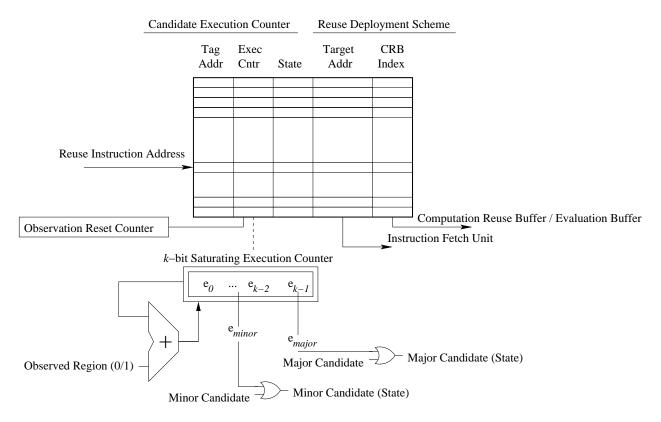

| 5.5  | Reuse Sentry hardware                                                                  | 129 |

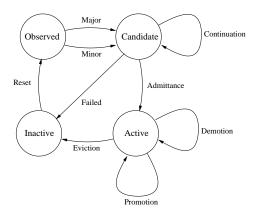

| 5.6  | Region states and transitions                                                          | 130 |

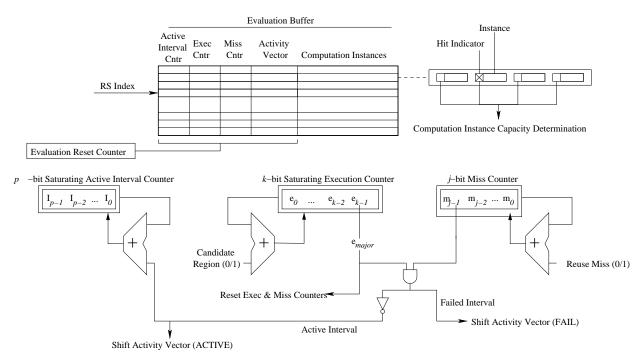

| 5.7  | Evaluation Buffer hardware                                                             | 133 |

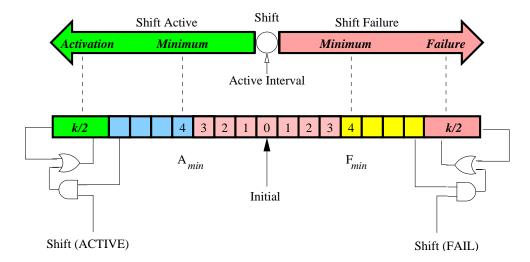

| 5.8  | Activity vector                                                                        | 134 |

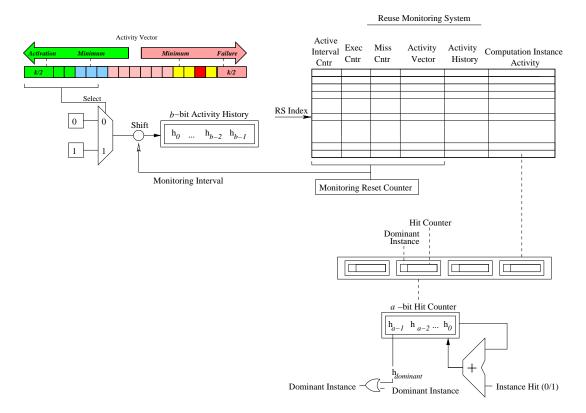

| 5.9  | Reuse Monitoring System hardware                                                       | 137 |

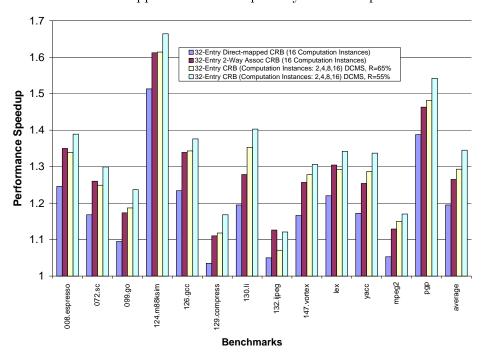

| 5.10 | Performance for CRB and DCMS models                                                    |     |

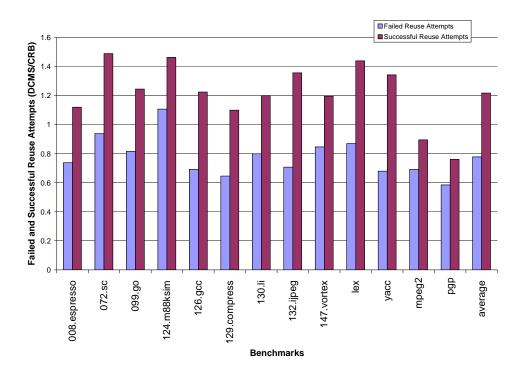

| 5.11 | Comparison of reuse attempts for the CRB and DCMS models                               |     |

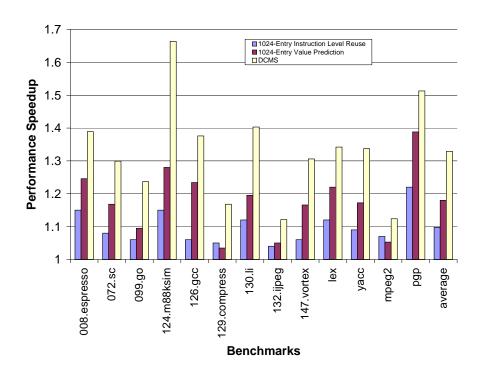

|      | Performance for DCMS, instruction reuse (IR), and value prediction (VP)                |     |

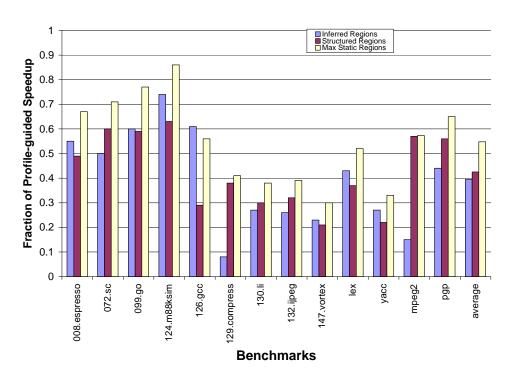

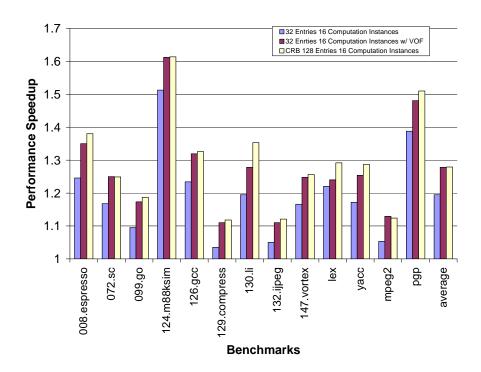

|      | Performance for static region identification techniques                                |     |

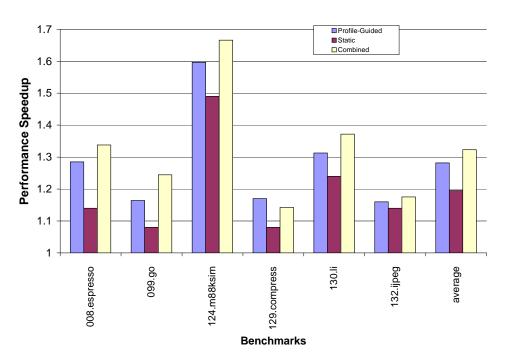

|      | Performance for combining profile-guided and static region identification methods      |     |

|      | on untrained input set                                                                 | 145 |

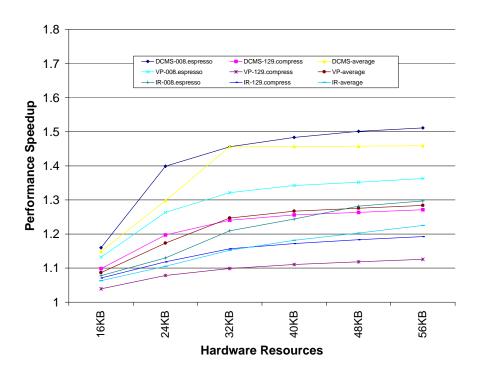

| 5.15 | Performance when varying levels of hardware resources for DCMS, instruction reuse (IR), and value prediction (VP) |

|------|-------------------------------------------------------------------------------------------------------------------|

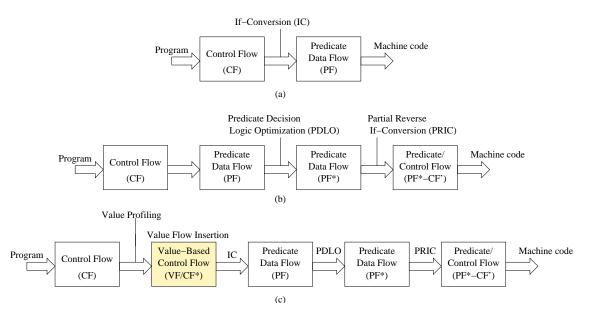

| 6.1  | Program flow-graph transformation paths                                                                           |

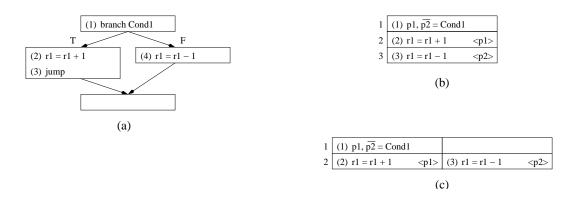

| 6.2  | An example code segment (a), after if-conversion (b), and after scheduling (c) 158                                |

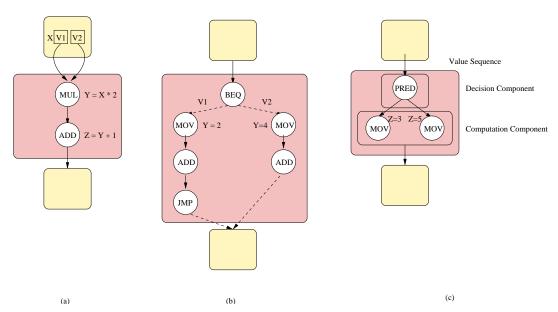

| 6.3  | Code for one variable <i>closed</i> region: dataflow representation (a), value-transformed                        |

|      | control flow representation (b), and value-transformed dataflow representation (c) 162                            |

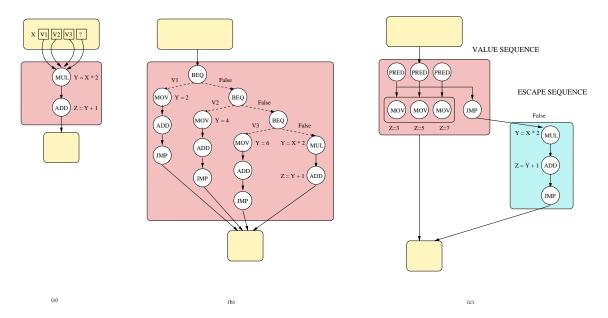

| 6.4  | Code for one variable open region: dataflow representation (a), value-transformed                                 |

|      | control flow representation (b), and value-transformed dataflow representation (c) 164                            |

| 6.5  | Execution distribution of silent store instructions                                                               |

| 6.6  | Fundamental conversion of memory flow (a) to control flow representation (b), and                                 |

|      | then to value-based predicate dataflow (c)                                                                        |

| 6.7  | Example of memory flow transformation for 126.gcc, showing the original code (a),                                 |

|      | the original dependence graph (b), the value-transformed predicate-asserted depen-                                |

|      | dence graph (c)                                                                                                   |

| 6.8  | MPEG2 IDCT dependence graph                                                                                       |

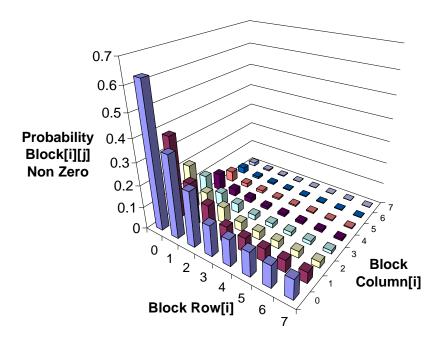

| 6.9  | Nonzero value distribution of DCT blocks of MPEG compressed video                                                 |

| 6.10 | MPEG reformulation of degree-8 vectors with the three open value vectors, control                                 |

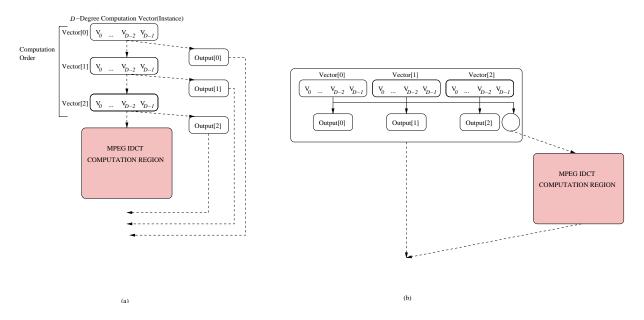

|      | flow representation of value-transformed code (a), and dataflow representation of                                 |

|      | value-transformed code (b)                                                                                        |

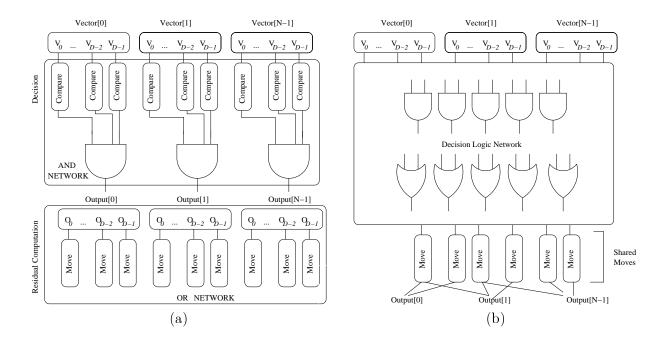

| 6.11 | Process of decision logic optimization, original logic network (a) and optimized de-                              |

|      | cision logic network(b)                                                                                           |

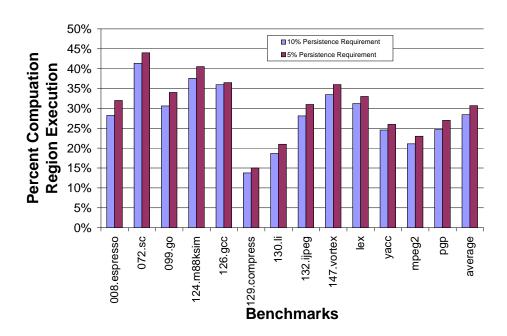

|      | Computation region execution with persistent vector characteristics                                               |

| 6.13 | Value-transformed sequence for population count example of 008. espresso, a degree-                               |

|      | 1 region with an open order-3 value transform                                                                     |

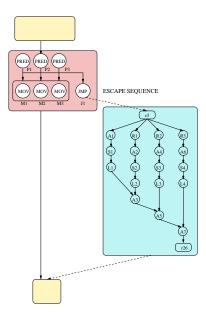

|      | Static schedules for the 008 espresso value and escape sequence                                                   |

|      | Static schedules for the 008.espresso using PRIC techniques                                                       |

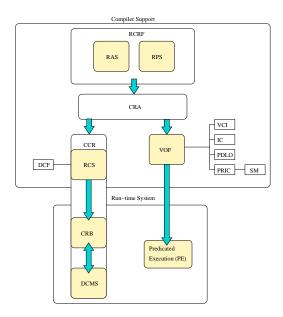

|      | Overview of applying compiler-based and compiler-directed techniques                                              |

|      | Algorithms for value optimization techniques                                                                      |

| 6.18 | Method of scheduling escape sequence instruction using partial reverse if-conversion                              |

|      | methodology                                                                                                       |

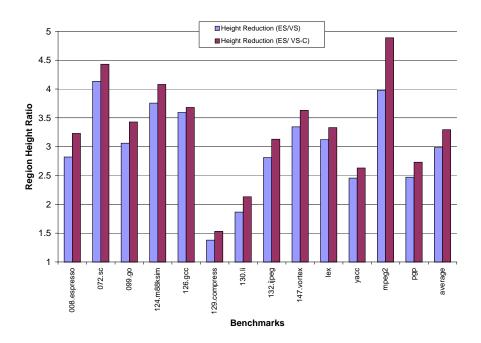

|      | Average relative height reduction for dataflow transformed regions                                                |

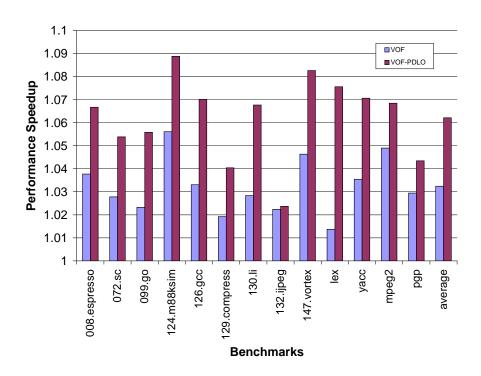

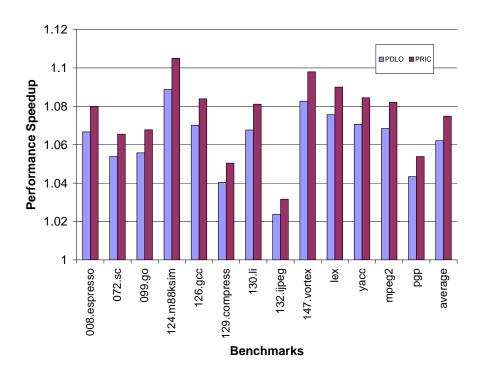

|      | Performance for VOF and VOF-PDLO optimization                                                                     |

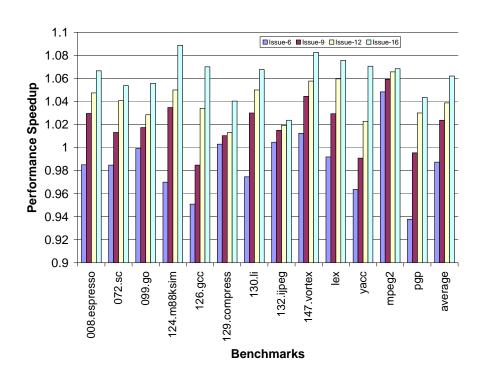

|      | Evaluation of PDLO speedup for different machine models                                                           |

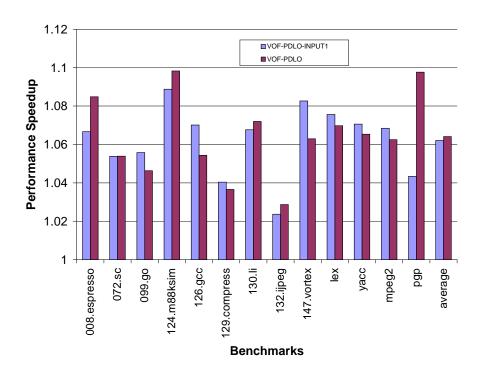

|      | Evaluation of VOF-PDLO speedup for different input sets                                                           |

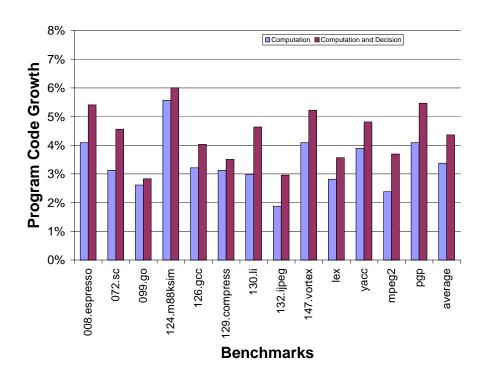

|      | Code growth for applying value transforms                                                                         |

|      | Performance for VOF-PDLO and VOF-PDLO-PRIC                                                                        |

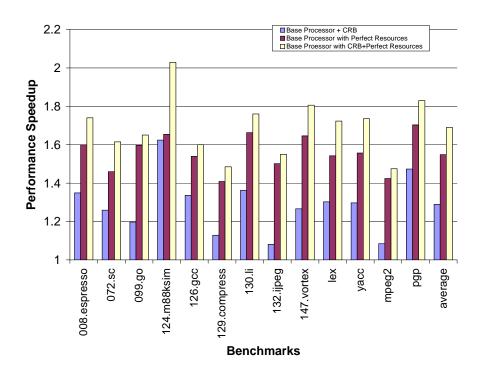

| 6.25 | Performance comparing CCR models when coordinating compiler-based and compiler-                                   |

| 0.00 | directed techniques                                                                                               |

| 6.26 | Performance comparing benefits of compiler-based and compiler-directed techniques                                 |

|      | when varying machine resources                                                                                    |

# CHAPTER 1

#### INTRODUCTION

The performance of an application on a modern processor is dominated by the level of compiler optimization. Generally, optimizing compilers are successful at eliminating inefficiencies and redundancies within programs by performing iterations of analysis and optimization. Static analysis techniques allow a large scope of a program to be considered and increase the available optimization opportunities. The elimination of redundancies in programs at compile time can dramatically improve a program's execution time. Traditional compiler techniques such as constant propagation, common subexpression elimination, loop invariant code removal, conditional branch elimination, and partial redundancy elimination [1] eliminate program redundancy and improve the efficiency of a program. However, compiler optimization techniques rely on the detection of static redundancy, which requires the complete assertion that the computations be definitely redundant for all executions. As such, compiler techniques have no mechanism for capturing dynamic redundancy, redundancy occurring over a temporal set of definitions. As a result of the deficiencies of compiler optimization, based on various types of applications, empirical program behavior studies indicate that many instruction traces are dynamically executed with the same inputs, a form of redundancy known as value locality [2], [3], [4], [5]. Overall, optimizing compilers are only able to make existing programs operate more efficiently on processors, and they fail to reformulate the program and transform the original algorithm to the most effective form. As such, optimizing compilers eliminate only a small portion of the overall redundancy of program execution.

The performance of an application on modern processors is also highly dependent on the ability to execute multiple instructions per cycle. In order to enable their cost-effective performance potential, these processors demand that increasing levels of instruction-level parallelism (ILP) be exposed in programs. As a result, compilers must perform increasingly more aggressive analysis and global optimization. Nevertheless, current state-of-the-art compilers cannot expose the level of ILP necessary to eliminate the diminishing performance returns of high-issue processors. Ultimately performance becomes limited by the dependences of programs, and not the machine resources. Thus, one of the major challenges to increasing processor performance is overcoming the fundamental dataflow limitation imposed by data dependences. By reusing previous computation results, the dataflow limit can be surpassed for sequences of operations that are otherwise redundantly executed.

As the availability of silicon increases, it makes sense to develop techniques to intelligently reduce the amount of redundancy or value locality in program execution. Several other fundamental architectural mechanisms are based on exploiting similar aspects of program behavior. Branch predictors [6] often occupy a fairly significant portion of the chip area and are critical for reducing the branch misprediction stalls. Generally, branch predictors are developed to exploit the predictability and correlation of branch execution behavior. Similarly, cache memory systems [7], [8] seek to exploit the locality characteristics found in memory references. By storing a referenced item, caches exploit temporal locality, the tendency for that item to be re-referenced soon. Additionally, by storing multiple items adjacent to the referenced item, caches exploit spatial locality, the tendency for neighboring items to be referenced soon. The exploitation of

value locality of the program execution may provide substantial improvement to application performance on modern processors.

This dissertation introduces compiler-directed computation redundancy elimination, an approach that allows the compiler to identify code regions whose computation can be reused during dynamic execution. In a compiler-directed approach, the compiler essentially partitions the program into a set of units, called reusable computation regions. The compiler may determine the regions based on profiling information or static formation techniques. The use of profiling information to determine region contents allows the compiler to select units that accurately reflect the dynamic behavior of the program and are more likely to benefit from reuse. As a result, the compiler may be able to detect the most likely sequences of reuse. Unfortunately, there are several drawbacks to profiling. As such, for the compiler-directed mechanism to be successful, it is necessary to statically estimate the reuse potential of program regions. This dissertation deals with both concepts of profile-directed and static-based computation region formation.

In the compiler-directed mechanism proposed by this dissertation, the instruction set architecture provides a simple interface for the compiler to communicate the scope of each reuse region and its live-out register information to the hardware. During run time, the micro-architectural components of the approach record the execution results of the regions for potential reuse. Explicit designation of computation reuse allows a large number of dynamic control, memory, and arithmetic instructions to be jointly considered for reuse in the compiler-directed framework. The fundamental responsibility for detecting reusable sequences of code is placed on the compiler and the basic action of reusing the results of the sequence of the code is enabled through hardware. However, variations in program behavior cause the static designation

of computation regions to reduce the effectiveness of the compiler-directed hardware approach. For instance, program invariance and computation redundancy occur in phases during run-time execution, and compile-time reuse decisions need to adapt to program behavior and contention for the reuse resources. Similarly, program invariance is highly related to input sets and the modes of particular applications, thus requiring methods of controlling the deployment of the compiler selected regions. Dynamic management hardware structures can gather run-time execution behavior and enable allocation policies of the computation reuse buffer. Within the dynamic framework, run-time decisions can determine which compiler selected computations are currently best exploited using the processor's reuse resources.

Many of the computation regions exploited through the compiler-directed hardware have persistent value locality characteristics that can be exploited using compiler transformation and existing architecture support. In the compiler-based value optimization framework, predicated-execution-based program transformations are used to exploit the redundancy of regions. These techniques offer venues for the compiler to synthesize codes based on value distribution within processors that do not offer hardware support for computation reuse.

This dissertation proposes and investigates the coordinated efforts of architectural and compilation techniques to eliminate dynamic computation redundancy of program execution on an ILP processor. An integrated compiler and architecture redundancy elimination framework has been implemented within the IMPACT compiler framework to quantify the benefits of exploiting value locality characteristics using both compiler techniques and hardware technologies.

# 1.1 Contributions

To integrate both compiler and hardware techniques in a coordinated framework to eliminate large amounts of dynamically redundant computation, four key technologies were developed.

These four technologies, discussed below, together form the contribution of this work.

#### • The Reusable Computation Region Framework (RCRF)

In order to apply compiler-directed dynamic elimination of redundant computation, the primary issue of determining the regions of a program that should be selected for reuse at run time must be addressed. Under this framework, the compiler partitions the program into reusable computation regions, which serve as the fundamental unit of execution in the integrated approach. Effective exploitation of dynamic redundancy requires that the compiler either be aware of the execution behavior of the program or estimate the program behavior. As such, two region formation approaches, profile-based and static, are developed. A quantitative analysis is performed to assess the characteristics of the reusable partitions selected using static heuristics and profile-based heuristics.

#### • Compiler-directed Computation Reuse Approach (CCR)

A new approach to computation reuse is introduced and investigated. Previous approaches to exploiting value locality have relied strictly on hardware support to detect, exploit, and adapt to program value locality opportunities. Hardware-only techniques generally illustrate limited performance improvement because run-time techniques have limited scope in exploiting dynamic redundancy between program instructions, and hardware structures cannot cost effectively detect program redundancy. In the compiler-directed computation reuse approach, the compiler divides the program into regions, which eliminates

reuse detection at run time and implements efficient reuse. The rationale for compiler-directed computation reuse is demonstrated, and the hardware framework for implementing compiler-directed reuse is presented.

### • Dynamic Computation Management System (DCMS)

An adaptive mechanism for bypassing computation regions based on the detected reuse patterns and utilization is developed. Run-time monitoring prevents regions with less likelihood of computation reuse from displacing computation regions with a greater likelihood of reuse in their use of hardware support resources. Both quantitative and analytical evaluations of the performance of reuse bypassing using the framework developed in this dissertation are presented.

#### • Compiler-based Value Optimization Framework (VOF)

Traditional compiler techniques for eliminating program redundancy rely on the detection of static redundancy, which requires the complete assertion that the computations be definitely redundant for all executions. Generally such techniques focus on removing the redundancy of computations already performed by other instances of computations in the control flow graph. In compiler-based value locality techniques, program reformulation, control flow transformation, and predicate-based value transformations are used to exploit redundancy. These techniques offer alternatives for the compiler to synthesize value-based codes rather than the traditional generation of program. The concept of each technique is explored, and the compiler infrastructure for implementing compiler-based value locality exploitations is presented.

## 1.2 Overview

This dissertation is composed of seven chapters. Chapter 2 presents an overview of the empirical redundancy characteristics of program execution and discusses related approaches to exploiting computation redundancy.

The Reusable Computation Region Framework (RCRF) is detailed in Chapter 3. Region selection provides an effective framework to investigate the exploitation of computation redundancy in an integrated compiler and architecture approach. This chapter discusses the complexities of identifying reusable computation with profiling information and with static program heuristics. Chapter 4 presents the essential hardware design and instruction set architecture extensions for the compiler-directed approach. Compiler-directed computation reuse provides an effective framework to convey static analysis of dynamic redundancy to the hardware. This chapter discusses the implications of this concept for the design of an ILP microarchitecture.

Chapter 5 investigates the application of run-time management system to the base model of compiler-directed computation reuse. Dynamic management provides an enhancement to the adaptability of the base model, and the necessary requirements of the system will be investigated. Chapter 6 examines the exploitation of recurrence behavior of computation regions using compiler-based value locality transformations. Chapter 6 provides an overview and experimental evaluation of the systematic coordination of the proposed compiler and hardware techniques to eliminate dynamic computation redundancy. A quantitative comparison is done to investigate the effectiveness of value locality exploitation in compiler-based, hardware-based, and compiler-directed approaches. Finally, in Chapter 7, conclusions and directions for future research are given.

# CHAPTER 2

### REDUNDANCY OF PROGRAM EXECUTION

Modern microprocessor architectures are increasingly designed to exploit aspects of program behavior. Since the introduction of virtual memory and cache memory systems, architectures have been exploiting spatial and temporal locality of memory access patterns to reduce the average latency of a memory reference. Similarly, the designs of branch prediction techniques focus on extracting branch predictability and correlation for improving the handling of branches within pipelined processors. Another program behavior is computation redundancy, or value locality, which describes the recurrence of a previously seen computation instance.

The importance of computation reuse is not limited to the frequent existence of computation redundancy in real-world applications. Researchers in many different scientific domains have recognized the importance of computation reuse. General techniques to code algorithms to use memoization of computation results to achieve efficient processing have been studied. Nevertheless, development of automatic computation redundancy elimination techniques has not been integrated into modern programming and computing environments. This thesis provides a initial method of establishing the automatic exploitation of computation redundancy in modern high-performance computing systems. To provide sufficient background for the techniques proposed in this thesis, this chapter outlines the general elements contributing to computation redundancy in modern computer systems. Then, an empirical analysis of the value locality occurring in general-purpose C programs evaluated using the IMPACT compiler is presented to

demonstrate the applicability and potential of this work. This chapter concludes with a brief survey of proposed approaches to exploit computation redundancy.

# 2.1 Dynamic Redundancy

The term value locality is used to describe the behavior of computations that execute with frequently recurring sets of values. Several empirical studies indicate the presence of significant amounts of value locality, or redundancy, in programs [5], [9], [10]. Traditional compiler techniques such as constant propagation, common subexpression elimination, loop invariant code removal, conditional branch elimination, and partial redundancy elimination reduce program redundancy and improve the efficiency of a program. These techniques are based on the detection of redundancy between computations of the program. As a result, current compiler optimization techniques can merely eliminate inefficiencies in a program by systematically detecting patterns within dataflow analysis of computations. Overall, compiler techniques are conservative and inflexible due to complexities associated with global program analysis [11].

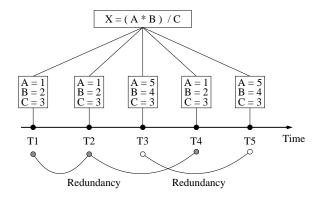

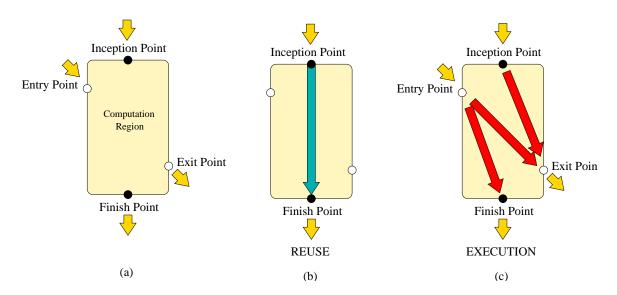

Dynamic redundancy is a form of redundancy that occurs when input operands being evaluated are identical to previously evaluated inputs in an arbitrary temporal set of executions for the same computation. Figure 2.1 illustrates the occurrence of dynamic redundancy for a given history of a particular computation. Generally, the degree of dynamic redundancy occurring is determined by recording a history of unique evaluations and calculating the number of repetitions divided by the total number of observed executions. Compiler techniques have no general mechanism for capturing dynamic redundancy and as a result, even highly optimized programs execute half of their instructions redundantly, only to recompute previously computed values. Ideally, these values should be recorded and later reused, removing unnecessary computations.

Figure 2.1 Illustration of dynamic computation redundancy.

# 2.2 Sources of Value Locality

There are several sources of computation redundancy within programs. Sodani and Sohi [5] characterized the sources by four categories. The fundamental sources are based on aspects of the input data, programming model, application domain, and the software distribution model. The work of this thesis does not specifically target any one source of redundancy; instead many elements of the proposed techniques are capable of eliminating redundancy from all of the base value locality sources. Naturally, many of these sources are subject to the particulars of an instruction set, compiler, and run-time environment being employed.

### 2.2.1 Data redundancy

Frequently, the input sets for real-world programs contain data that has little variation. Examples of this are sparse matrices, low frequency images, text files with white space, and repeated data entries in spreadsheets. Other aspects of data redundancy contributing to computation redundancy relate to the quantization and scaling of the input data at different points within a program.

#### 2.2.2 Programming models

Studies [12] indicate that redundancy may exist primarily for the same reason that partial evaluation is such an effective compile-time optimization: real-world programs, run-time environments, and operating systems incur severe performance penalties because they are general by design. Most modern programming environments are implemented to handle numerous contingencies, exceptional conditions, and erroneous inputs, all of which occur relatively rarely and contribute to redundant run-time execution.

# 2.2.3 Application domain

Various types of applications by the nature of their design include run-time constants and semi-invariants. Examples are interpreters, simulators, and graphics processing. For interpreters, the program being interpreted is a run-time constant. For simulators, circuit layout parameters, and architecture resource constraints are examples of run-time invariants. Finally, for graphics processing, the scene and viewing parameters are semi-invariant.

In addition to the methods of programming a particular application, each application domain can be characterized by a degree of recurrence for certain overlapping subtasks within its implementation. Program coding recurrence of this form has been studied in its relation to the principles of dynamic programming [13]. Dynamic programming, similar to divide-and-conquer methodologies, solves problems by combining solutions to subproblems. However divide-and-conquer algorithms partition problems into independent subproblems, solve the subproblems recursively, and combine each solution to solve the original problem. In contrast, a dynamic-programming algorithm solves every subproblem exactly once and then saves the answer in an effort to avoid the work of recomputing the answer every time the identical subproblem

is encountered. Whenever a problem exhibits overlapping subproblems, it meets a primary requirement of being solvable with a dynamic-programming algorithm. As such, since many applications created in modern programs exhibit repetition of subproblems, there exist significant amounts of redundant computation and a tremendous opportunity to exploit the principles of dynamic programming of the implicit but uncoded underlying algorithm.

Another aspect of application domains that contributes to dynamic redundancy is the different behaviors observed during execution. Virtually all programs go through a series of stages and each application domain can be described by how redundancy exists when the working set changes, either for the code or for the data, and sometimes for both. Generally an application may have different modes which operate on the data set in different ways and for different periods of time.

#### 2.2.4 Software distribution model

Although current trends in compiler technology help reduce the amount of redundancy within programs, even code that is aggressively optimized by modern, state-of-the-art compilers exhibits redundancy. In short, substantial barriers to compiler optimization occur due to the limited scope of program analysis and optimization. The compiler must often be conservative and the result is code that includes large amounts of redundant computation. For instance, when disambiguating stores and potentially aliasing loads, a compiler must frequently generate redundant loads to resolve a potential alias. Overall, enhancing the level of program analysis appears to be a fundamental theme in overcoming the barriers to removing redundant instruction execution with compiler and hardware techniques.

Other aspects of the high performance computing market add to the occurrence of redundancy, the most dominant being a trend in software distribution. Proliferation of ubiquitous computing and interchangeable software is driving the use of Dynamically Linked Libraries (DLLs), downloadable updates, and downloadable net applications. Such models of distribution act as fundamental barriers to traditional compilation by eliminating some availability of program analysis and decreasing the ability estimate program behavior. The distribution methods increase the potential of the underlying processor executing invariant and semi-invariant codes. Ultimately in these models, performance is sacrificed for maintainability.

Related to software distribution are the inherent software portability aspects such as procedure calling conventions, stack frame orientation, and caller/callee register assignment. These items provide standardized software portability features but frequently sacrifice overall performance by contributing to program redundancy [5].

# 2.3 Value Locality Characteristics in Programs

There are several important metrics that can be used to describe the inherent value locality of a program. Value locality characteristics are important as they can determine which optimization technique can most effectively be applied to eliminate the redundant execution. For compiler optimizations, the invariance of a variable, the most frequent values of the variables, or the frequent set of values for a variable over the lifetime of the program are all important execution characteristics. In this section, a straightforward approach to value profiling is discussed. The study concentrates on instruction-level profiling to motivate the observed redundancy occurring in large regions of program execution.

#### 2.3.1 Value profiling

Value profiling [2] can be used to automatically guide compilation and optimization. To determine code regions that have variables with semi-invariant or recurrent behavior, three types of information are important: (i) how an instruction's result varies over the lifetime of the program, (ii) the top N results values for an instruction, and (iii) the reuse history of instruction execution.

The invariance of an instruction's resulting value can be calculated in many different ways. The  $Most\ Recent\ Value-M\ (MRV-M)$  metric, defined by Calder et al., tracks the number of times an instruction's destination register was assigned a value that was one of the most recent M values. Where M is the history depth of the most recent unique values executed and defines the value profiling environment in which an instruction's invariance is being studied. The Invariance-X of an instruction-level locality characteristic indicates the percentage of execution time that the top X values occurred during profiling. The MRV characteristic differs from the invariance because it does not have state associated with each value indicating the execution occurrence.

The value profiling information required for determining exploitable semi-invariant code region behavior also requires the repetition of instruction computation instances. A history depth of unique instances of register source operands encountered during an instruction's execution can be used to calculate the overall redundancy of arithmetic operations in the program execution. Similarly, the repetition of values in the memory state can be tracked by maintaining the history of accesses for each memory instruction and a database of all accesses to memory.

## 2.3.2 Reuse Profiling System (RPS)

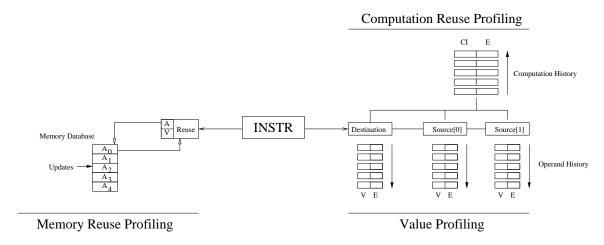

Although value profiling provides insight about the values occurring during execution, the nature of estimating a repeatable sequence requires further collection of the run-time behavior of a program. As such, the Reuse Profiling System (RPS) was developed for this thesis. Figure 2.2 shows a diagram of the information maintained by the profiling infrastructure developed in this thesis. The foundation of the reuse profiling infrastructure is the value profiling of source and destination register operands. The infrastructure generally performs reuse profiling of program execution by enabling three individual profiling methodologies: value profiling, computation reuse profiling, and memory reuse profiling. In addition, region reuse profiling can be enabling by annotating regions within code prior to profiling. Region reuse profiling determines the value, computation reuse, and memory reuse execution behavior for a region of code rather than a single instruction.

The value profiler keeps a topN value (TNV) table for each register operand. The TNV table records (V-value, E-execution) pairs for each entry with a least frequently used (LFU) replacement policy. When inserting a value into the table, existing entries are incremented. If a value is not found, the least frequently used entry is replaced. A least recently used (LRU) value replacement policy does not account for the execution occurrence of a particular value. A modified LFU policy with fixed and temporary entries is used. The temporary entries are used to contain the most recent unrecorded values and are periodically cleared to allow new entries to be collected.

To determine the repetition of computation execution, the computation reuse profiler records instances of all the source operand values of a profiled instruction within a history buffer with N entries. The entries maintain (CI-computation instance, E-execution) pairs with an LRU

Figure 2.2 Reuse profiling: value, computation reuse, and memory reuse profiling.

replacement policy. When accounting for matching computation instances, the specific values of the source operands are not recorded for final determination. Instead, only the reuse statistics observed within the computation history are maintained. In addition to the history buffer, an additional computation instance entry records the last computation entry set. This entry accounts for redundant computation that matches identically with the very last computation execution, allowing value locality that occurs in streaks or phases to be detected. Finally, to determine the activity of the history buffer, for every period of 1,000 computation instances, the number of buffer entries attributing more than 5% of the observed execution instances is recorded. This measure indicates whether a dominant number of computation instances exists for a computation instruction.

Conceptually, the memory reuse profiling approach is based on an address-based hash table system that records a database of references for each accessed datum. The memory addresses of load and store operations in a profiled program are extracted and used as the hash keys for a single global hash table. At the same time, information is maintained locally for the instruction references memory. The local information consists of A-address, V-value of data, and the Reuse

time. The addresses of the hash table entries correspond to specific data items, such as variables or array elements, in the executing program. Since the goal of memory profiling is to associate conflicts between load and store operations, it is necessary for each hash entry to maintain the unique ID for the last store operation that modified the respective program address. When load operations execute, their memory addresses access the hash table and find the respective hash entry. This entry contains the store ID of the last conflicting store operation, and is used to construct a conflict between the load and store operations. Conflicts between operations are maintained in the local instruction structure and are updated for each occurring conflict. Previous work [14] developed a similar address hash structure for evaluating data dependences to direct data speculative optimization and scheduling algorithms.

The region reuse profiling can be intuitively described as emulation of a designated region of code as a single instruction. Live-in source register values, computations instances, and memory reuse can be collected for the annotated region. Region annotations can be obtained using profile-guided techniques or static analysis. The value profiler can designate a trace of instructions with high individual instruction reuse for region reuse profiling. Further description of the computation region formation process is given in the next chapter.

Static analysis derives regions consisting of simple loops, capturing potential redundancy for linked-list traversals and array scans. When statically annotating regions, a defined set of control blocks composes a region. Formally, a function can be represented by a control flow graph G(N, E), where N is the set of basic blocks in the function and E is the set of all control flow edges between blocks in N. The graph can be divided further to represent the individual instructions that define basic blocks by the graph GI(I, E), where I is the set of all instructions in the function and E is the set of all control edges. The difference between graphs G and GI is

that GI uses implied edges between the sequential instructions of a basic block N. The graph GI is trivially created from G by designating every instruction as a basic block.

For each reuse region, profiling instrumentation is inserted to verify reuse at the start of each region. However, this process involves executing the region to initiate the path of executions and check the register values and memory database. Thus in validating region reuse, both the memory region reuse rate and rate that an individual load causes the invalidation of a loop execution can be determined. During stateless region detection, loops representing memory regions are annotated for the profiling system to gather the memory region reuse information.

#### 2.3.2.1 Evaluation methodology

The benchmarks used in the experiments of this evaluation and the entire thesis consist of 13 nonnumeric programs: two of the SPECINT92 benchmarks, 008.espresso, 072.sc; seven of the SPECINT95 benchmarks, 099.go, 124.m88ksim, 126.gcc, 129.compress, 130.li, 132.ijpeg, 147.vortex; two Unix utilities, lex, yacc; and two media utilities, mpeg2, pgp. These benchmarks were selected to represent the characteristics of a wide range of engineering, communication, and desktop applications. Table 2.1 describes the functionality of the applications studied and is cited to develop comparisons between the program behavior and reuse characteristics of the different application types.

To throughly study the value locality characteristics of programs, profile information was collected for two series of inputs, training and reference. Generally, a training input is selected to indicate the program elements that are most characteristic of the application behavior. The data input sets used for all experimental evaluations in this thesis, and the respective number of dynamic instructions (in millions) executed for each data set are described in Table 2.2.

Table 2.1

Benchmarks descriptions.

| Benchmark    | Description                                             |

|--------------|---------------------------------------------------------|

| 008.espresso | Optimization program for Programmable Logic Arrays.     |

| 072.sc       | A mathematical spreadsheet program.                     |

| 099.go       | An internationally ranked go-playing program.           |

| 124.m88ksim  | A chip simulator for the Motorola 88100 microprocessor. |

| 126.gcc      | The GNU C compiler, version 2.5.3.                      |

| 129.compress | An in-memory compression application.                   |

| 130.li       | Xlisp interpreter.                                      |

| 132.ijpeg    | Image compression/decompression on in-memory images.    |

| 147.vortex   | An object oriented database.                            |

| lex          | A lexical analyzer generator.                           |

| yacc         | A parser generator for context free grammars.           |

| mpeg2        | Standard for digital video transmission.                |

| pgp          | 128-bit digital signature cryptography.                 |

${\bf Table~2.2}~~{\rm Data~input~sets~used~in~evaluating~locality}.$

|              | Data Input Set 1 : Training |              | Data Input Set 2 : Reference |              |  |

|--------------|-----------------------------|--------------|------------------------------|--------------|--|

| Benchmark    | Name                        | Exec M-instr | Name                         | Exec M-instr |  |

| 008.espresso | bca.in                      | 307.8        | cps.in                       | 369.7        |  |

| 072.sc       | loada1                      | 86.8         | loada2                       | 64.7         |  |

| 099.go       | 2stone9.in                  | 292.9        | 5stone21.in                  | 11122.6      |  |

| 124.m88ksim  | dcrand.big                  | 67.8         | dhry.big                     | 46550.2      |  |

| 126.gcc      | amptjp.i                    | 855.0        | varasm.i                     | 16301.2      |  |

| 129.compress | test.in                     | 23.8         | bigtest.in                   | 27835.4      |  |

| 130.li       | train.lsp                   | 114.3        | reference                    | 35611.2      |  |

| 132.ijpeg    | vigo.ppm                    | 1072.3       | penguin.ppm                  | 22000.3      |  |

| 147.vortex   | persons.250                 | 1082.1       | persons.1k                   | 32806.5      |  |

| lex          | lex.l                       | 37.8         | awk.lx.l                     | 35.5         |  |

| yacc         | c-parse.y                   | 33.8         | awk.g.y                      | 15.0         |  |

| mpeg2        | mei16v2.m2v                 | 94.7         | reference                    | 974.2        |  |

| pgp          | pgptest.plain               | 43.8         | pgptext.pgp                  | 54.4         |  |

The amount of time for a reuse profile to be generated plays an important role in the integration of an architecture mechanism or compiler technique into a traditional high-performance computing system. Table 2.3 shows the time of the value profiling infrastructure. The second column indicates the amount of user and system time spent performing control profiling a program's execution. The third column indicates both the time spent performing value profiling and the factor of evaluation time increase relative to the time of control profiling. The fourth column shows the both the time spent performing reuse value profiling with memory reuse profiling and the factor of evaluation increase relative to the time of control profiling.

The amount of time spent in developing, verifying, and releasing software will vary depending on the level of the potential benefits achievable. Although the times for reuse profiling in Table 2.3 indicate considerable expense to the program development time, the estimated benefits in program execution significantly outweigh the costs. Methods of reducing value profiling time by taking advantage of value locality properties have been considered [2].

**Table 2.3** Control profiling, value profiling, and reuse profiling times.

|              | Control Profiling (CP) | Value Profiling (VP) |         | Reuse Profiling (RP) |         |

|--------------|------------------------|----------------------|---------|----------------------|---------|

| Benchmark    | Time (s)               | Time (s)             | (VP/CP) | Time (s)             | (RP/CP) |

| 008.espresso | 156.5                  | 231.4                | 1.47    | 295.6                | 1.88    |

| 072.sc       | 78.5                   | 114.6                | 1.46    | 120.9                | 1.54    |

| 099.go       | 202.2                  | 306.4                | 1.51    | 280.8                | 1.38    |

| 124.m88ksim  | 134.5                  | 184.9                | 1.37    | 172.5                | 1.28    |

| 126.gcc      | 944.4                  | 1156.7               | 1.22    | 1395.4               | 1.47    |

| 129.compress | 29.2                   | 72.3                 | 2.47    | 181.9                | 6.23    |

| 130.li       | 50.7                   | 89.0                 | 1.75    | 165.8                | 3.26    |

| 132.ijpeg    | 152.0                  | 193.9                | 1.27    | 319.8                | 2.10    |

| 147.vortex   | 326.0                  | 378.9                | 1.16    | 801.9                | 2.46    |

| lex          | 22.1                   | 66.7                 | 3.01    | 163.4                | 7.39    |

| yacc         | 18.8                   | 47.4                 | 2.51    | 158.2                | 8.41    |

| mpeg2        | 28.7                   | 111.7                | 3.89    | 323.0                | 11.25   |

| pgp          | 68.8                   | 167.1                | 2.42    | 204.6                | 2.97    |

#### 2.3.3 Invariance

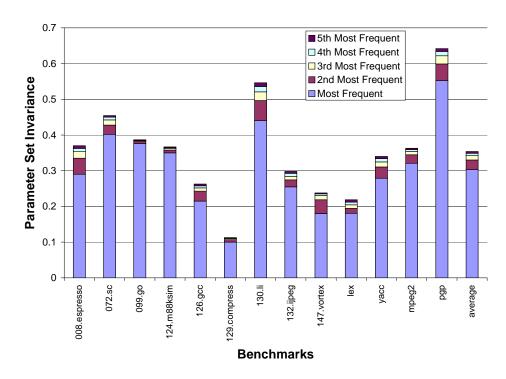

This section examines the invariance of values for instruction types and procedure parameters. For the results, a TNV table size of 10 values was used for profiling. When an instruction or parameter is said to have an *Invariance-M* of X, this is calculated by taking the number of times the top M values occurred during profiling, as found in the TNV table after profiling, and dividing the number of times the instruction was executed. Table 2.4 shows the percentage of execution matching the *Inv-10* invariance characteristic and the percentage of dynamic execution frequency for different individual instruction types.

Table 2.4 includes instruction categories: integer loads (I-Load), integer stores (I-Store), integer arithmetic (I-Arith), integer multiplication (I-Mul), integer logical (I-Logic), floating-point loads (F-Load), floating-point arithmetic (F-Arith), and all other floating-point operations (F-Op). The results show that integer invariance is a common behavior in the programs evaluated. For all programs, the integer loads and the integer arithmetic instructions consistently have a high degree of invariance and account for the major portion of program execution. The floating-point instructions, although having a high degree of invariance, are not frequently executed. These results indicate that dynamic computation redundancy is concentrated in integer operations and motivates the development of a mechanism to eliminate redundant code execution in nonnumeric programs.

Many compiler optimizations exploit the invariance commonly exhibited by variables during program execution. Load instructions represent the mechanism by which variables that reside in the memory system are transferred to the processor. Due to the growing disparity between processor and memory performance, load instructions occasionally incur increasingly long latencies. These latencies delay the execution of dependent instructions, which can significantly

**Table 2.4** Percentage execution invariance and percentage dynamic program execution for individual instruction types.

| Benchmark    | I-Load  | I-Store | I-Arith  | I-Mul  | I-Logic | F-Load  | F-Arith | F-Op    |

|--------------|---------|---------|----------|--------|---------|---------|---------|---------|

| 008.espresso | 55 (27) | 73 (14) | 48 (32)  | 28 (0) | 57 (0)  | 80 (0)  | 50 (0)  | 98 (0)  |

| 072.sc       | 42 (26) | 48 (14) | 49 (26)  | 34 (0) | 63 (6)  | 78 (0)  | 0 (0)   | 50 (0)  |

| 099.go       | 35 (32) | 70 (15) | 30 (35)  | 20 (0) | 45 (0)  | 100 (0) | 0 (0)   | 97(0)   |

| 124.m88ksim  | 75 (22) | 76 (12) | 65 (30)  | 35 (0) | 69 (0)  | 60 (0)  | 100 (0) | 100 (0) |

| 126.gcc      | 43 (21) | 36 (12) | 43 (26)  | 39(0)  | 56 (9)  | 67(0)   | 0 (0)   | 0 (0)   |

| 129.compress | 42 (22) | 14 (6)  | 14 (34)  | 10 (0) | 16 (11) | 0 (0)   | 0 (0)   | 0 (0)   |

| 130.li       | 40 (30) | 59 (15) | 55 (25)  | 30 (0) | 70 (3)  | 90 (1)  | 0 (0)   | 100 (0) |

| 132.ijpeg    | 25 (20) | 22 (5)  | 22 ( 35) | 35 (3) | 18 (22) | 75 (0)  | 0 (0)   | 90 (0)  |

| 147.vortex   | 55 (27) | 60 (12) | 60 (30)  | 10 (0) | 35 (5)  | 79 (0)  | 0 (0)   | 0 (0)   |

| lex          | 38 (27) | 42 (10) | 22 (34)  | 15 (0) | 30 (6)  | 50 (0)  | 0 (0)   | 48 (0)  |

| yacc         | 52 (25) | 50 (11) | 45 (30)  | 25 (0) | 52 (5)  | 50 (0)  | 33 (0)  | 67(0)   |

| mpeg2        | 32 (19) | 40 (9)  | 38 (18)  | 13 (0) | 35 (3)  | 56 (0)  | 0 (0)   | 33 (0)  |

| pgp          | 55 (22) | 58 (10) | 51 (31)  | 27 (1) | 51 (9)  | 65 (1)  | 45 (0)  | 82 (2)  |

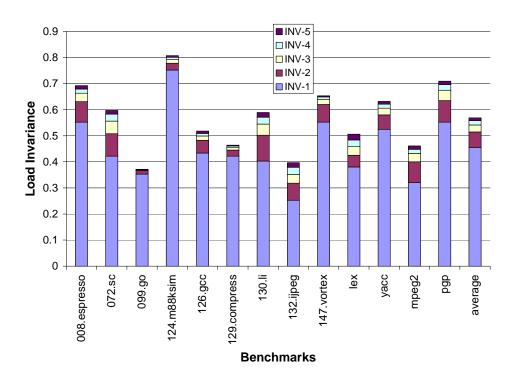

affect system performance. For these reasons, the invariance of load values is an important characteristic to exploit in both compiler-based and hardware-based techniques. In order to look at the overall invariance for an instruction, several degrees of invariance were examined. For Inv-1, the frequency count of the most frequently occurring value in the TNV table is divided by the number of instruction executions. For Inv-X, the occurrences of the top X values in the final TNV table are added together and divided by the number of instruction executions to generate the percentage invariant execution. Figure 2.3 shows the invariance for integer loads for the top five values. The difference in Inv-1 and Inv-5 invariance of load instructions for most programs is about 10% of the load execution. The results indicate that benchmarks 124.m88ksim, 147.vortex, and pgp have an Inv-5 invariance that accounts for upwards of 65% of the overall instruction execution. Overall the high percentage of load execution accounted by a relatively small number of values indicates that potentially recording a limited set of values for each instruction can amount to significant performance improvement.

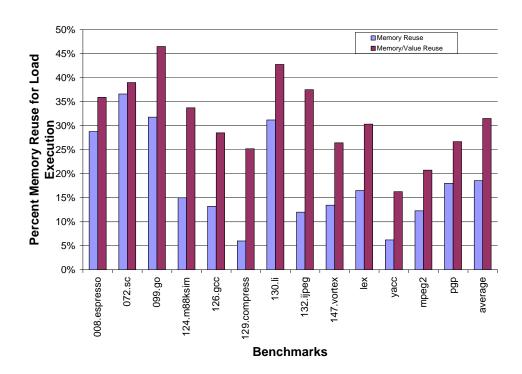

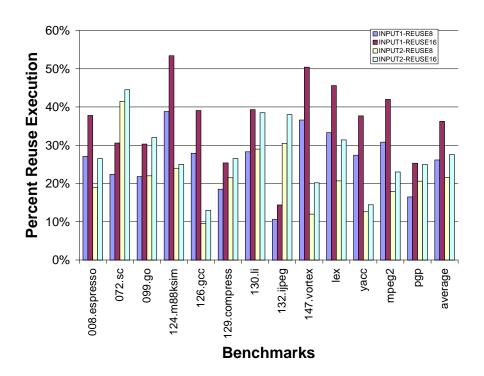

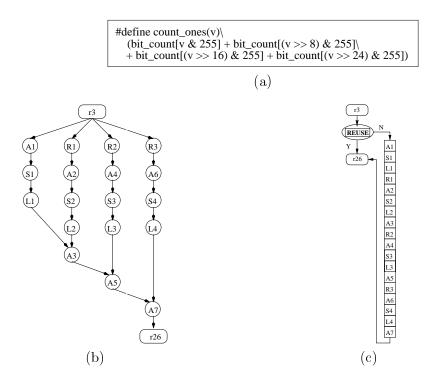

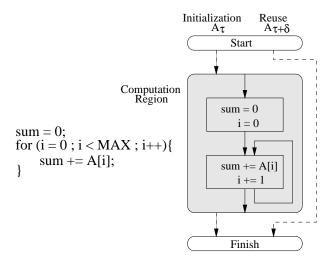

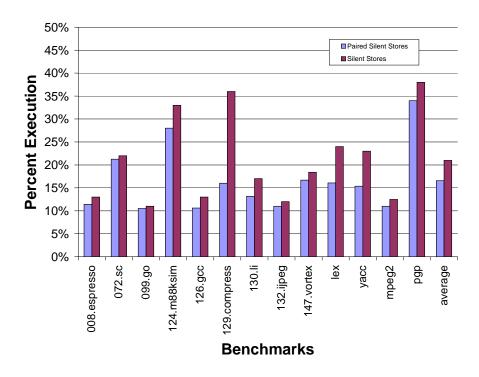

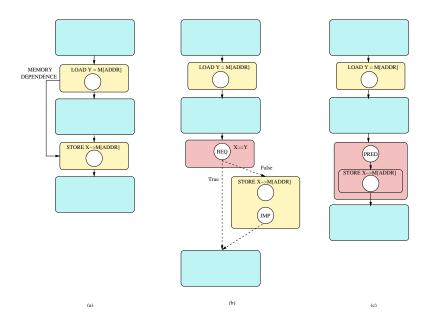

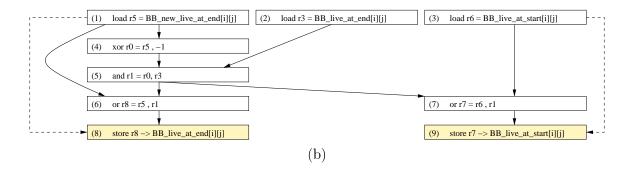

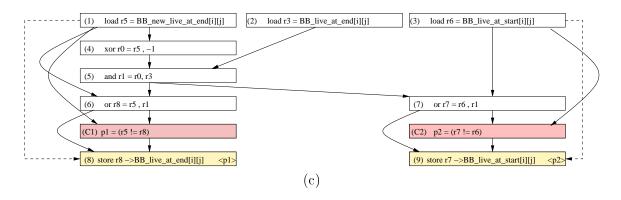

Figure 2.3 Evaluated load invariance of top five values.